www.ti.com

Analog Mux Control Registers

587

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

I/O Pads and Pin Multiplexing

16.5 Analog Mux Control Registers

The internal analog switches and muxes for the analog-digital pins must be configured correctly for proper

device operation, and to avoid damaging the device. When a digital I/O pad cell is routed correctly to the

package pin using these analog switches, the functional pin-mux must be configured to select the desired

digital interface pin to be brought out of the chip. In other words, these pins require two levels of mux

configuration.

The CC32xx ROM firmware automatically configures the analog switches and muxes for pins 29, 30, 45,

50, 52, and 53 as part of the chip initialization sequence, which occurs after exiting from global reset

(nRESET pulled high from low), exiting from hibernate mode, or exiting from LPDS mode. The application

code can directly use these six pins like any other digital pins.

The ADC inputs, on the other hand, can tolerate levels only up to 1.8 V. Application code must therefore

enable the analog switches for one or more ADC inputs, after ensuring there are no other internal or

external drivers on the pins that can go above 1.8 V. The output buffer, pullup, and pulldown should be

disabled while ADC inputs are connected to the pins, to avoid damaging the device.

Table 16-4 describes the register bits used to configure the internal analog switches and muxes for the

analog-digital pins.

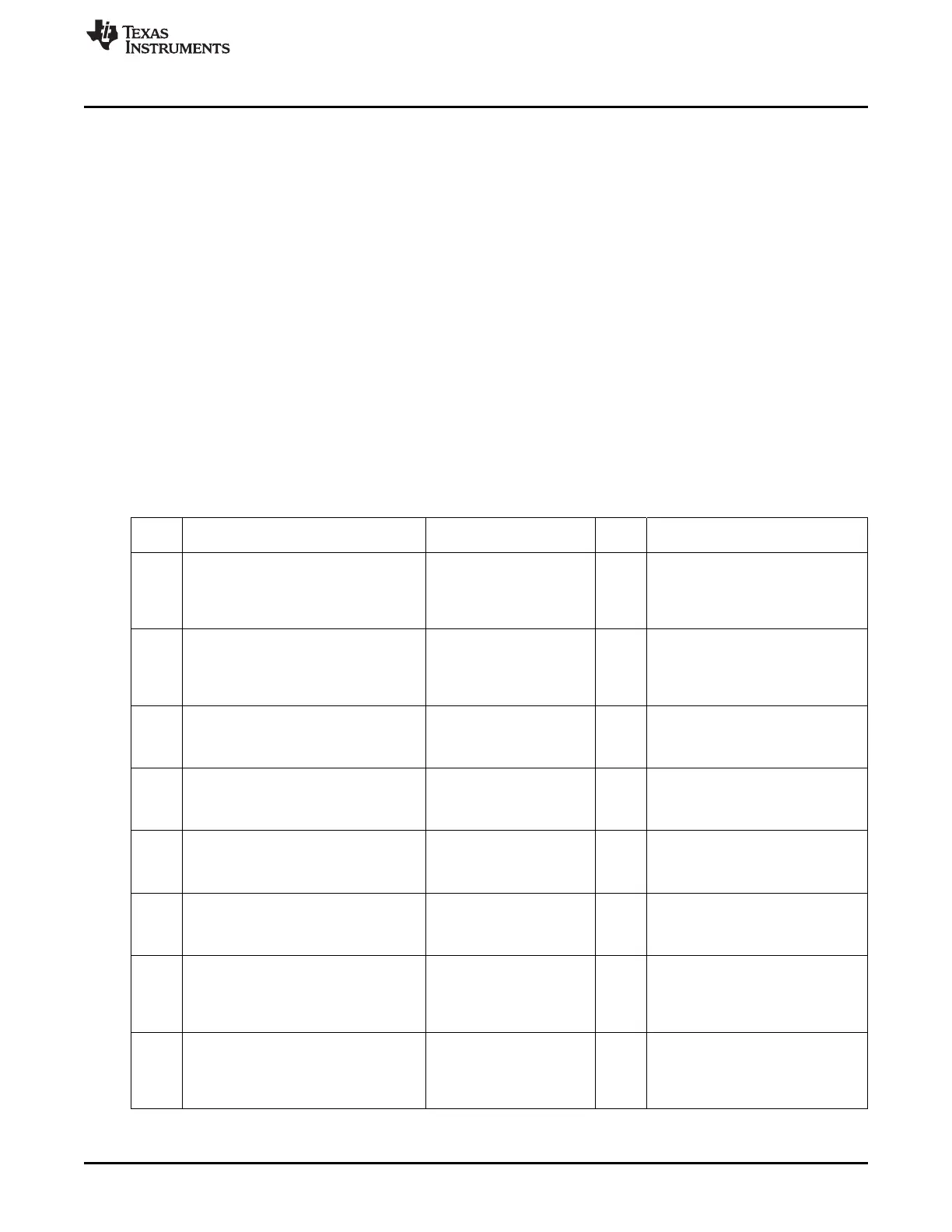

Table 16-5 describes the default behavior and configurations required for some of the analog-digital

multiplexed I/Os used for digital signals.

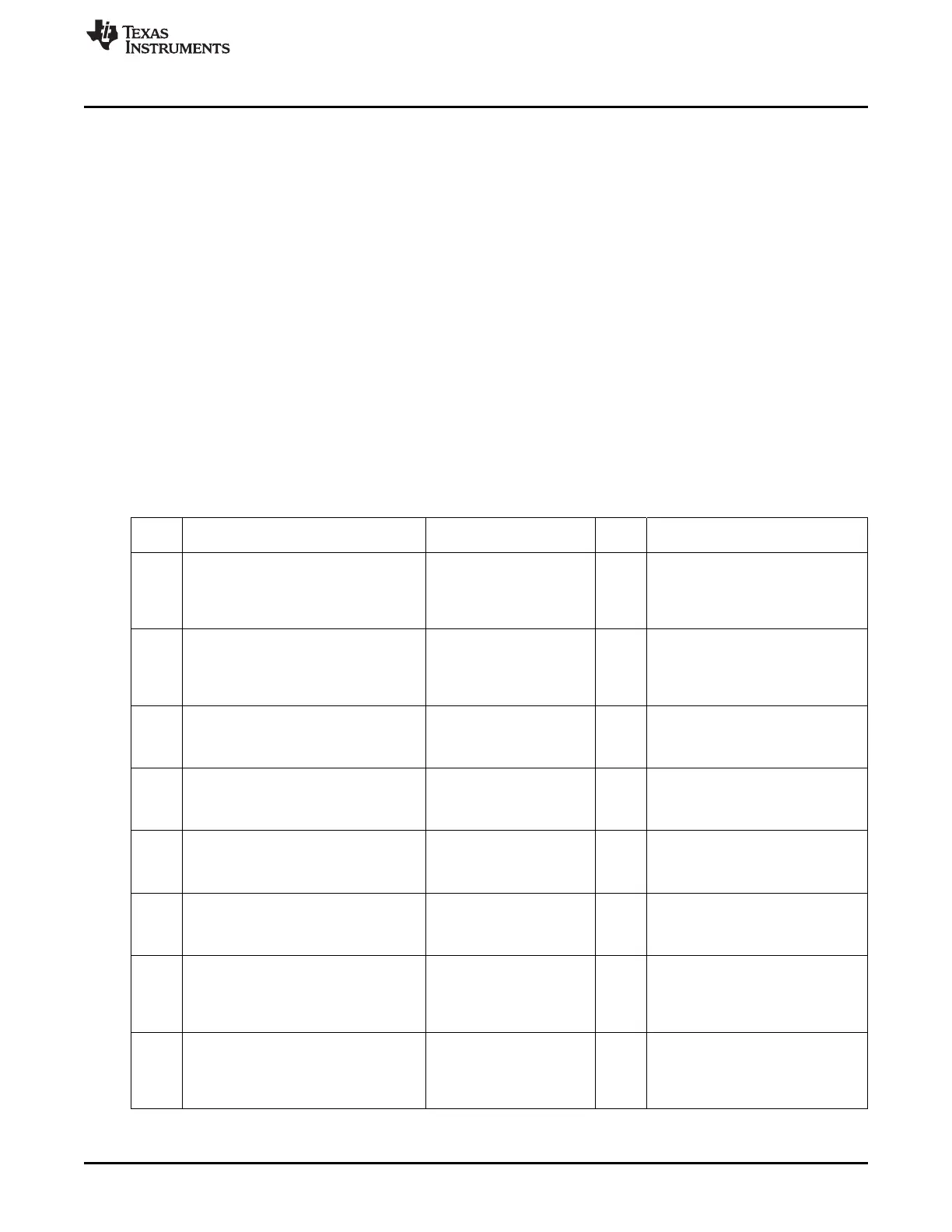

Table 16-4. Analog Mux Control Registers and Bits

Pin Analog Mux Control Register and Bit Write Values

Reset

Value

Notes

29

Register: MEM_TOPMUXCTRL_IFORCE

Address: 0x4402 E178

Bit [0]

0: GPIO26 Digital path not

enabled

1: GPIO26 Digital path

enabled

0

ANTSEL1 (GPIO26)

Device init firmware enables the

digital path.

No user configuration required for the

analog mux.

30

Register: MEM_TOPMUXCTRL_IFORCE

Address: 0x4402 E178

Bit [1]

0: GPIO27 Digital path not

enabled

1: GPIO27 Digital path

enabled

0

ANTSEL2 (GPIO27)

Device init firmware enables the

digital path.

No user configuration required for the

analog mux.

45

Register: MEM_HIB_CONFIG

Address: 0x4402 F850

Bit [19]

0: Digital path not enabled

1: Digital path enabled

0

Device init firmware enables the

digital path.

No user configuration required for the

analog mux.

50

Register: MEM_HIB_CONFIG

Address: 0x4402 F850

Bit [17]

0: Digital path not enabled

1: Digital path enabled

0

Device init firmware enables the

digital path.

No user configuration required for the

analog mux.

52

Register: MEM_HIB_CONFIG

Address: 0x4402 F850

Bit [16]

0: Digital path not enabled

1: Digital path enabled

0

Device init firmware enables the

digital path.

No user configuration required for the

analog mux.

53

Register: MEM_HIB_CONFIG

Address: 0x4402 F850

Bit [18]

0: Digital path not enabled

1: Digital path enabled

0

Device init firmware enables the

digital path.

No user configuration required for the

analog mux.

57

Register: ADCSPARE1

Address: 0x4402 E8B8

Bit [1]

0: ADC channel 0 path is not

enabled

1: ADC channel 0 path is

enabled

0

Digital I/O cell is always connected to

this pin, and application software

must make the digital I/O Hi-Z before

enabling analog mux, to prevent

damaging the device.

58

Register: ADCSPARE1

Address: 0x4402 E8B8

Bit [2]

0: ADC channel 1 path is not

enabled

1: ADC channel 1 path is

enabled

0

Digital I/O cell is always connected to

this pin, and application software

must make the digital I/O Hi-Z before

enabling analog mux, to prevent

damaging the device.

Loading...

Loading...