ARM® Cortex® M4

Instrumentation

Trace Macrocell

Data

Watchpoint

and Trace

CM4 Core

Instructions Data

Flash

Patch and

Breakpoint

Nested

Vectored

Interrupt

Controller

Adv. Peripheral

Bus

Bus

Matrix

Debug

Access Port

ROM

Table

Serial Wire JTAG

Debug Port

Trace

Port

Interface

Unit

Serial Wire

Output Trace

Port (SWO)

I-code bus

d-code bus

system bus

Private Peripheral Bus

(internal)

Interrupts

Sleep

Debug

Overview

www.ti.com

52

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Cortex

®

-M4 Processor

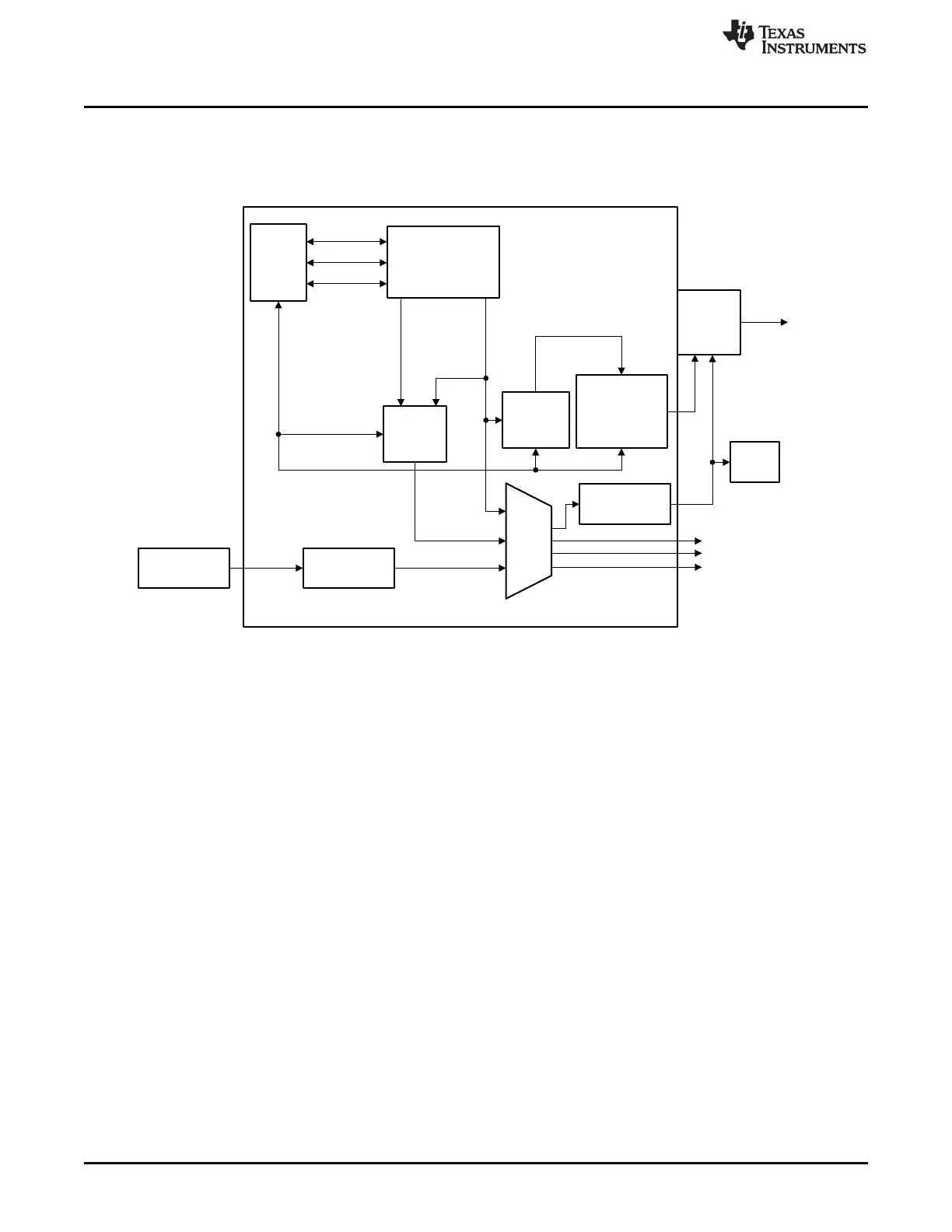

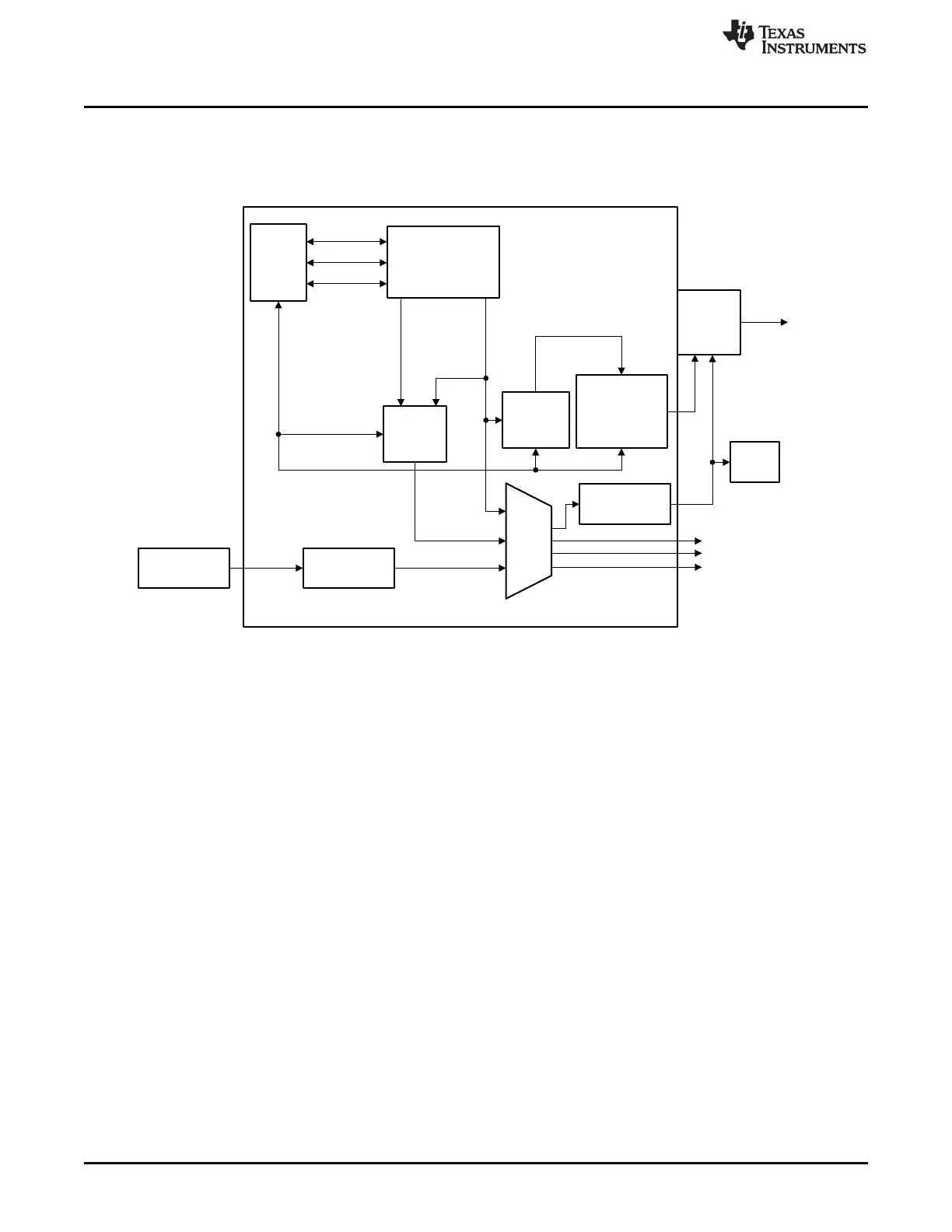

2.1.1 Block Diagram

Figure 2-1 shows the block diagram.

Figure 2-1. Application CPU Block Diagram

2.1.2 System-Level Interface

The Cortex

®

-M4 application processor in the CC32xx provides multiple interfaces using AMBA™

technology to provide high-speed, low-latency memory accesses. The core supports unaligned data

accesses and implements atomic bit manipulation that enables faster peripheral controls, system

spinlocks, and thread-safe Boolean data handling.

2.1.3 Integrated Configurable Debug

The Cortex

®

-M4 application processor implements an Arm

®

CoreSight™-compliant serial wire JTAG-

debug port (SWJ-DP) interface. The SWJ-DP interface combines the SWD and JTAG debug ports into

one module. See the Arm Debug Interface V5 Architecture Specification for details on SWJ-DP.

The 4-bit trace interface from embedded trace macrocell (ETM) is not supported in the CC32xx due to pin

limitations. Instead, the processor integrates an instrumentation trace macrocell (ITM) alongside data

watchpoints and a profiling unit. A serial-wire viewer (SWV) can export a stream of software-generated

messages (printf style debug), data trace, and profiling information through a single pin to enable simple

and cost-effective profiling of the system trace events.

The flash patch and breakpoint unit (FPB) provides up to eight hardware breakpoint comparators for

debugging. The comparators in the FPB also provide remap functions for up to eight words of program

code in the code memory region. FPB also provides code patching capability; however, as the CC32xx

application processor implements and executes from SRAM architecture, this type of patching is no longer

required.

For more information on the Cortex

®

-M4 debug capabilities, see the Arm Debug Interface V5 Architecture

Specification.

Loading...

Loading...