Camera Registers

www.ti.com

496

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Parallel Camera Interface Module

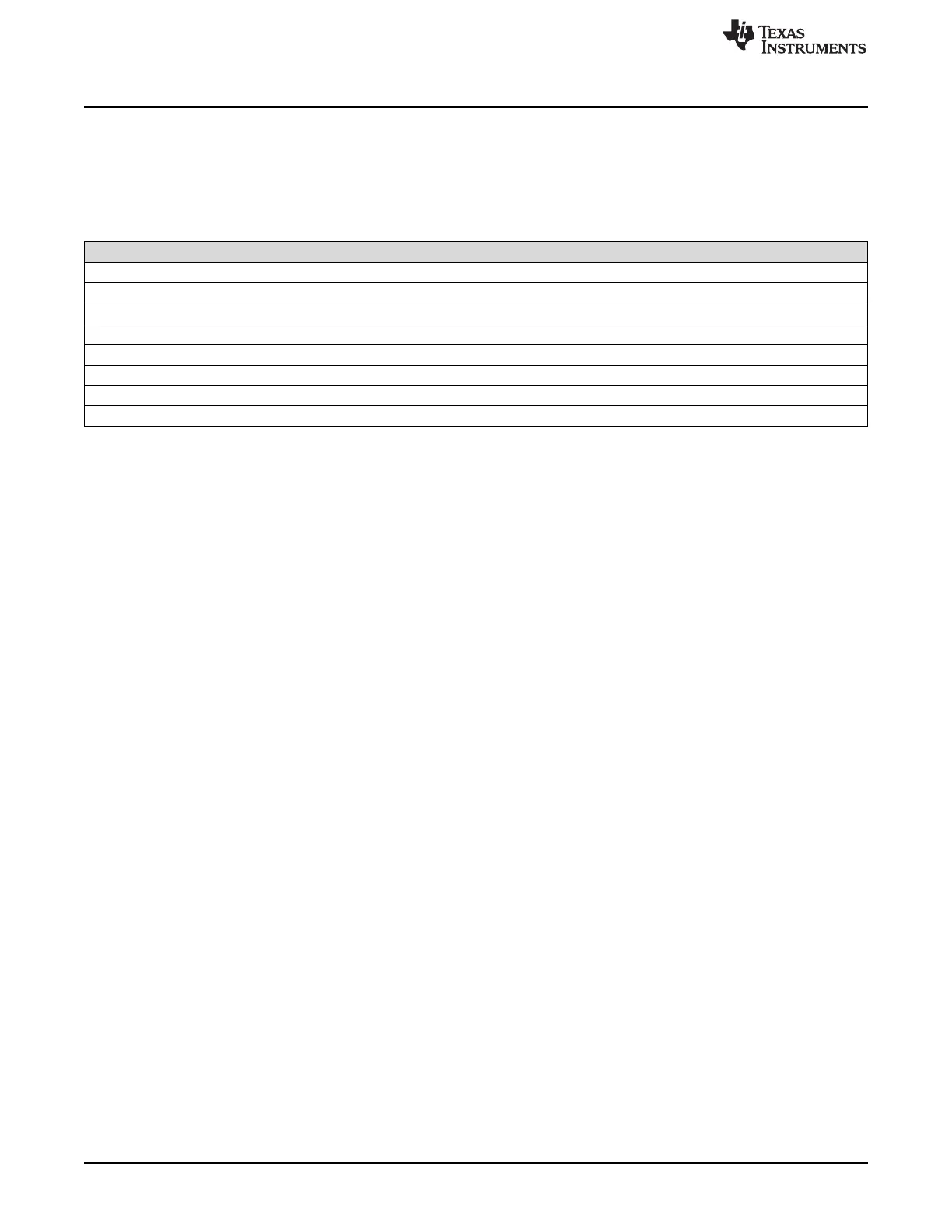

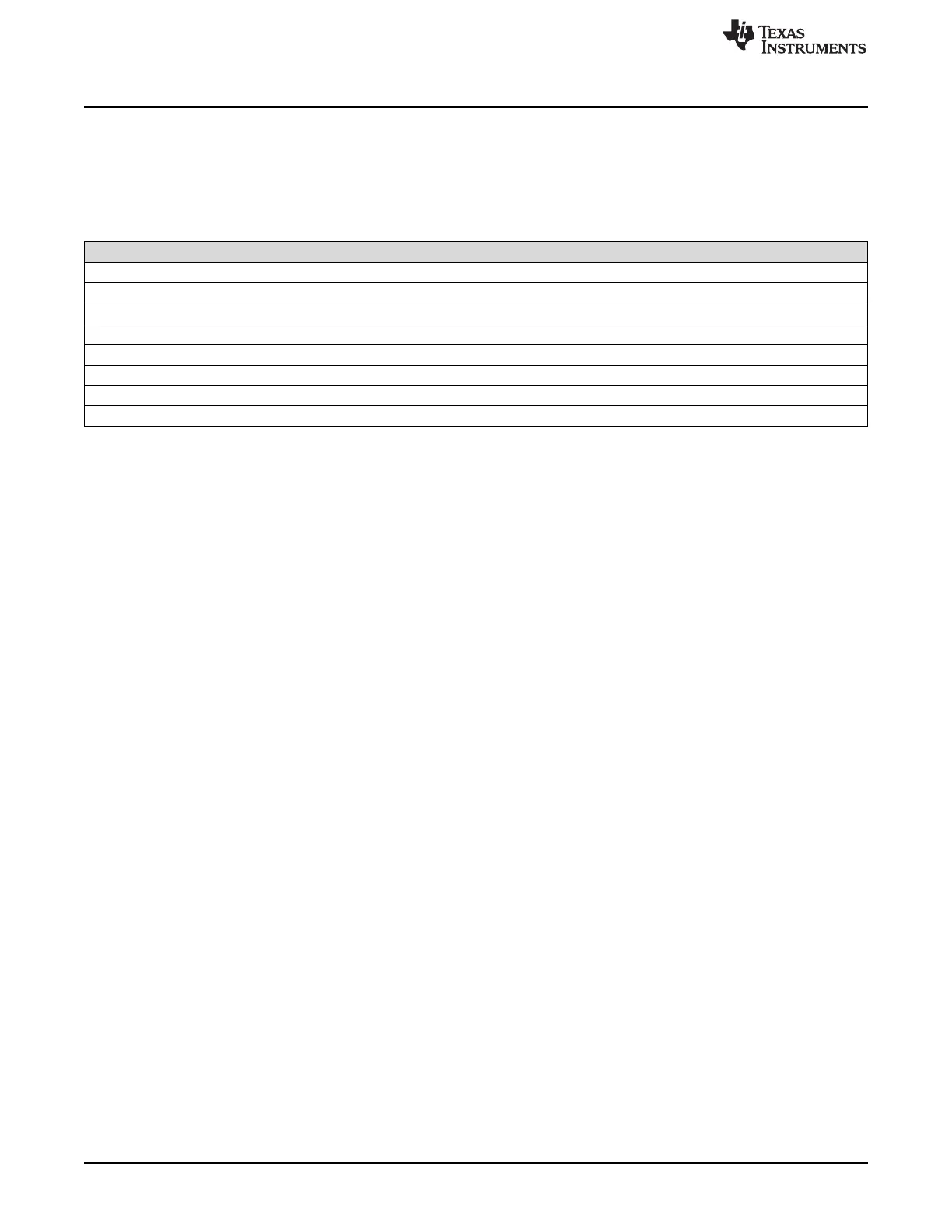

14.6 Camera Registers

Table 14-3 lists the memory-mapped Camera registers. All register offset addresses not listed in Table 14-

3 should be considered as reserved locations and the register contents should not be modified. TI

recommends using the APIs instead of directly accessing the register bits in this module.

Table 14-3. Camera Registers

Offset Acronym Register Name Section

10h CC_SYSCONFIG System Configuration Register Section 14.6.1

14h CC_SYSSTATUS System Status Register Section 14.6.2

18h CC_IRQSTATUS Interrupt Status Register Section 14.6.3

1Ch CC_IRQENABLE Interrupt Enable Register Section 14.6.4

40h CC_CTRL Control Register Section 14.6.5

44h CC_CTRL_DMA Control DMA Register Section 14.6.6

48h CC_CTRL_XCLK External Clock Control Register Section 14.6.7

4Ch to 1FCh CC_FIFODATA FIFO Data Register Section 14.6.8

Loading...

Loading...