Register Map

www.ti.com

98

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Cortex

®

-M4 Peripherals

3.3.1.13 VTABLE Register (Offset = D08h) [reset = 0h]

VTABLE is shown in Figure 3-13 and described in Table 3-16.

Return to Summary Table.

The VTABLE register indicates the offset of the vector table base address from memory address

0x0000.0000.

NOTE: This register can only be accessed from privileged mode.

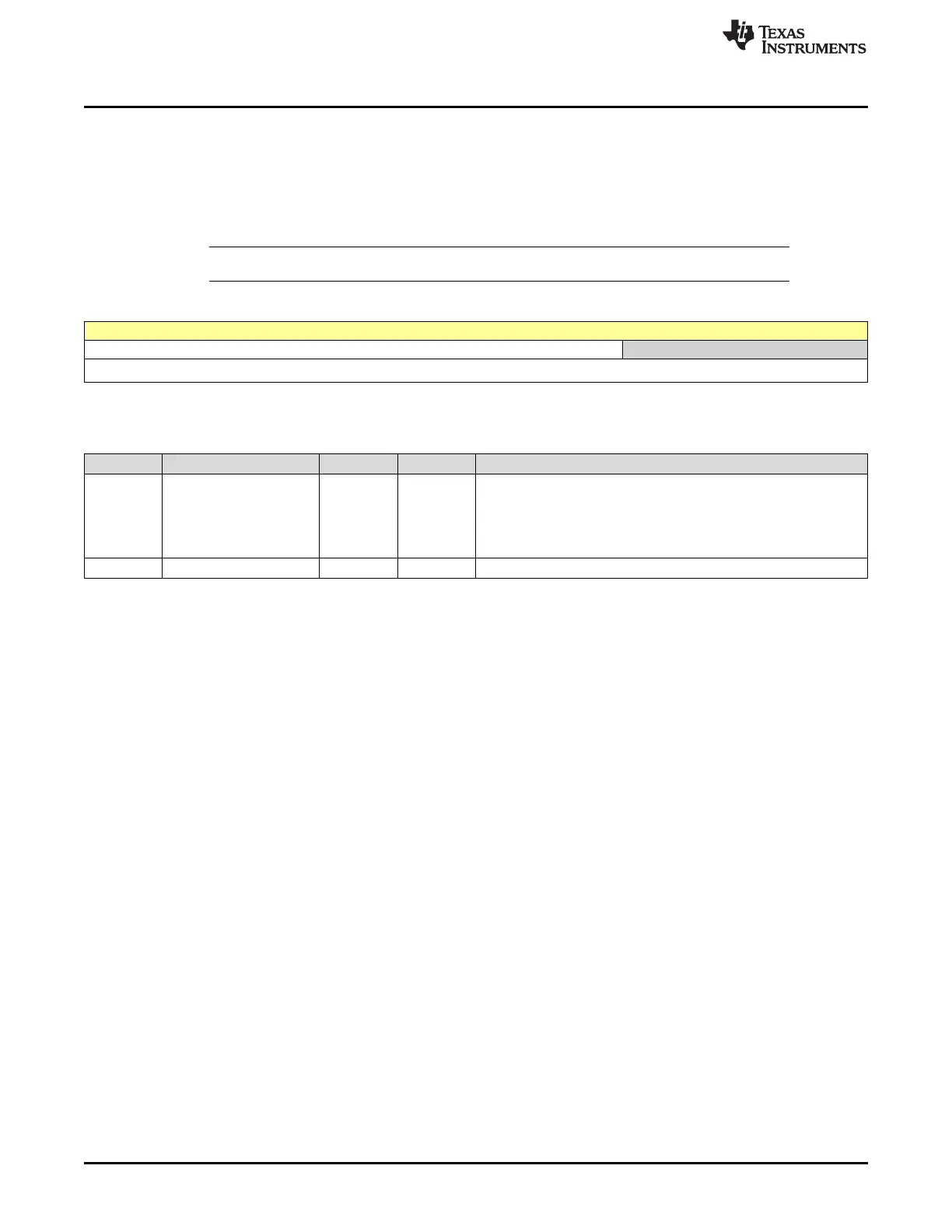

Figure 3-13. VTABLE Register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

OFFSET RESERVED

R/W-0h R-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

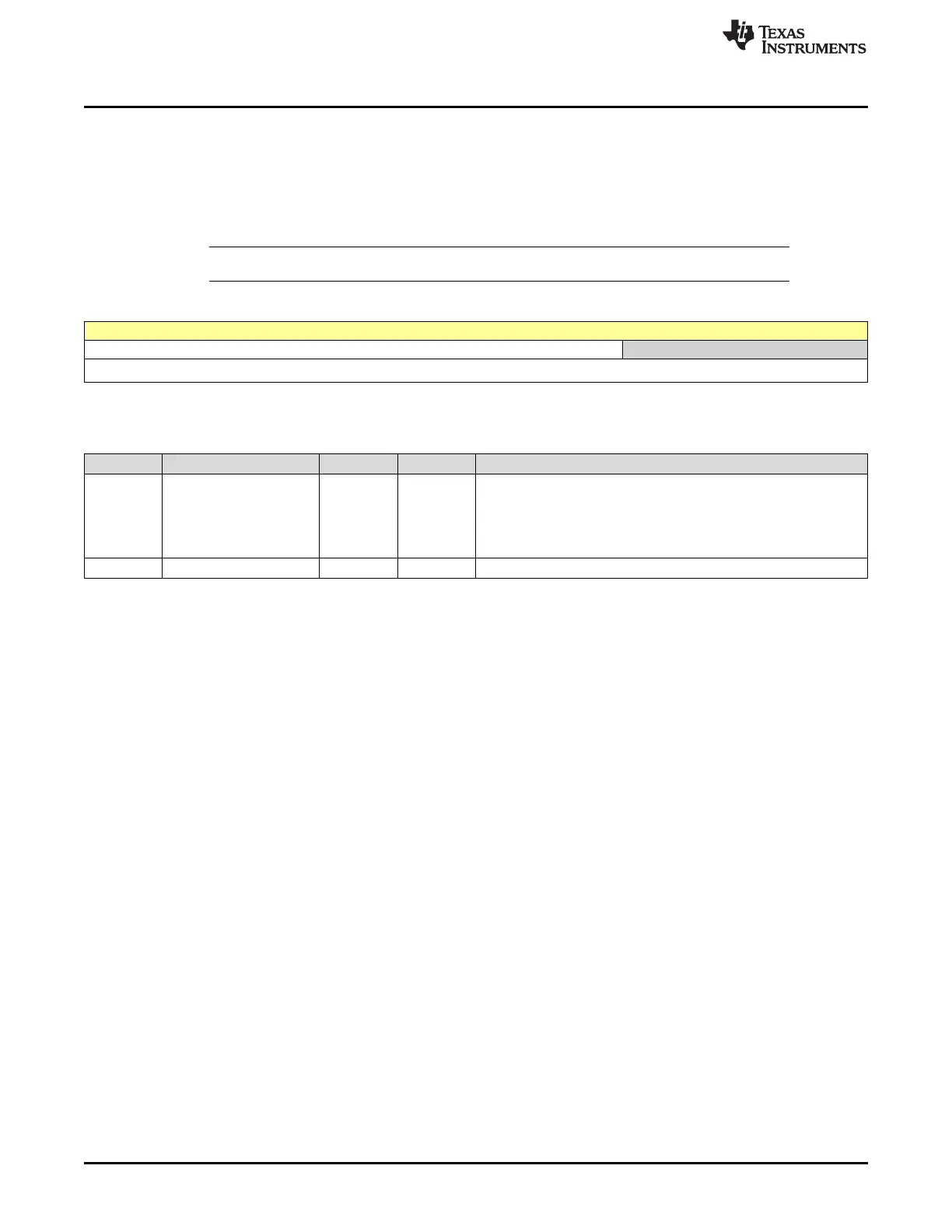

Table 3-16. VTABLE Register Field Descriptions

Bit Field Type Reset Description

31-10 OFFSET R/W 0h

Vector Table Offset

When configuring the OFFSET field, the offset must be aligned to

the number of exception entries in the vector table. Because there

are 199 interrupts, the offset must be aligned on a 1024-byte

boundary.

9-0 RESERVED R 0h

Loading...

Loading...