www.ti.com

Register Map

97

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Cortex

®

-M4 Peripherals

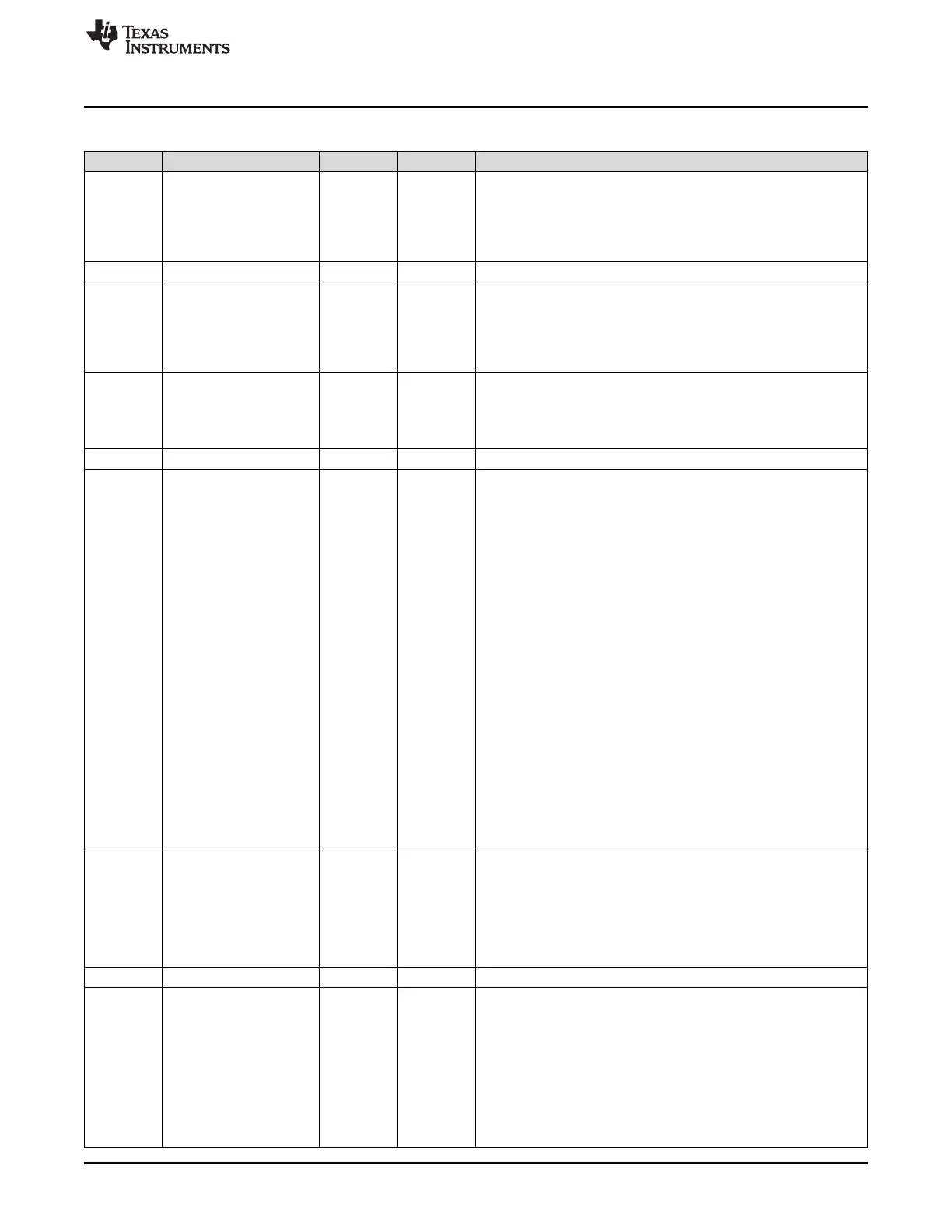

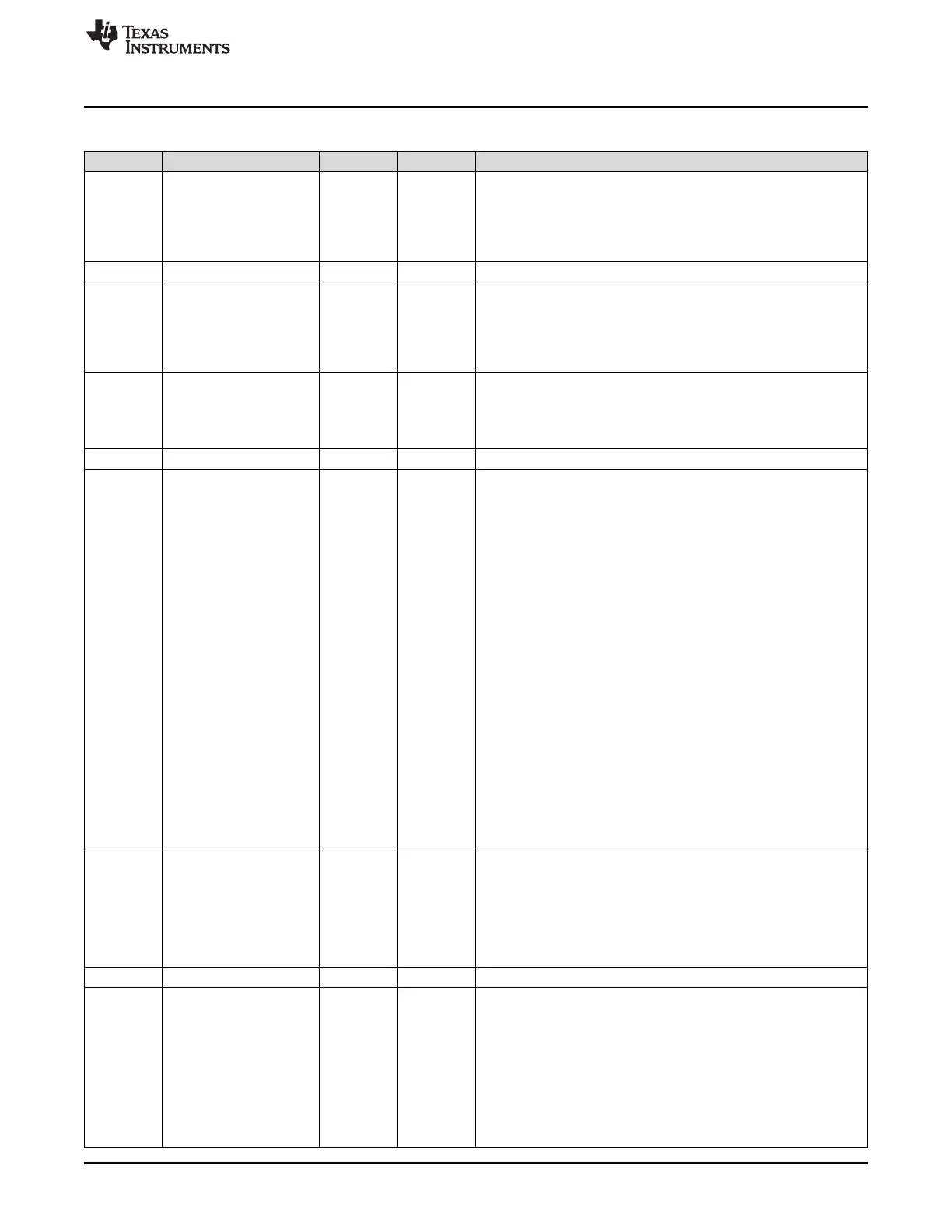

Table 3-15. INTCTRL Register Field Descriptions (continued)

Bit Field Type Reset Description

25 PENDSTCLR W 0h

SysTick Clear Pending

This bit is write only on a register read, its value is unknown.

0h = On a write, no effect.

1h = On a write, removes the pending state from the SysTick

exception.

24 RESERVED R 0h

23 ISRPRE R 0h

Debug Interrupt Handling

This bit is only meaningful in debug mode, and reads as zero when

the processor is not in debug mode.

0h = The release from halt does not take an interrupt.

1h = The release from halt takes an interrupt.

22 ISRPEND R 0h

Interrupt Pending

This bit provides status for all interrupts excluding NMI and faults.

0h = No interrupt is pending.

1h = An interrupt is pending.

21-20 RESERVED R 0h

19-12 VECPEND R 0h

Interrupt Pending Vector Number

This field contains the exception number of the highest priority

pending enabled exception. The value indicated by this field includes

the effect of the BASEPRI and FAULTMASK registers, but not any

effect of the PRIMASK register.

0h = No exceptions are pending

1h = Reserved

2h = NMI

3h = Hard fault

4h = Memory management fault

5h = Bus fault

6h = Usage fault

7h- Ah = Reserved

Bh = SVCall

Ch = Reserved for Debug

Dh = Reserved

Eh = PendSV

Fh = SysTick

10h = Interrupt Vector 0

11h = Interrupt Vector 1

...

D9h = Interrupt Vector 199

11 RETBASE R 0h

Return to Base

This bit provides status for all interrupts excluding NMI and faults.

This bit only has meaning if the processor is currently executing an

ISR (the Interrupt Program Status (IPSR) register is non-zero).

0h = There are preempted active exceptions to execute.

1h = There are no active exceptions, or the currently executing

exception is the only active exception.

10-8 RESERVED R 0h

7-0 VECACT R 0h

Interrupt Pending Vector Number

This field contains the active exception number. The exception

numbers can be found in the description for the VECPEND field. If

this field is clear, the processor is in Thread mode.

This field contains the same value as the ISRNUM field in the IPSR

register.

Subtract 16 from this value to obtain the IRQ number required to

index into the Interrupt Set Enable (ENn), Interrupt Clear Enable

(DISn), Interrupt Set Pending (PENDn), Interrupt Clear Pending

(UNPENDn), and Interrupt Priority (PRIn) registers.

Loading...

Loading...