SWAS032-013

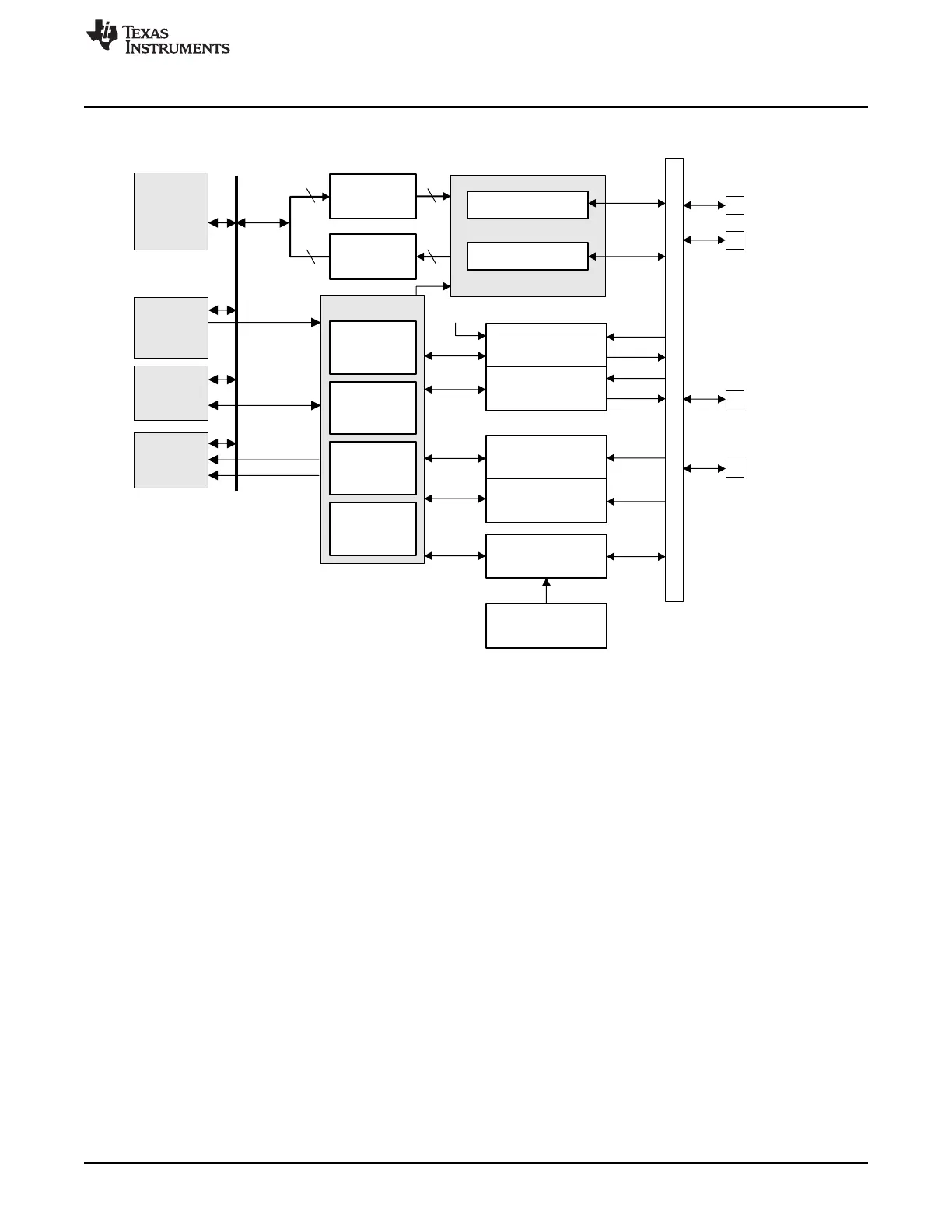

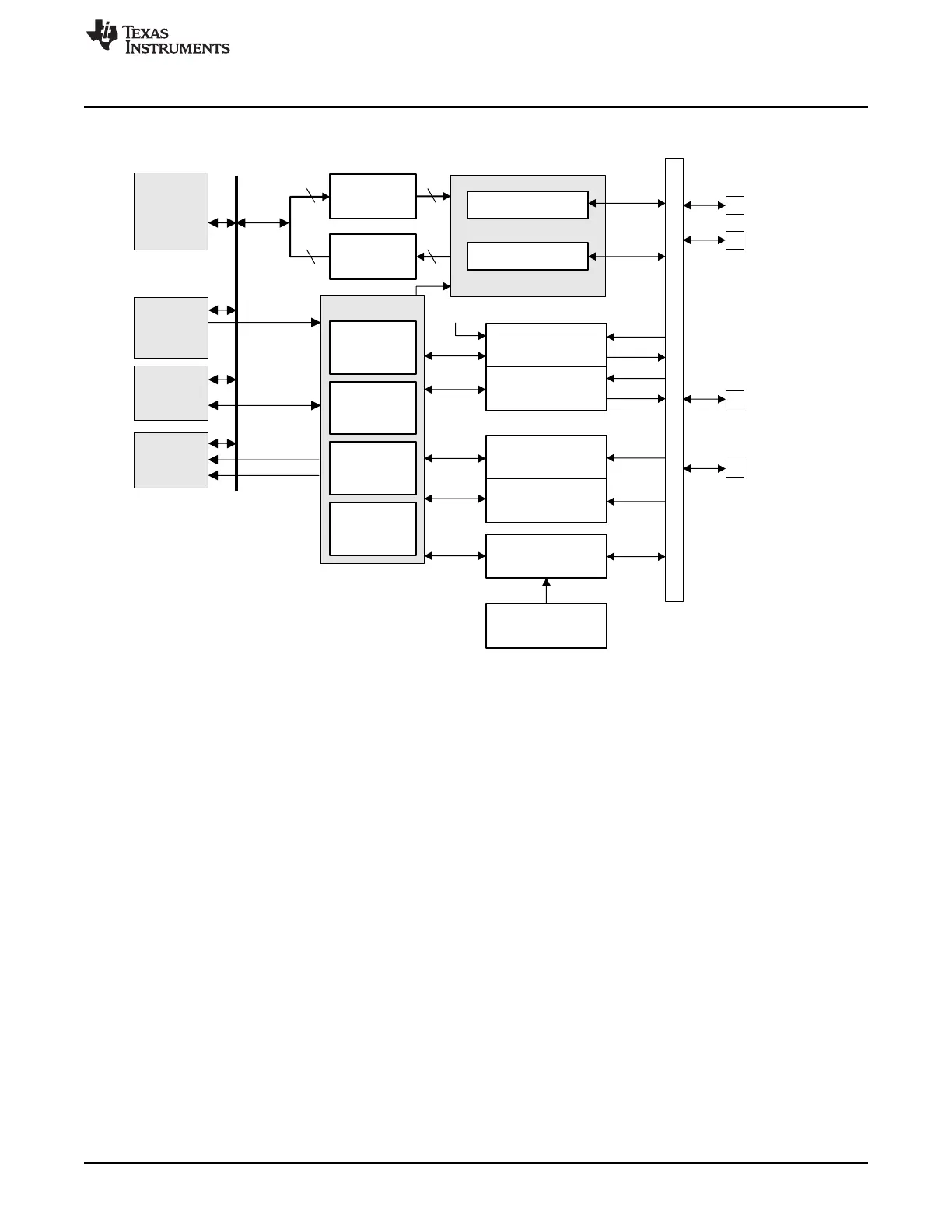

Local

host

System

clock

unit

System

interrupt

System

DMA

32 32

32 32

Transmit

format unit

Receive

format unit

Control

Transmit

state

machine

Transmit

TDM

sequencer

Receive

state

machine

Receive

TDM

sequencer

AUXCLK

Serializer 0

Serializer 1

Transmit

McAXR0

McACLKX

McACLKR

McAFSX

McAFSR

Pin function control

Clock

generator

Frame-sync

generator

Receive

Error check

Clock check

circuit

Clock

generator

Frame-sync

generator

McAXR1

www.ti.com

Functional Description

403

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Inter-Integrated Sound (I2S) Multichannel Audio Serial Port

Figure 12-2. I2S Module

12.2 Functional Description

The configuration options follow:

• Interface

– Bit clock configuration (generated internally in the device) – speed, polarity, and so forth

– Frame-sync configuration – speed, polarity, width, and so forth

• Data format

– Alignment (left or right)

– Order (MSB first or LSB first)

– Pad

– Slot size

• Data transfer (CPU or DMA)

For details on the APIs used for I2S configuration, see Section 12.4.

12.3 Programming Model

12.3.1 Clock and Reset Management

The Power, Reset, and Clock Management (PRCM) module manages the clock and reset. The I2S master

module is sourced by a 240-MHz clock through a fractional clock divider. By default, this divider is set to

output 24-MHz clock to the I2S module. The minimum frequency obtained by configuring this divider is

(240000 kHz/1023.99) = 234.377 kHz.

Loading...

Loading...