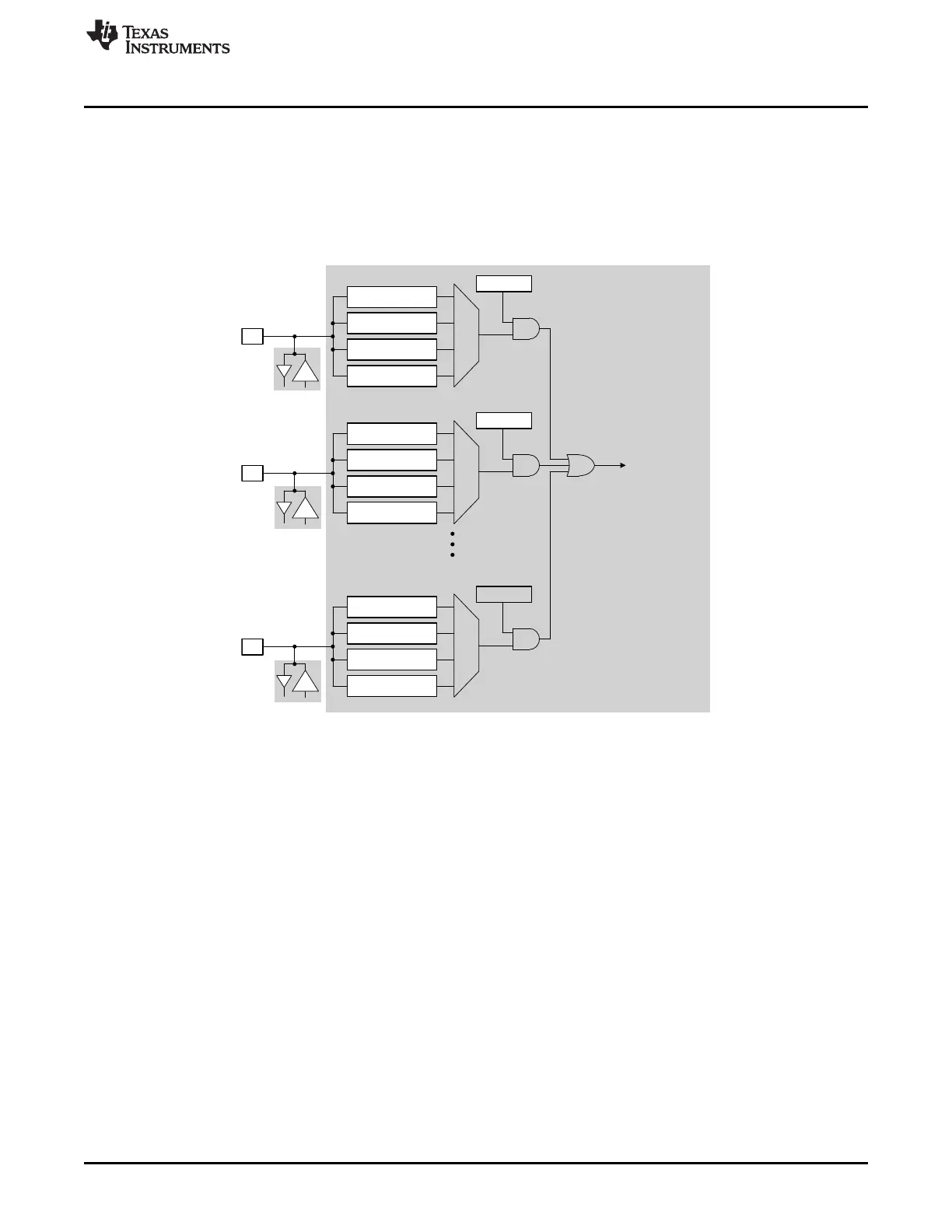

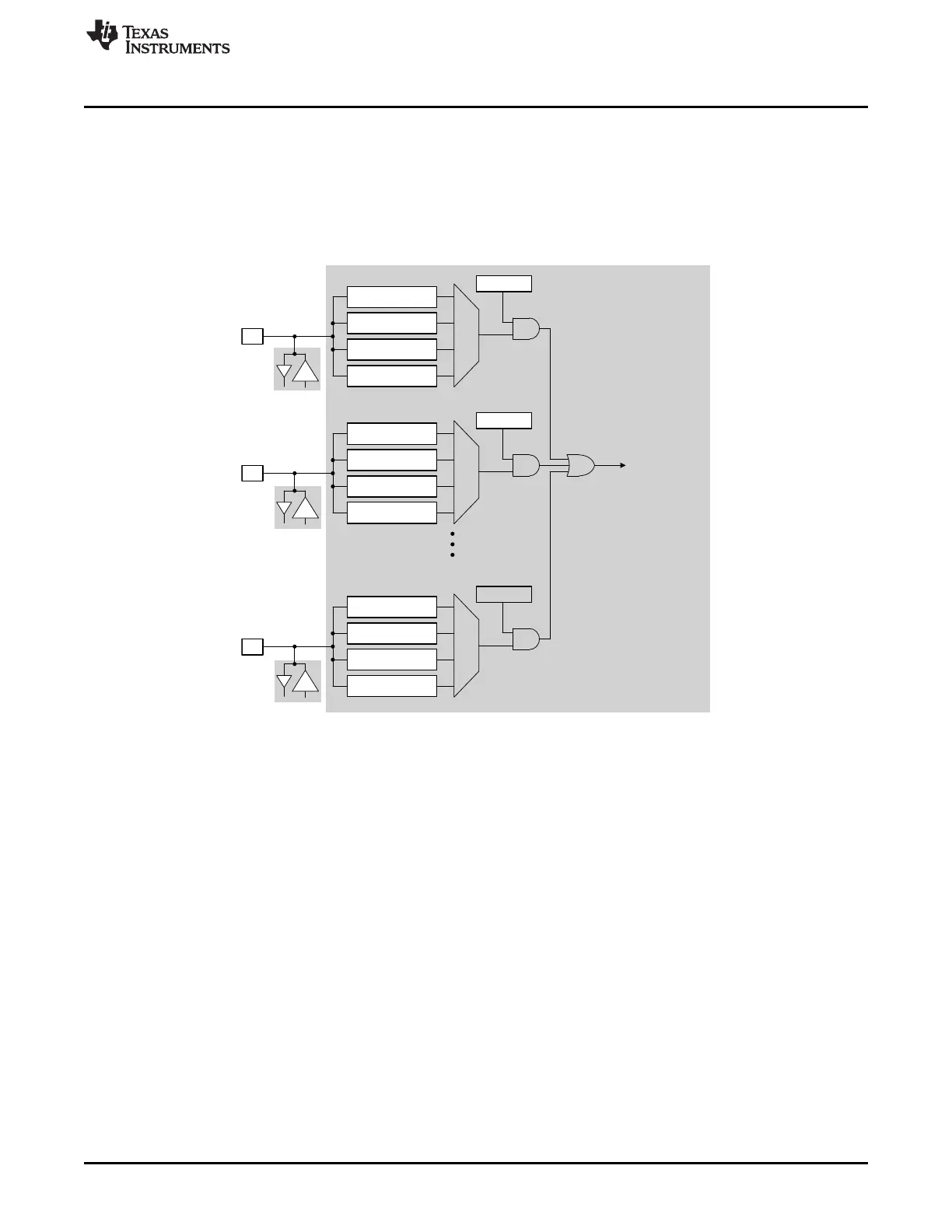

VBAT POWERED LOGIC

LEVEL = 0 TRIGGER

LEVEL = 1 TRIGGER

RISE EDGE TRIGGER

FALL EDGE TRIGGER

IO CELL

LEVEL = 0 TRIGGER

LEVEL = 1 TRIGGER

RISE EDGE TRIGGER

FALL EDGE TRIGGER

IO CELL

LEVEL = 0 TRIGGER

LEVEL = 1 TRIGGER

RISE EDGE TRIGGER

FALL EDGE TRIGGER

IO CELL

MASK BIT

MASK BIT

MASK BIT

PIN

PIN

PIN

WAKE FROM HIB

www.ti.com

Pin Mapping Recommendations

609

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

I/O Pads and Pin Multiplexing

16.8.5 Wake on Pad

The CC32xx supports wake from hibernate and LPDS on pad events for up to six pins. Figure 16-4 shows

the implementation for hibernate.

Similar capability is available in LPDS mode as well. However, in case of LPDS, only one pin at a time

can be selected as the wake-up source. Wake-up sources are covered in detail in .

Figure 16-4. Wake on Pad for Hibernate Mode

Loading...

Loading...