www.ti.com

SHA-MD5 Registers

705

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

SHA/MD5 Accelerator

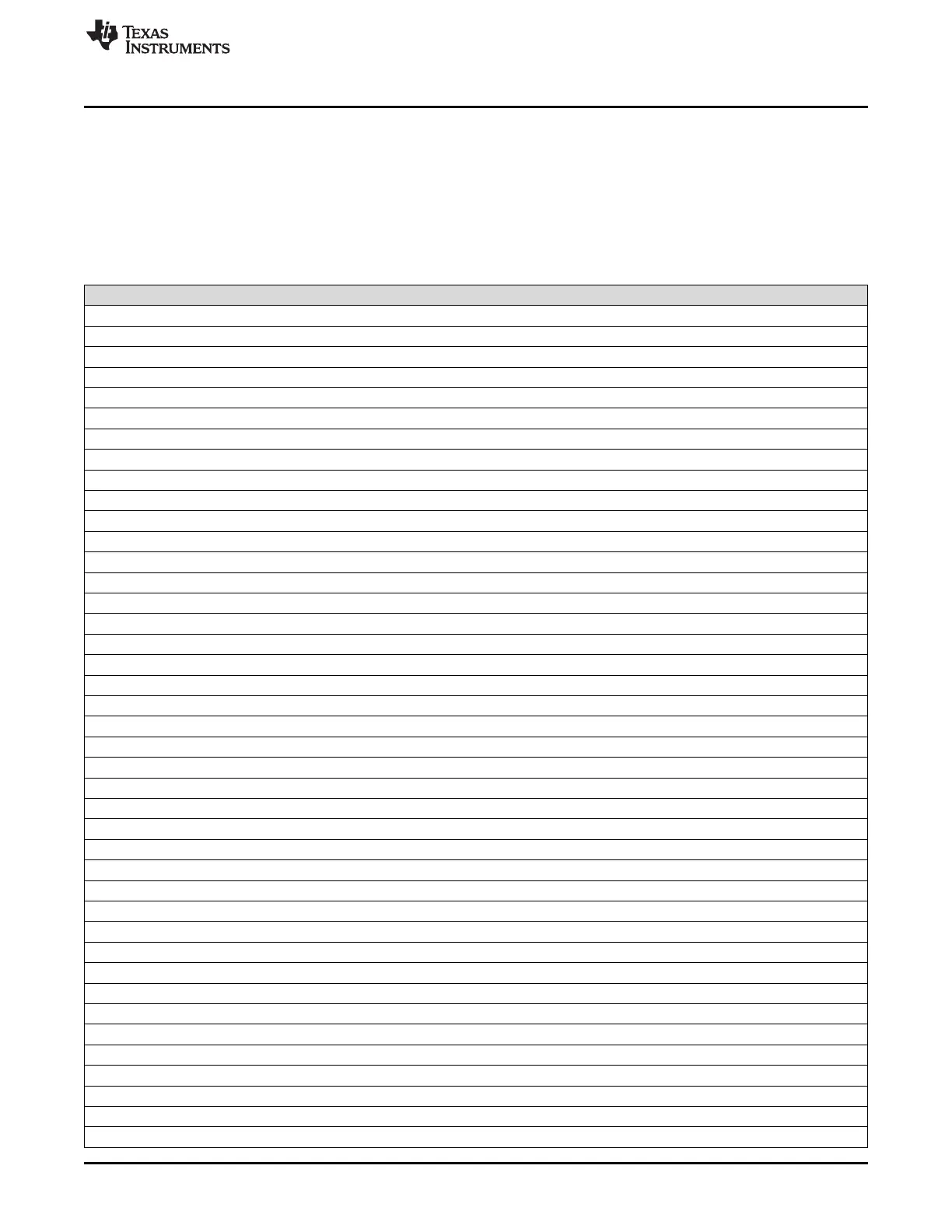

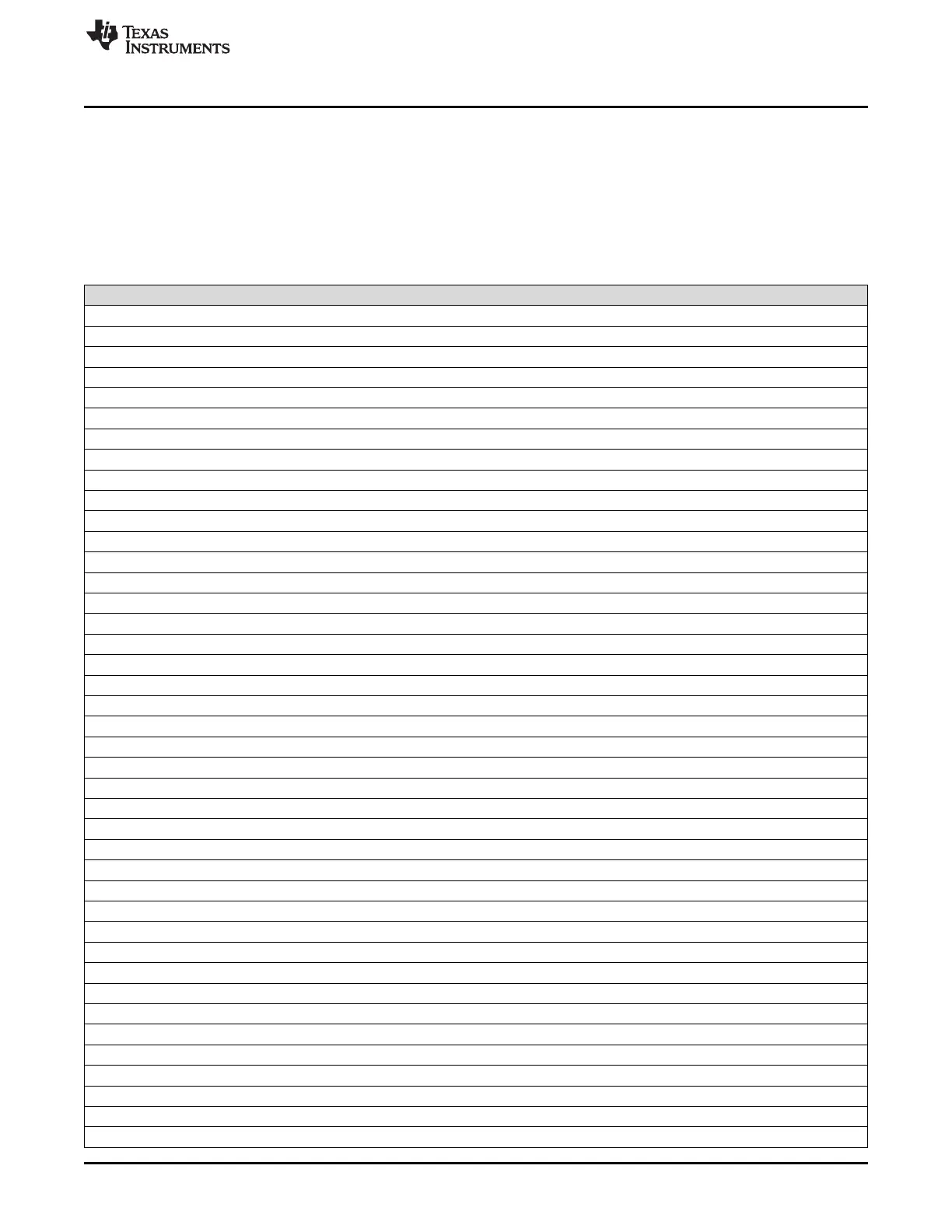

19.2 SHA-MD5 Registers

SHAMD5 functional registers offset: 0x4403 5000.

Table 19-11 lists the memory-mapped registers for SHA/MD5. All register offset addresses not listed in

Table 19-11 should be considered as reserved locations and the register contents should not be modified.

Figure 19-4 shows an overview of Public World, Inner and Outer Digest registers, and usage for MD5,

SHA-1, and SHA-224/256.

Table 19-11. SHA-MD5 Registers

Offset Acronym Register Name Section

0h SHAMD5_ODIGEST_A Outer Digest Register A Section 19.2.1

4h SHAMD5_ODIGEST_B Outer Digest Register B Section 19.2.2

8h SHAMD5_ODIGEST_C Outer Digest Register C Section 19.2.3

Ch SHAMD5_ODIGEST_D Outer Digest Register D Section 19.2.4

10h SHAMD5_ODIGEST_E Outer Digest Register E Section 19.2.5

14h SHAMD5_ODIGEST_F Outer Digest Register F Section 19.2.6

18h SHAMD5_ODIGEST_G Outer Digest Register G Section 19.2.7

1Ch SHAMD5_ODIGEST_H Outer Digest Register H Section 19.2.8

20h SHAMD5_IDIGEST_A Inner Digest Register A Section 19.2.9

24h SHAMD5_IDIGEST_B Inner Digest Register B Section 19.2.10

28h SHAMD5_IDIGEST_C Inner Digest Register C Section 19.2.11

2Ch SHAMD5_IDIGEST_D Inner Digest Register D Section 19.2.12

30h SHAMD5_IDIGEST_E Inner Digest Register E Section 19.2.13

34h SHAMD5_IDIGEST_F Inner Digest Register F Section 19.2.14

38h SHAMD5_IDIGEST_G Inner Digest Register G Section 19.2.15

3Ch SHAMD5_IDIGEST_H Inner Digest Register H Section 19.2.16

40h SHAMD5_DIGEST_COUNT Digest Count Section 19.2.17

44h SHAMD5_MODE SHA Mode Section 19.2.18

48h SHAMD5_LENGTH SHA Length Section 19.2.19

80h SHAMD5_DATA0_IN Data input message 0 Section 19.2.20

84h SHAMD5_DATA1_IN Data input message 1 Section 19.2.21

88h SHAMD5_DATA2_IN Data input message 2 Section 19.2.22

8Ch SHAMD5_DATA3_IN Data input message 3 Section 19.2.23

90h SHAMD5_DATA4_IN Data input message 4 Section 19.2.24

94h SHAMD5_DATA5_IN Data input message 5 Section 19.2.25

98h SHAMD5_DATA6_IN Data input message 6 Section 19.2.26

9Ch SHAMD5_DATA7_IN Data input message 7 Section 19.2.27

A0h SHAMD5_DATA8_IN Data input message 8 Section 19.2.28

A4h SHAMD5_DATA9_IN Data input message 9 Section 19.2.29

A8h SHAMD5_DATA10_IN Data input message 10 Section 19.2.30

ACh SHAMD5_DATA11_IN Data input message 11 Section 19.2.31

B0h SHAMD5_DATA12_IN Data input message 12 Section 19.2.32

B4h SHAMD5_DATA13_IN Data input message 13 Section 19.2.33

B8h SHAMD5_DATA14_IN Data input message 14 Section 19.2.34

BCh SHAMD5_DATA15_IN Data input message 15 Section 19.2.35

110h SHAMD5_SYSCONFIG System Config Section 19.2.36

118h SHAMD5_IRQSTATUS IRQ Status Section 19.2.37

11Ch SHAMD5_IRQENABLE IRQ Enable Section 19.2.38

810h DTHE_SHA_IM SHA Interrupt Mask Set Section 19.2.39

814h DTHE_SHA_RIS SHA Interrupt Raw Interrupt Status Section 19.2.40

818h DTHE_SHA_MIS SHA Interrupt Masked interrupt Status Section 19.2.41

Loading...

Loading...