Register Map

www.ti.com

94

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Cortex

®

-M4 Peripherals

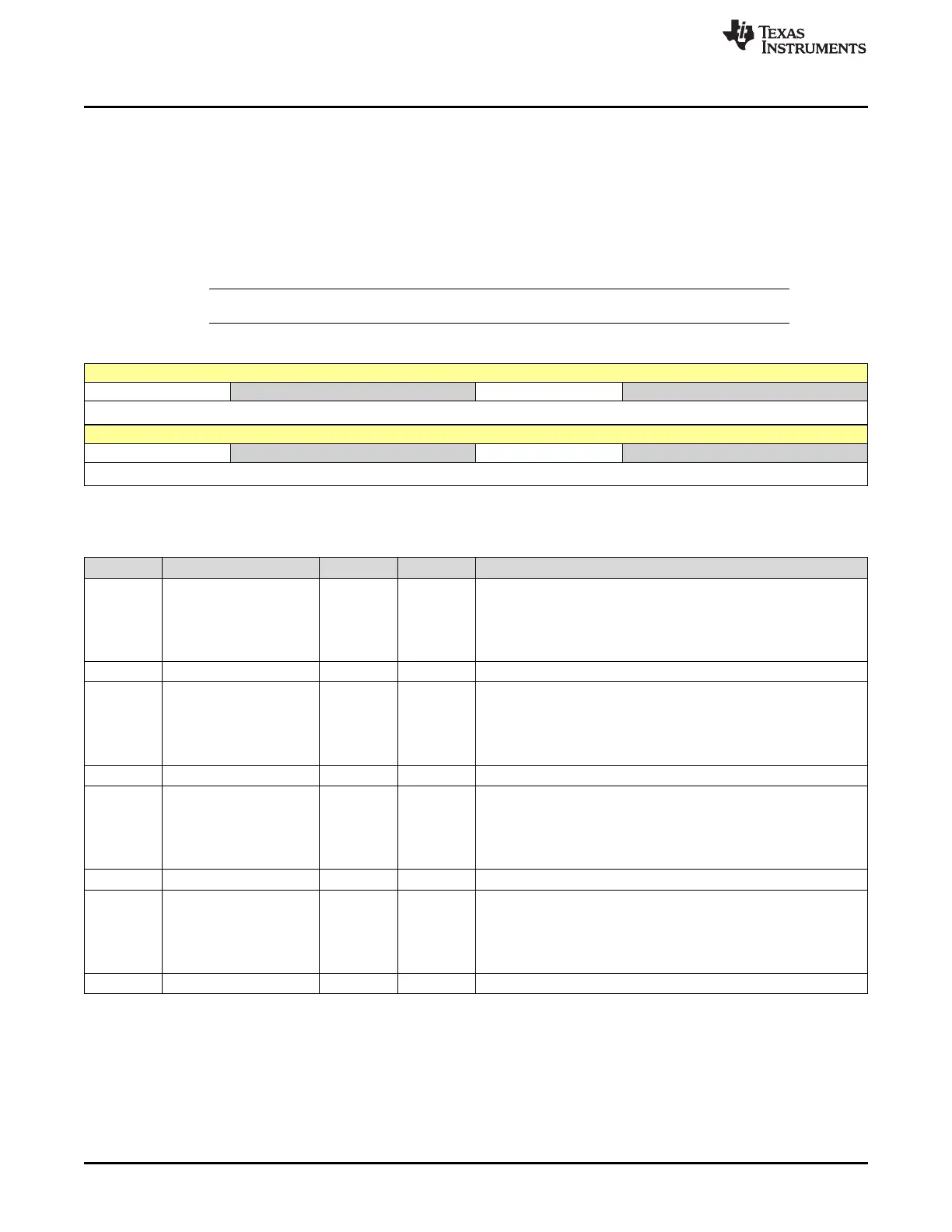

3.3.1.10 PRI_0 to PRI_49 Register (offset = 400h to 4C4h) [reset = 0h]

PRI_0 to PRI_49 is shown in Figure 3-10 and described in Table 3-13.

The PRIn registers provide 3-bit priority fields for each interrupt. These registers are byte accessible. Each

register holds four priority fields that are assigned to interrupts as follows: bits 31 to 29 have interrupt

[4n+3], bits 23 to 21 have interrupt [4n+2], bits 15 to 13 have interrupt [4n+1], and bits 7 to have interrupt

[4n]. Each priority level can be split into separate group priority and subpriority fields. The PRIGROUP

field in the Application Interrupt and Reset Control (APINT) register indicates the position of the binary

point that splits the priority and subpriority fields.

NOTE: This register can only be accessed from privileged mode.

Figure 3-10. PRI_0 to PRI_49 Register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

INTD RESERVED INTC RESERVED

R/W-0h R-0h R/W-0h R-0h

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

INTB RESERVED INTA RESERVED

R/W-0h R-0h R/W-0h R-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

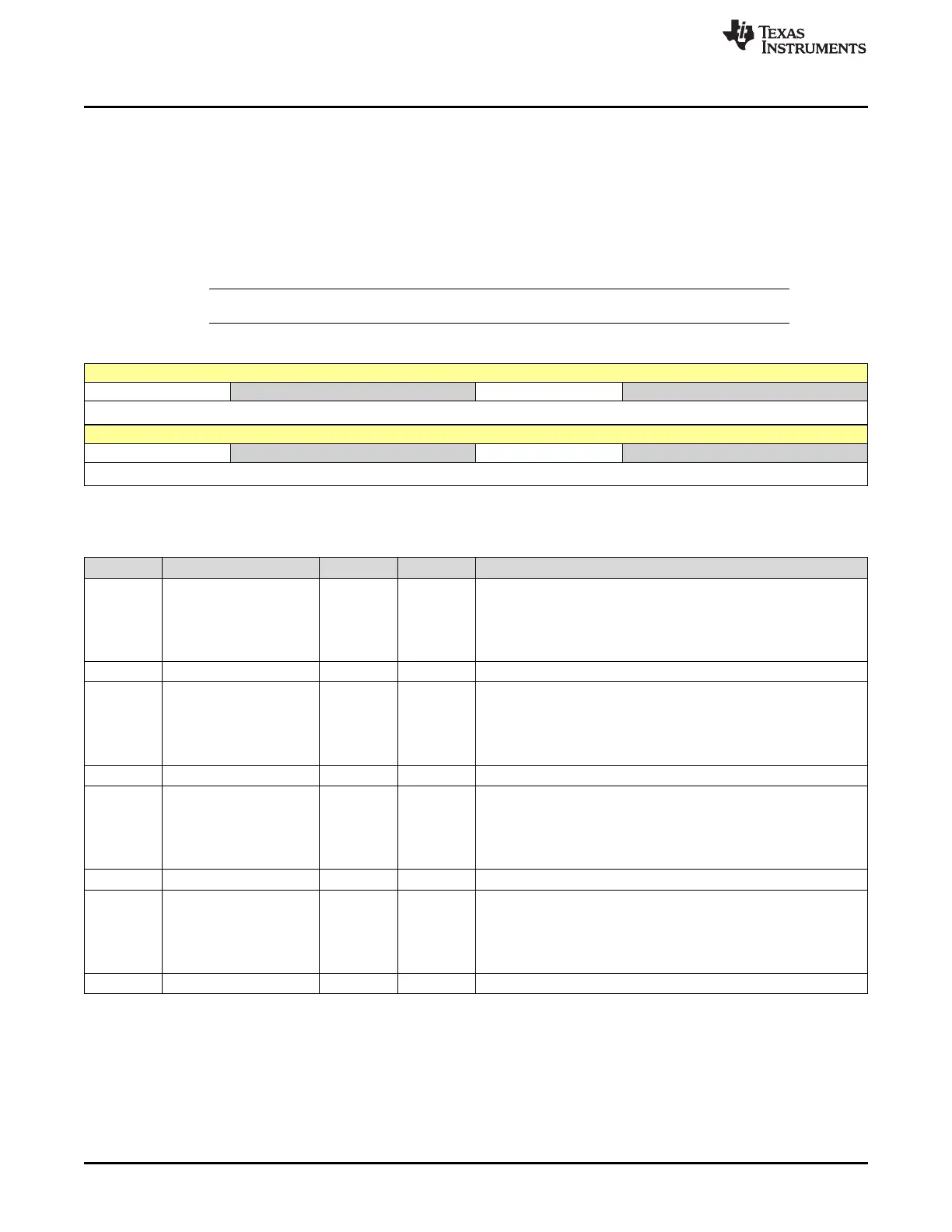

Table 3-13. PRI_0 to PRI_49 Register Field Descriptions

Bit Field Type Reset Description

31-29 INTD R/W 0h

Interrupt Priority for Interrupt [4n+3]

This field holds a priority value, 0-7, for the interrupt with the number

[4n+3], where n is the number of the Interrupt Priority register (n=0

for PRI0, and so on). The lower the value, the greater the priority of

the corresponding interrupt.

28-24 RESERVED R 0h

23-21 INTC R/W 0h

Interrupt Priority for Interrupt [4n+2]

This field holds a priority value, 0-7, for the interrupt with the number

[4n+2], where n is the number of the Interrupt Priority register (n=0

for PRI0, and so on). The lower the value, the greater the priority of

the corresponding interrupt.

20-16 RESERVED R 0h

15-13 INTB R/W 0h

Interrupt Priority for Interrupt [4n+1]

This field holds a priority value, 0-7, for the interrupt with the number

[4n+1], where n is the number of the Interrupt Priority register (n=0

for PRI0, and so on). The lower the value, the greater the priority of

the corresponding interrupt.

12-8 RESERVED R 0h

7-5 INTA R/W 0h

Interrupt Priority for Interrupt [4n]

This field holds a priority value, 0-7, for the interrupt with the number

[4n], where n is the number of the Interrupt Priority register (n=0 for

PRI0, and so on). The lower the value, the greater the priority of the

corresponding interrupt.

4-0 RESERVED R 0h

Loading...

Loading...