I2C Registers

www.ti.com

240

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Inter-Integrated Circuit (I

2

C) Interface

7.3.10 I2CMCLKOCNT Register (Offset = 24h) [reset = 0h]

I2CMCLKOCNT is shown in Figure 7-23 and described in Table 7-14.

Return to Summary Table.

This register contains the upper 8 bits of a 12-bit counter that can be used to keep the timeout limit for

clock stretching by a remote slave. The lower four bits of the counter are not user visible and are always

0x0.

NOTE: The master clock low timeout counter counts for the entire time SCL is held Low

continuously. If SCL is de-asserted at any point, the master clock low timeout counter is

reloaded with the value in the I2CMCLKOCNT register and begins counting down from this

value.

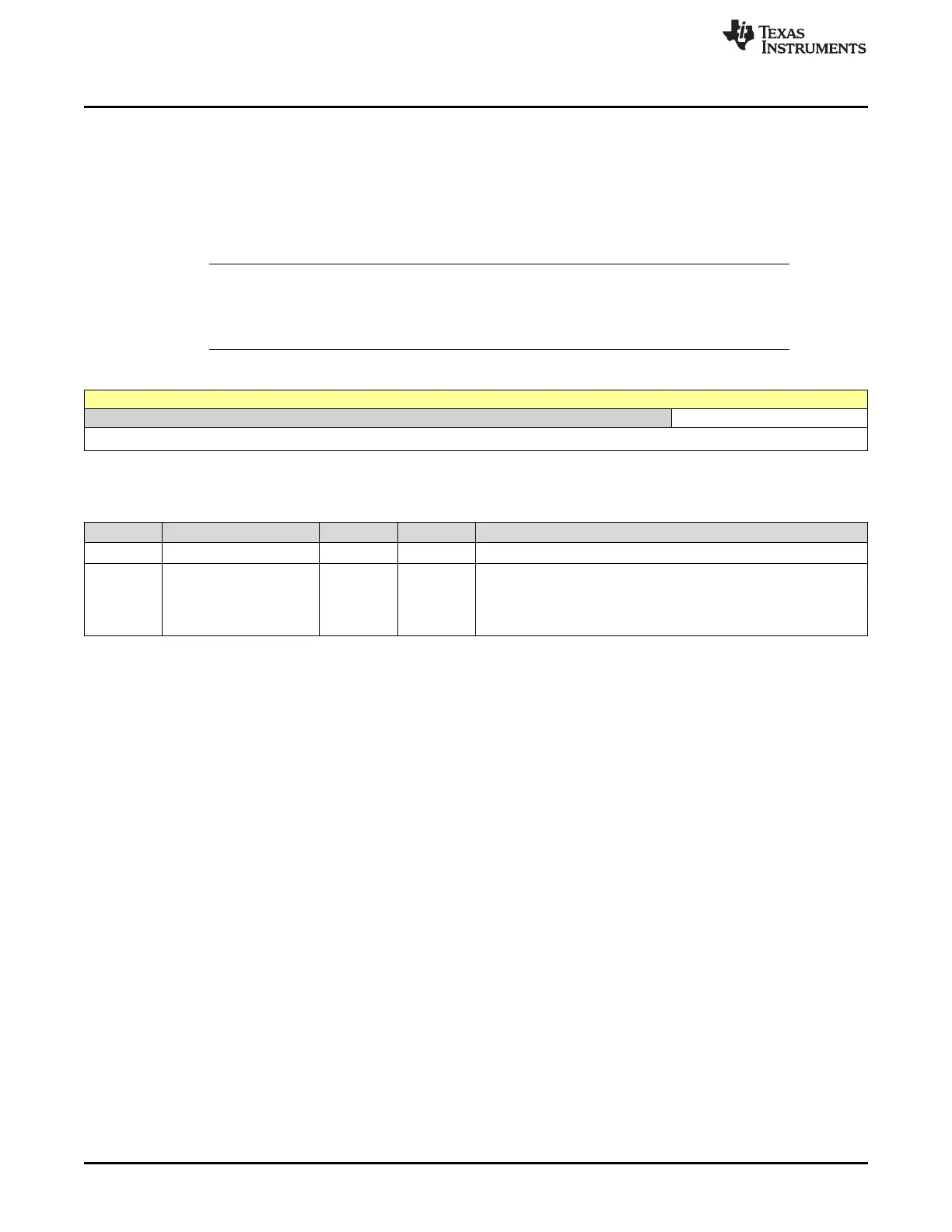

Figure 7-23. I2CMCLKOCNT Register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RESERVED CNTL

R-0h R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

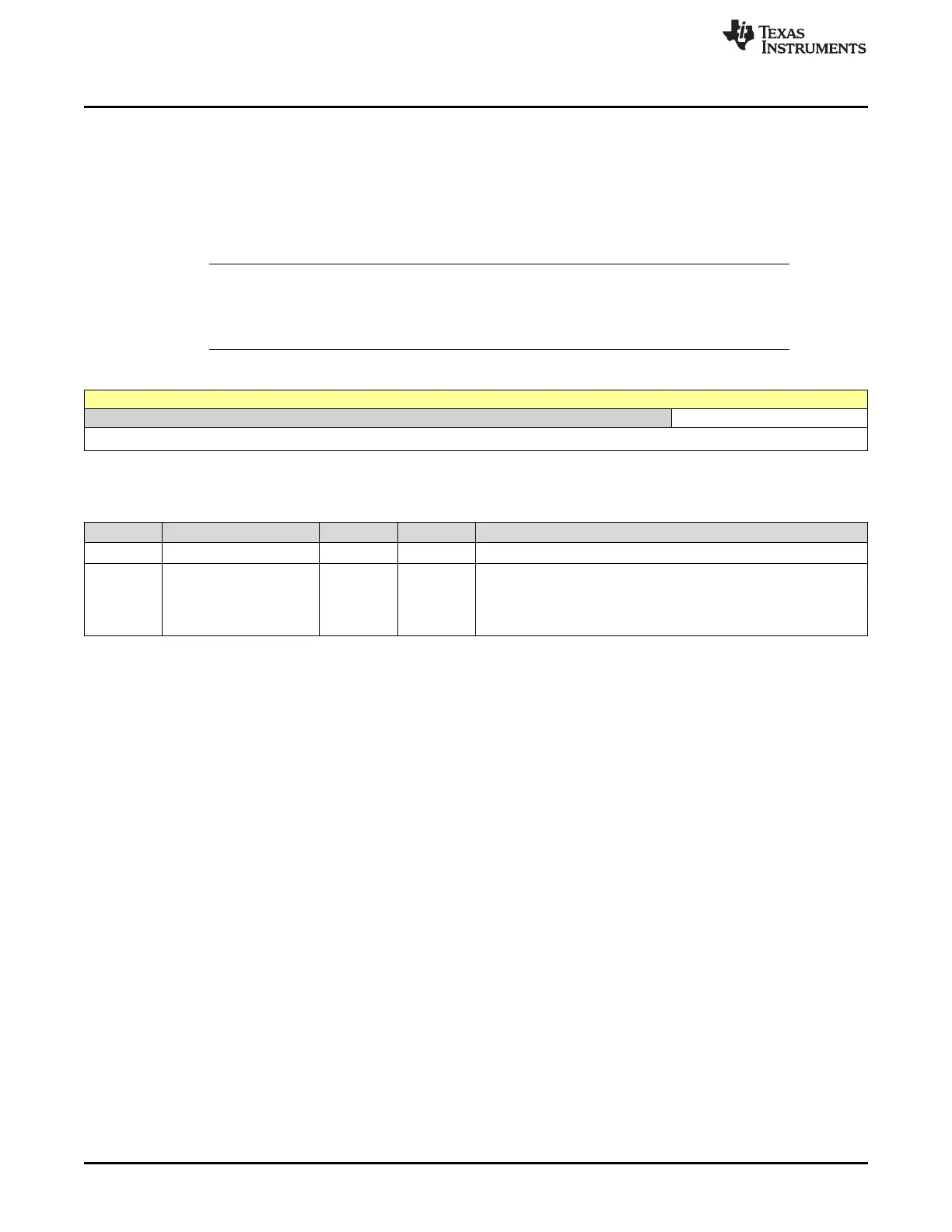

Table 7-14. I2CMCLKOCNT Register Field Descriptions

Bit Field Type Reset Description

31-8 RESERVED R 0h

7-0 CNTL R/W 0h

I2C Master Count

This field contains the upper 8 bits of a 12-bit counter for the clock

low timeout count.

Note: The value of CNTL must be greater than 0x1.

Loading...

Loading...