www.ti.com

Timer Registers

329

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

General-Purpose Timers

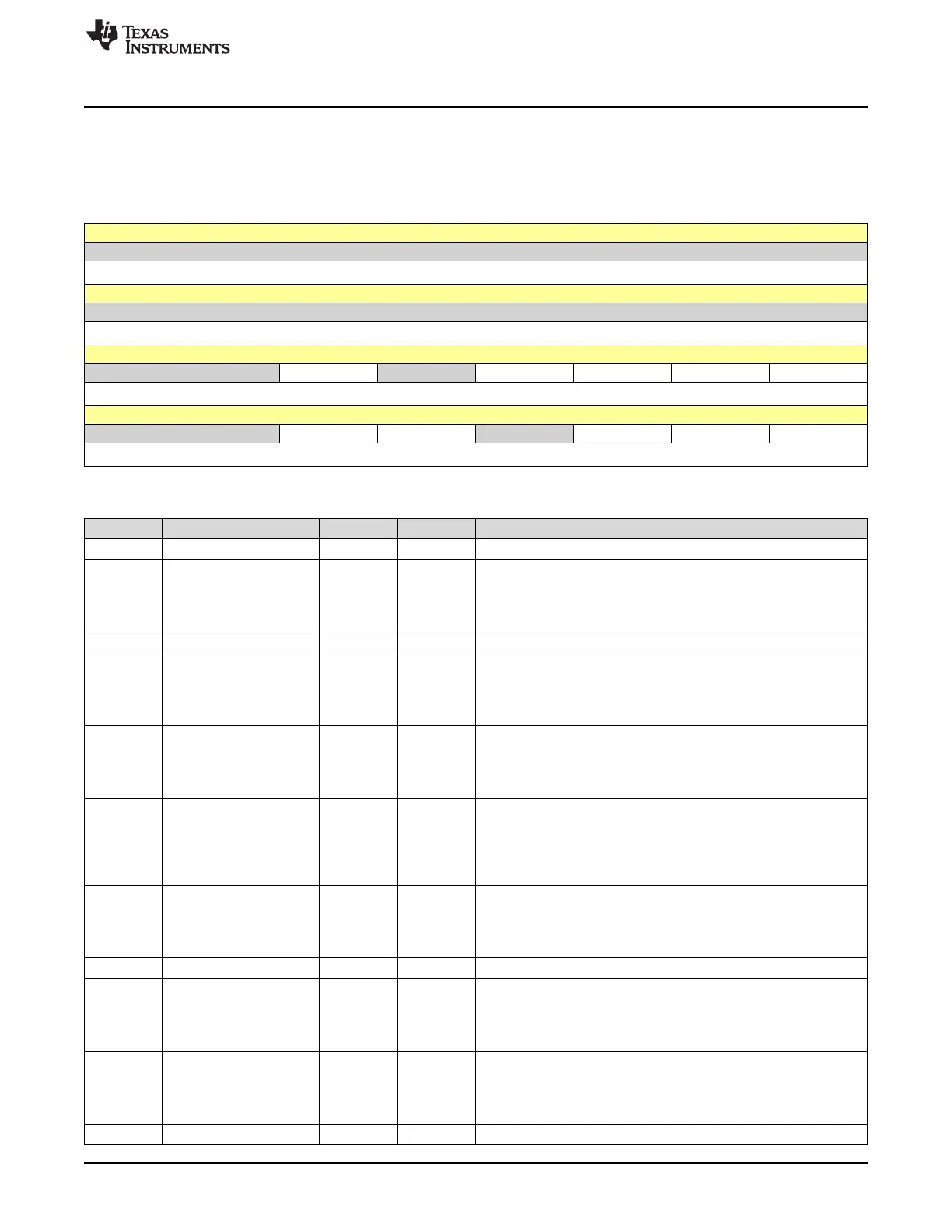

9.5.7 GPTMMIS Register (offset = 20h) [reset = 0h]

Register mask: 0h

GPTMMIS is shown in Figure 9-11 and described in Table 9-15.

Figure 9-11. GPTMMIS Register

31 30 29 28 27 26 25 24

RESERVED

R-X

23 22 21 20 19 18 17 16

RESERVED

R-X

15 14 13 12 11 10 9 8

RESERVED DMABMIS RESERVED TBMMIS CBEMIS CBMMIS TBTOMIS

R-X R-X R-X R-X R-X R-X R-X

7 6 5 4 3 2 1 0

RESERVED DMAAMIS TAMMIS RESERVED CAEMIS CAMMIS TATOMIS

R-X R-X R-X R-X R-X R-X R-X

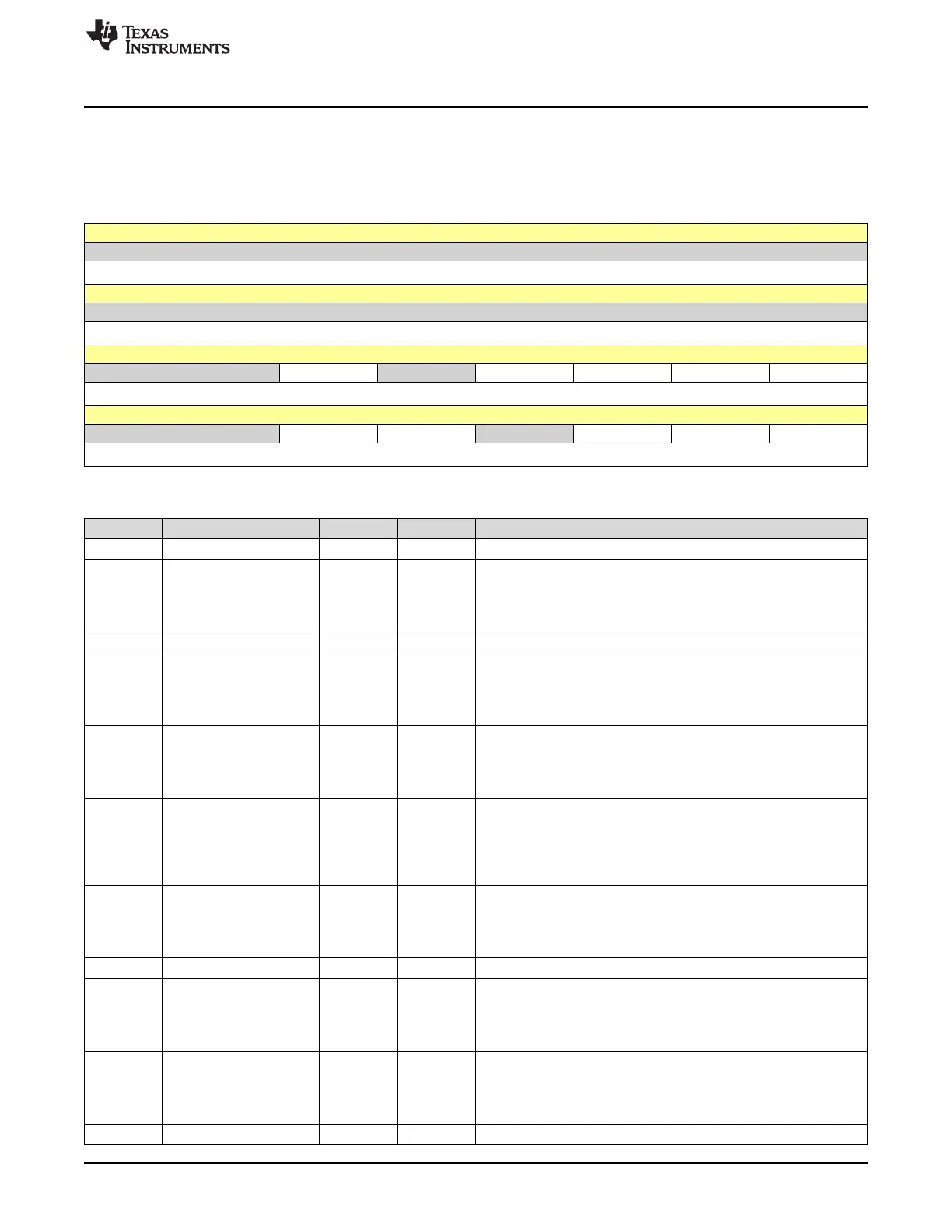

Table 9-15. GPTMMIS Register Field Descriptions

Bit Field Type Reset Description

31-14 RESERVED R X

13 DMABMIS R X

GPTM Timer B DMA Done Masked Interrupt. This bit is cleared by

writing 1 to the DMABINT bit in the GPTMICR register.

0h = A Timer B DMA done interrupt has not occurred or is masked.

1h = An unmasked Timer B DMA done interrupt has occurred.

12 RESERVED R X

11 TBMMIS R X

GPTM Timer B Match Masked Interrupt. This bit is cleared by writing

1 to the TBMCINT bit in the GPTMICR register.

0h = A Timer B mode match interrupt has not occurred or is masked.

1h = An unmasked Timer B mode match interrupt has occurred.

10 CBEMIS R X

GPTM Timer B Capture Mode Event Masked Interrupt. This bit is

cleared by writing 1 to the CBECINT bit in the GPTMICR register.

0h = A Capture B event interrupt has not occurred or is masked.

1h = An unmasked Capture B event interrupt has occurred.

9 CBMMIS R X

GPTM Timer B Capture Mode Match Masked Interrupt. This bit is

cleared by writing 1 to the CBMCINT bit in the GPTMICR register.

0h = A Capture B mode match interrupt has not occurred or is

masked.

1h = An unmasked Capture B match interrupt has occurred.

8 TBTOMIS R X

GPTM Timer B Time-Out Masked Interrupt. This bit is cleared by

writing 1 to the TBTOCINT bit in the GPTMICR register.

0h = A Timer B time-out interrupt has not occurred or is masked.

1h = An unmasked Timer B time-out interrupt has occurred.

7-6 RESERVED R X

5 DMAAMIS R X

GPTM Timer A DMA Done Masked Interrupt. This bit is cleared by

writing 1 to the DMAAINT bit in the GPTMICR register.

0h = A Timer A DMA done interrupt has not occurred or is masked.

1h = An unmasked Timer A DMA done interrupt has occurred.

4 TAMMIS R X

GPTM Timer A Match Masked Interrupt. This bit is cleared by writing

1 to the TAMCINT bit in the GPTMICR register.

0h = A Timer A mode match interrupt has not occurred or is masked.

1h = An unmasked Timer A mode match interrupt has occurred.

3 RESERVED R X

Loading...

Loading...