Debug

ATB

Slave

Port

ARM® Trace

Bus (ATB)

Interface

Asynchronous FIFO

Trace Out

(serializer)

Serial Wire

Trace Port

(SWO)

APB

Sla

ve

Port

Advance

Peripheral

Bus (APB)

Interface

www.ti.com

Overview

53

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Cortex

®

-M4 Processor

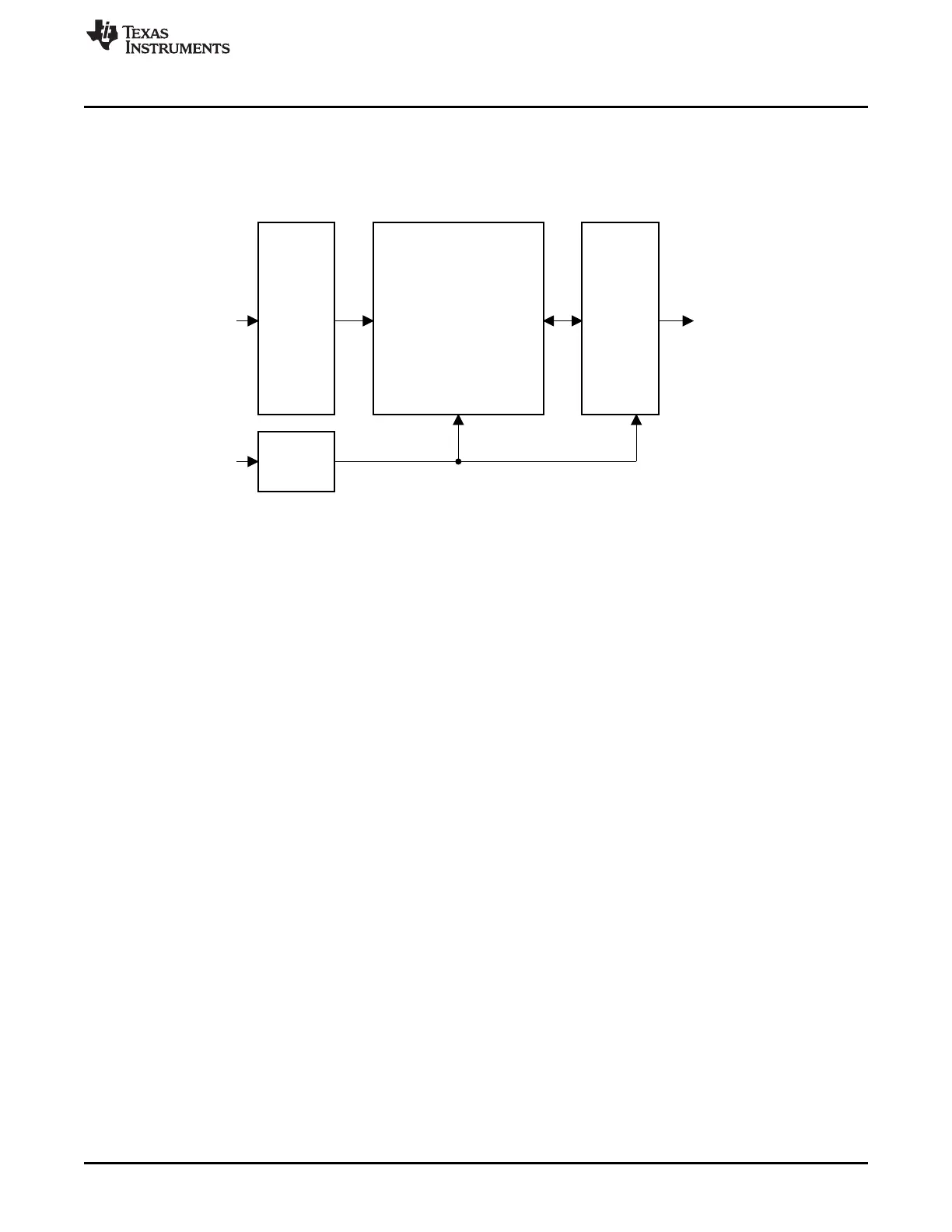

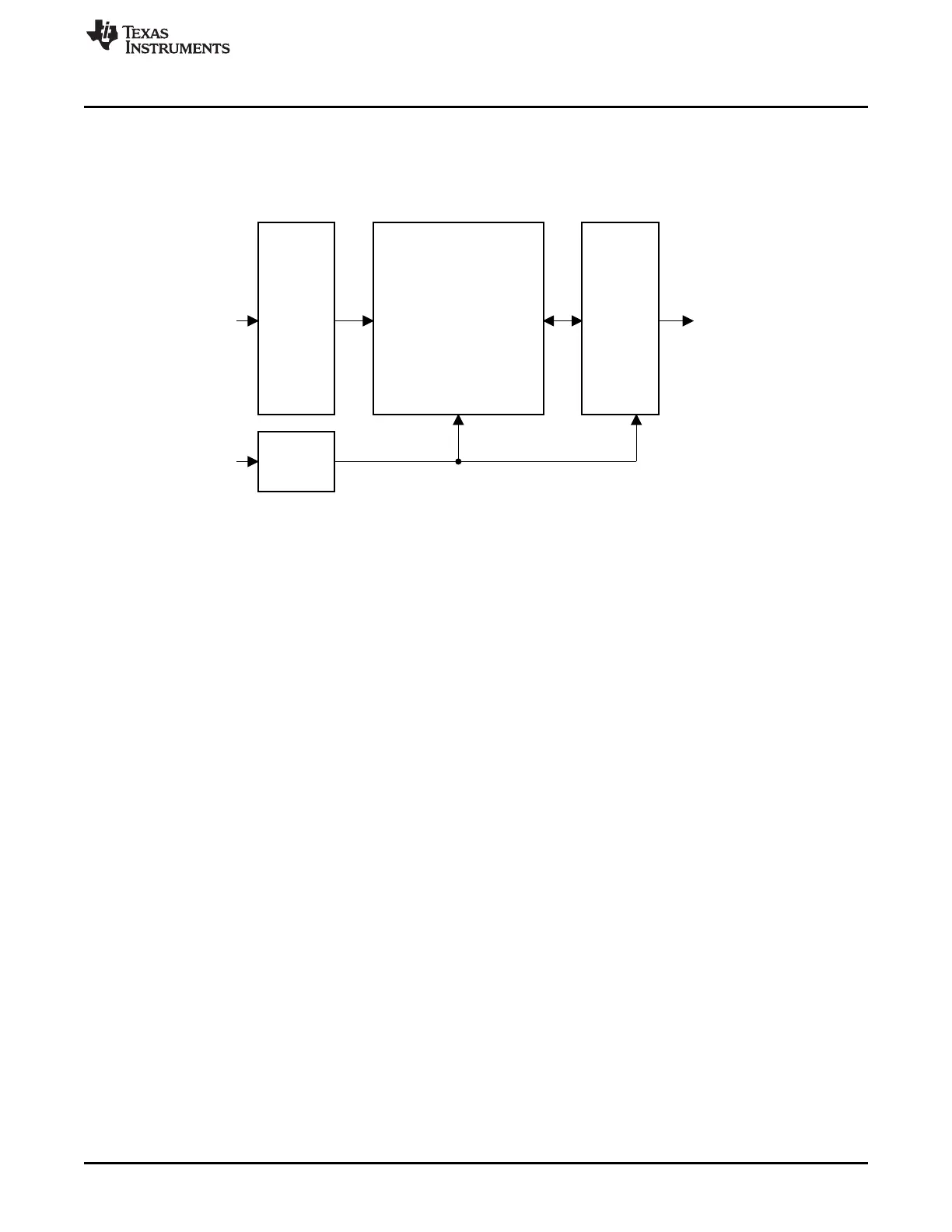

2.1.4 Trace Port Interface Unit (TPIU)

The TPIU acts as a bridge between the Cortex

®

-M4 trace data from the ITM, and an off-chip trace port

analyzer, as shown in Figure 2-2.

Figure 2-2. TPIU Block Diagram

2.1.5 Cortex

®

-M4 System Component Details

The Cortex

®

-M4 application processor core includes the following system components:

• SysTck: A 24-bit count-down timer used as an RTOS tick timer or as a simple counter (see

Section 3.2.1).

• Nested Vectored Interrupt Controller (NVIC): An embedded interrupt controller that supports low-

latency interrupt processing (see Nested Vectored Interrupt Controller [NVIC] in Section 3.2.2).

• System Control Block (SCB): The programming model interface to the processor. The SCB provides

system implementation information and system control, including configuration, control, and reporting

of system exceptions (see System Control Block [SCB] in Section 3.2.3).

Loading...

Loading...