www.ti.com

Register Map

89

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Cortex

®

-M4 Peripherals

3.3.1.5 EN_0 to EN_6 Register (offset = 100h to 118h) [reset = 0h]

EN_0 to EN_6 is shown in Figure 3-5 and described in Table 3-8.

The ENn registers enable interrupts and show which interrupts are enabled. Bit 0 of EN0 corresponds to

Interrupt 0; bit 31 corresponds to Interrupt 31. Bit 0 of EN1 corresponds to Interrupt 32; bit 31 corresponds

to Interrupt 63. Bit 0 of EN2 corresponds to Interrupt 64; bit 31 corresponds to Interrupt 95. Bit 0 of EN3

corresponds to Interrupt 96; bit 31 corresponds to Interrupt 127. Bit 0 of EN4 corresponds to Interrupt 128;

bit 31 corresponds to Interrupt 159. Bit 0 of EN5 corresponds to Interrupt 160; bit 31 corresponds to

Interrupt 191. Bit 0 of EN6 corresponds to interrupt 192; bit 7 corresponds to interrupt 199. If a pending

interrupt is enabled, the NVIC activates the interrupt based on its priority. If an interrupt is not enabled,

asserting its interrupt signal changes the interrupt state to pending, but the NVIC never activates the

interrupt, regardless of its priority.

NOTE: This register can only be accessed from privileged mode.

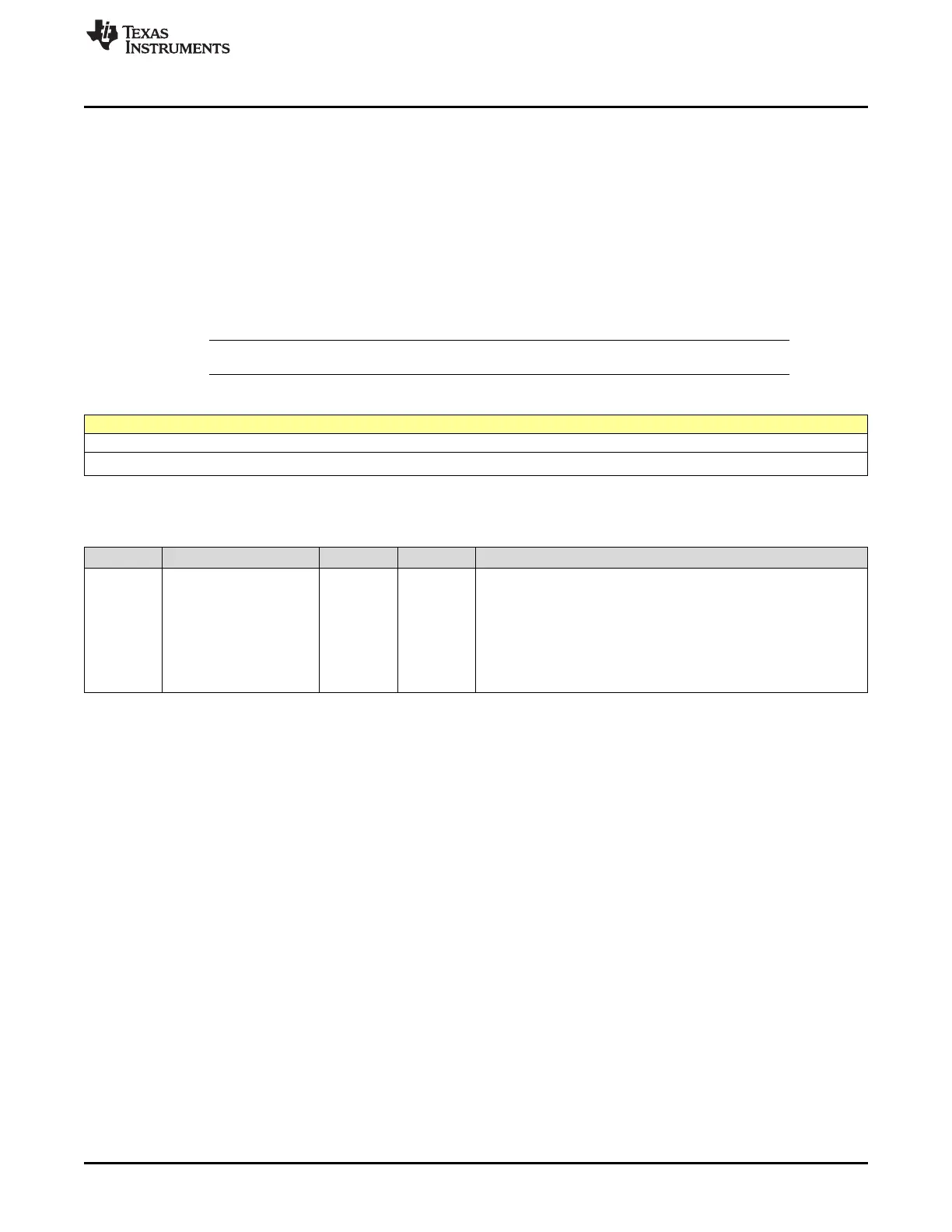

Figure 3-5. EN_0 to EN_6 Register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

INT

R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

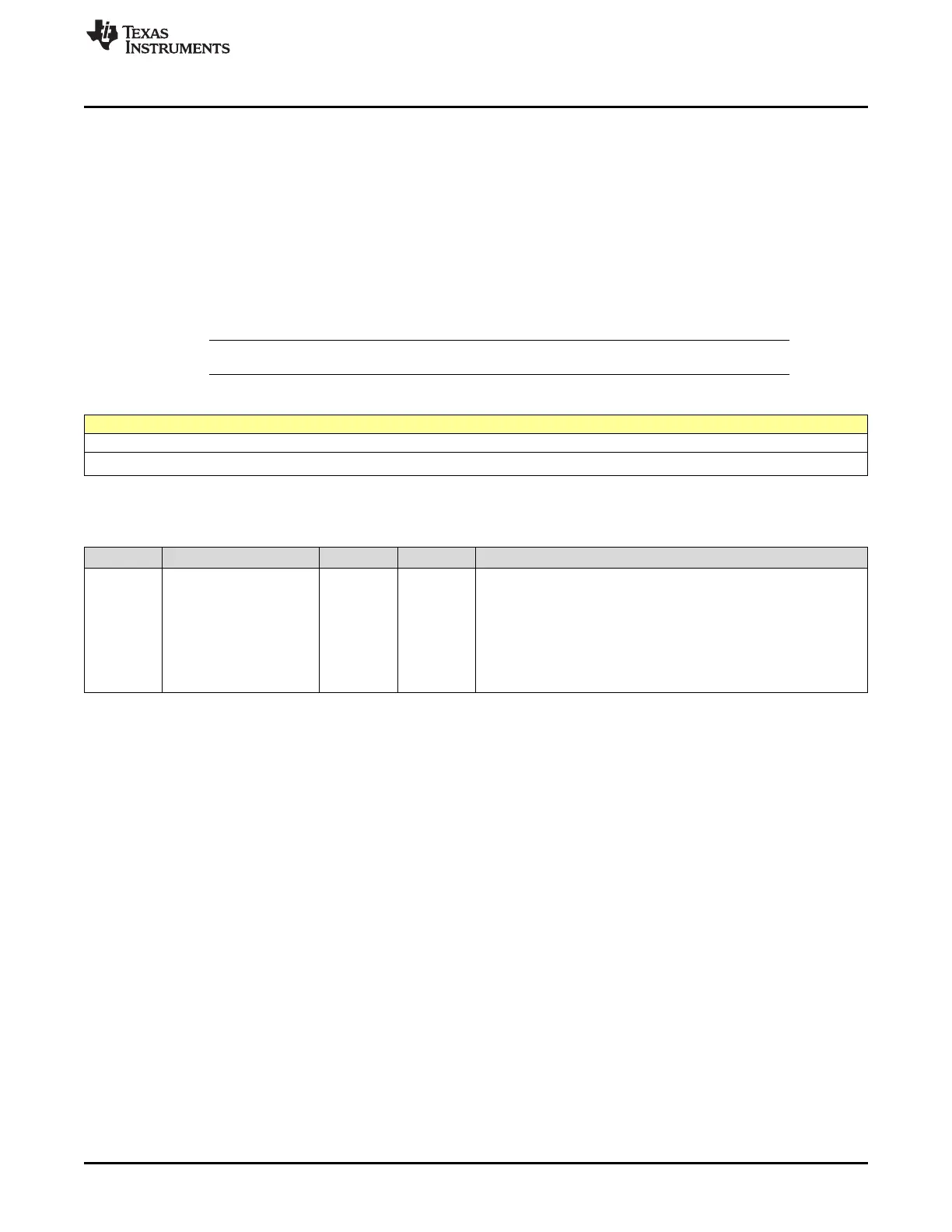

Table 3-8. EN_0 to EN_6 Register Field Descriptions

Bit Field Type Reset Description

31-0 INT R/W 0h

Interrupt Enable

A bit can only be cleared by setting the corresponding INT[n] bit in

the DISn register.

0h (W) = On a write, no effect.

0h (R) = On a read, indicates the interrupt is disabled.

1h (W) = On a write, enables the interrupt.

1h (R) = On a read, indicates the interrupt is enabled.

Loading...

Loading...