www.ti.com

DES Module Programming Guide – Low-Level Programming Models

671

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Data Encryption Standard Accelerator (DES)

18.4.2.2 DES Interrupt Mode

Table 18-5 lists the DES interrupt mode steps.

Table 18-5. DES Interrupt Mode

Step Register/Bit Field/Programming Model Value

Enable DES module interrupts. DES_IRQENABLE[2:0] 0x7

Load the input buffer data LSW register. DES_DATA_L[31:0] DATA_L –

Load the input buffer data HSW register. DES_DATA_H[31:0] DATA_H –

18.4.2.3 DES Interrupt DMA Mode

Table 18-6 lists the DES DMA mode steps.

Table 18-6. DES DMA Mode

Step Register/Bit Field/Programming Model Value

Enable DES module DMA requests. DES_SYSCONFIG[7:5] 0x7

Load the input buffer data LSW register. DES_DATA_L[31:0] DATA_L –

Load the input buffer data HSW register. DES_DATA_H[31:0] DATA_H –

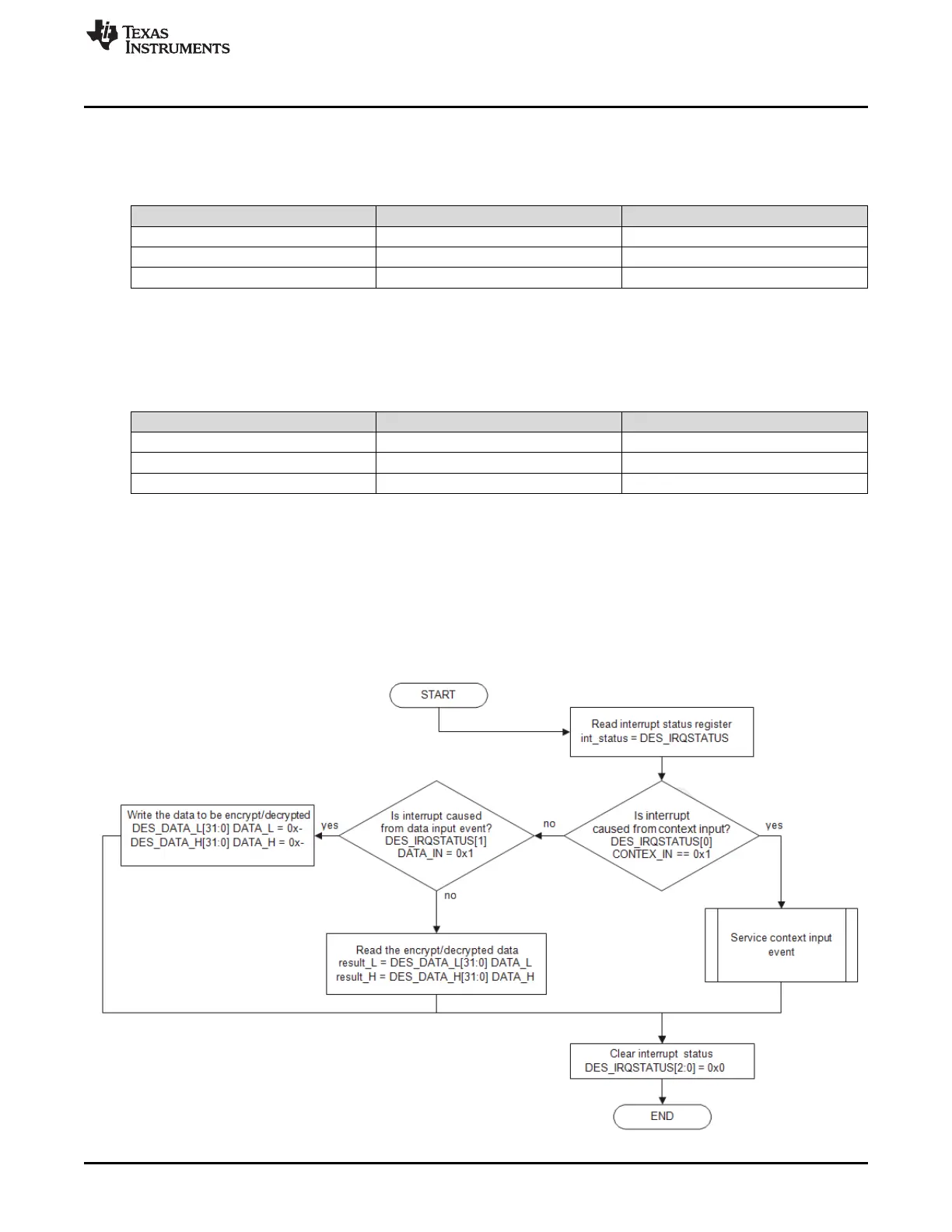

18.4.3 DES Events Servicing

18.4.3.1 Interrupt Servicing

This section describes the event servicing of the module. Figure 18-6 shows the DES interrupt service.

The registers used during event servicing are: DES_IRQSTATUS, DES_DATA_L, and DES_DATA_H.

Figure 18-6. DES Interrupt Service

Loading...

Loading...