www.ti.com

AES Registers

643

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Advance Encryption Standard Accelerator (AES)

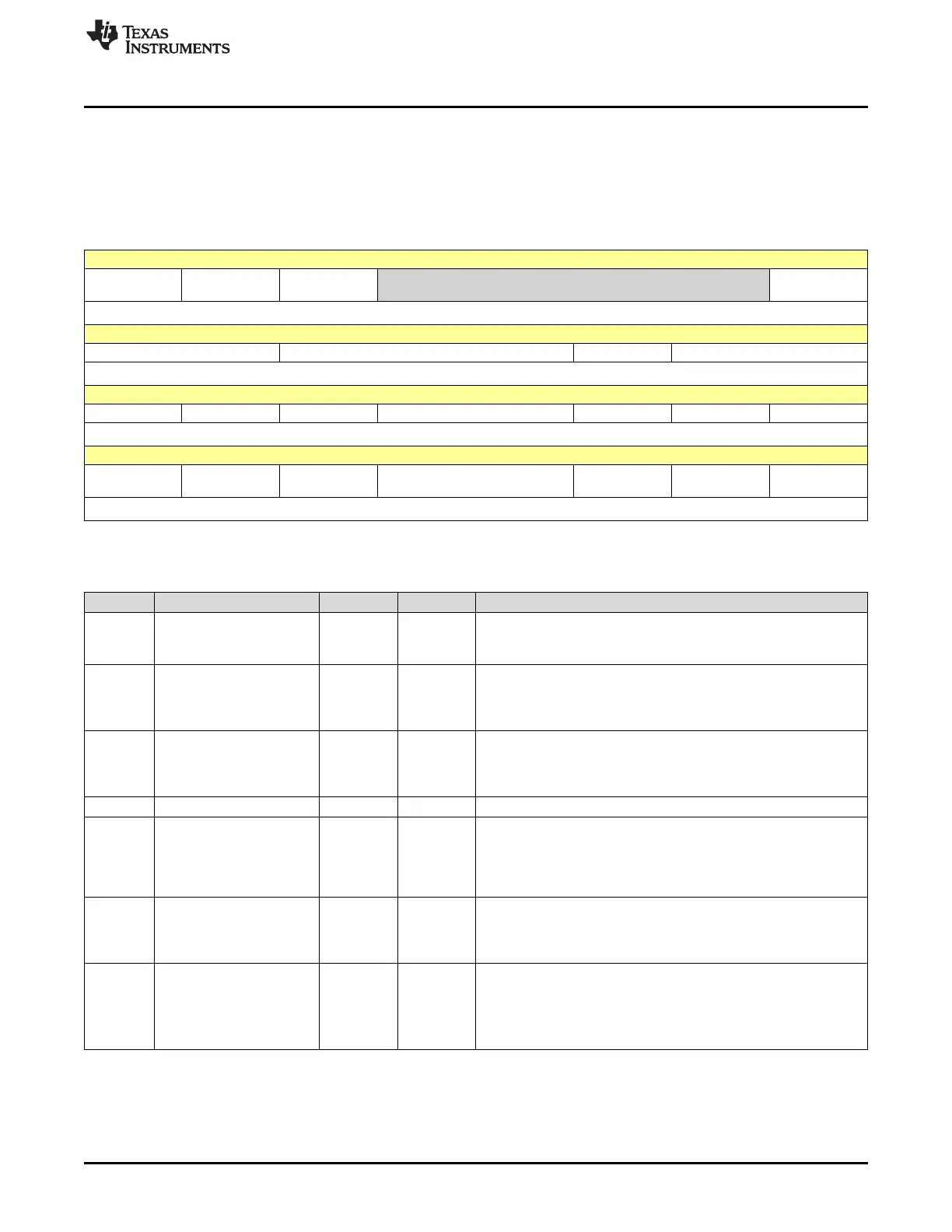

17.4.21 AES_CTRL Register (Offset = 50h) [reset = X]

AES_CTRL is shown in Figure 17-34 and described in Table 17-24.

Return to Summary Table.

Determines the mode of operation of the AES engine.

Figure 17-34. AES_CTRL Register

31 30 29 28 27 26 25 24

CONTEXT_RE

ADY

SAVE_CONTE

XT_READY

SAVE_CONTE

XT

RESERVED CCM_M

RO-1h RO-0h R/W-0h R-X R/W-0h

23 22 21 20 19 18 17 16

CCM_M CCM_L CCM GCM

R/W-0h R/W-0h R/W-0h R/W-0h

15 14 13 12 11 10 9 8

CBCMAC F9 F8 XTS CFB ICM CTR_WIDTH

R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h

7 6 5 4 3 2 1 0

CTR_WIDTH CTR MODE KEY_SIZE DIRECTION INPUT_READY OUTPUT_REA

DY

R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h RO-0h RO-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

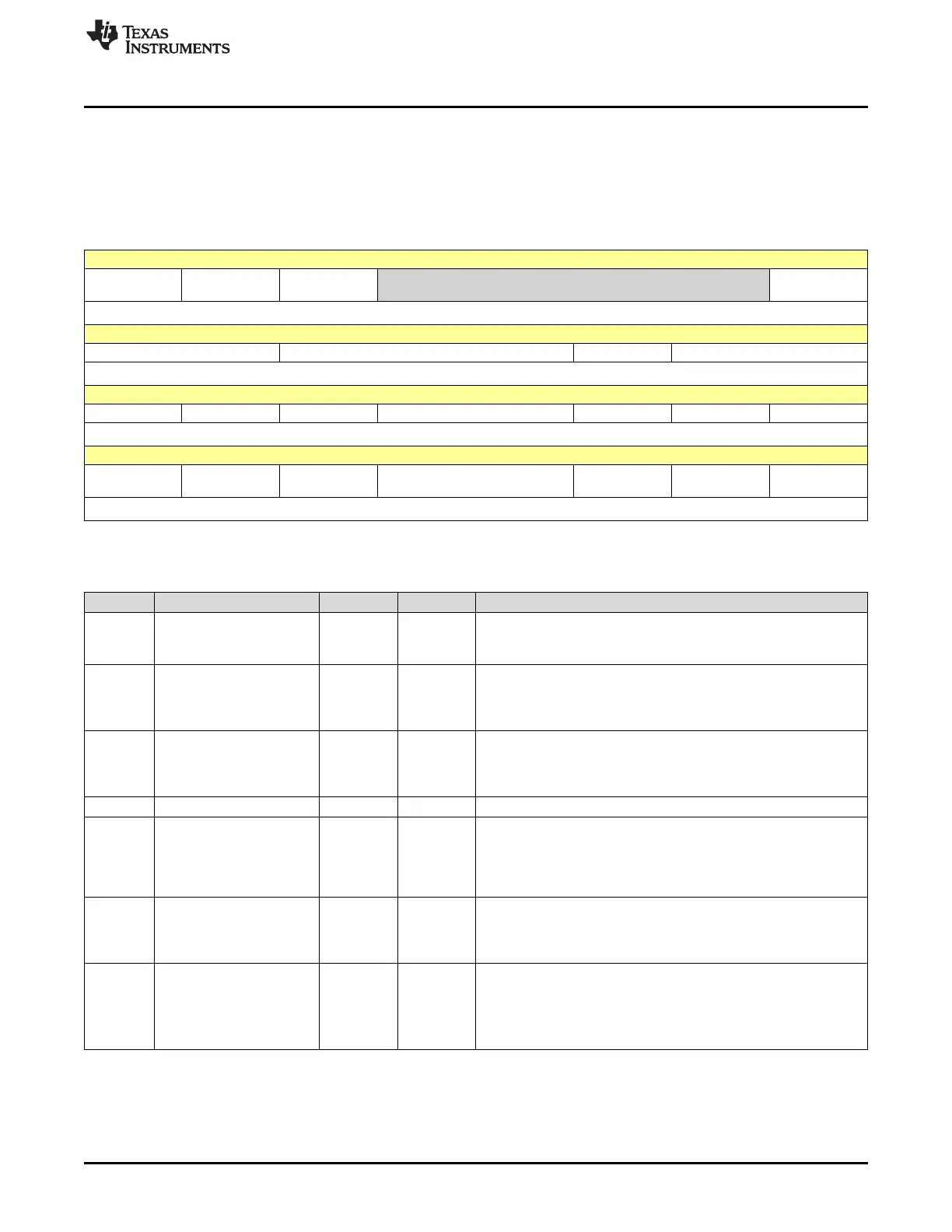

Table 17-24. AES_CTRL Register Field Descriptions

Bit Field Type Reset Description

31 CONTEXT_READY RO 1h

If 1, this read-only status bit indicates that the context data registers

can be overwritten, and the host is permitted to write the next

context.

30 SAVE_CONTEXT_READY RO 0h

If 1, this read-only status bit indicates that an AES authentication

TAG or IV blocks are available for the host to retrieve. This bit is only

asserted if the ‘save_context’ bit is set to 1. The bit is mutually

exclusive with the ‘context_ready’ bit.

29 SAVE_CONTEXT R/W 0h

This bit indicates that an authentication TAG or result IV must be

stored as a result context. If this bit is set, context output DMA or

interrupt are asserted if the operation is finished and related signals

are enabled.

28-25 RESERVED R X

24-22 CCM_M R/W 0h

Defines “M” that indicated the length of the authentication field for

CCM operations; the authentication field length equals two times (the

value of CCM-M plus one). The AES engine always returns a 128-bit

authentication field, of which the M least significant bytes are valid.

All values are supported.

21-19 CCM_L R/W 0h

Defines “L” that indicated the width of the length field for CCM

operations; the length field in bytes equals the value of CMM-L plus

one. Supported values for L are (programmed value): 2 (1), 4 (3) and

8 (7).

18 CCM R/W 0h

AES-CCM is selected; this is a combined mode, using AES for both

authentication and encryption. No additional mode selection is

required.

0h = Other mode selected

1h = CCM mode selected

Loading...

Loading...