www.ti.com

SD-HOST Registers

377

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

SD Host Controller Interface

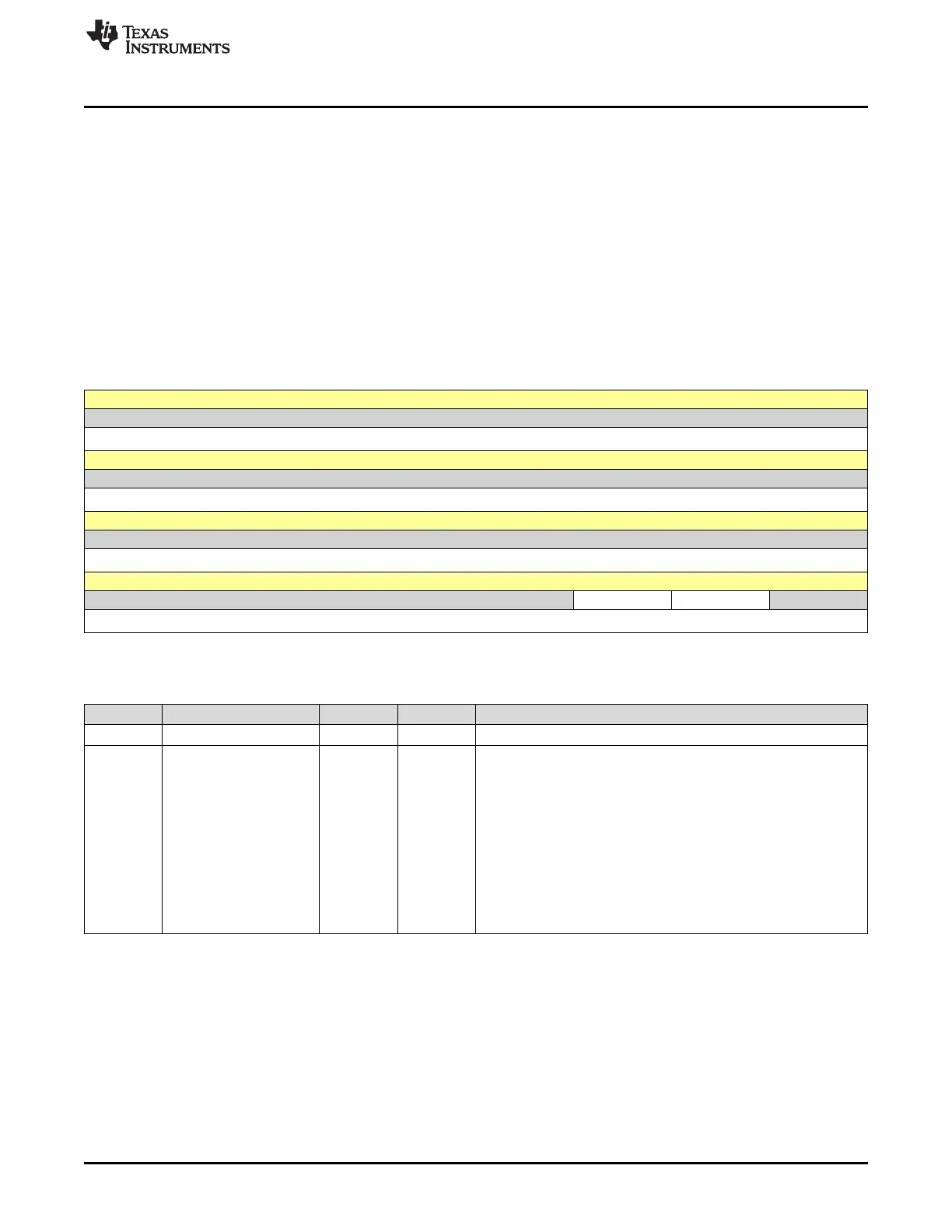

11.7.2 MMCHS_CON Register (Offset = 12Ch) [reset = 0h]

Configuration register

MMCHS_CON is shown in Figure 11-3 and described in Table 11-6.

Return to Summary Table.

This register is used to do the following:

• Select the functional mode for any card

• Send an initialization sequence to any card

• Enable the detection on the mmci_dat[1] signal of a card interrupt for SDIO cards only

• Configure specific data and command transfers for MMC cards only

• Configure the parameters related to the card detect and write protect input signals.

Figure 11-3. MMCHS_CON Register

31 30 29 28 27 26 25 24

RESERVED

R-0h

23 22 21 20 19 18 17 16

RESERVED

R-0h

15 14 13 12 11 10 9 8

RESERVED

R-0h

7 6 5 4 3 2 1 0

RESERVED HR INIT RESERVED

R-0h R/W-0h R/W-0h R-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

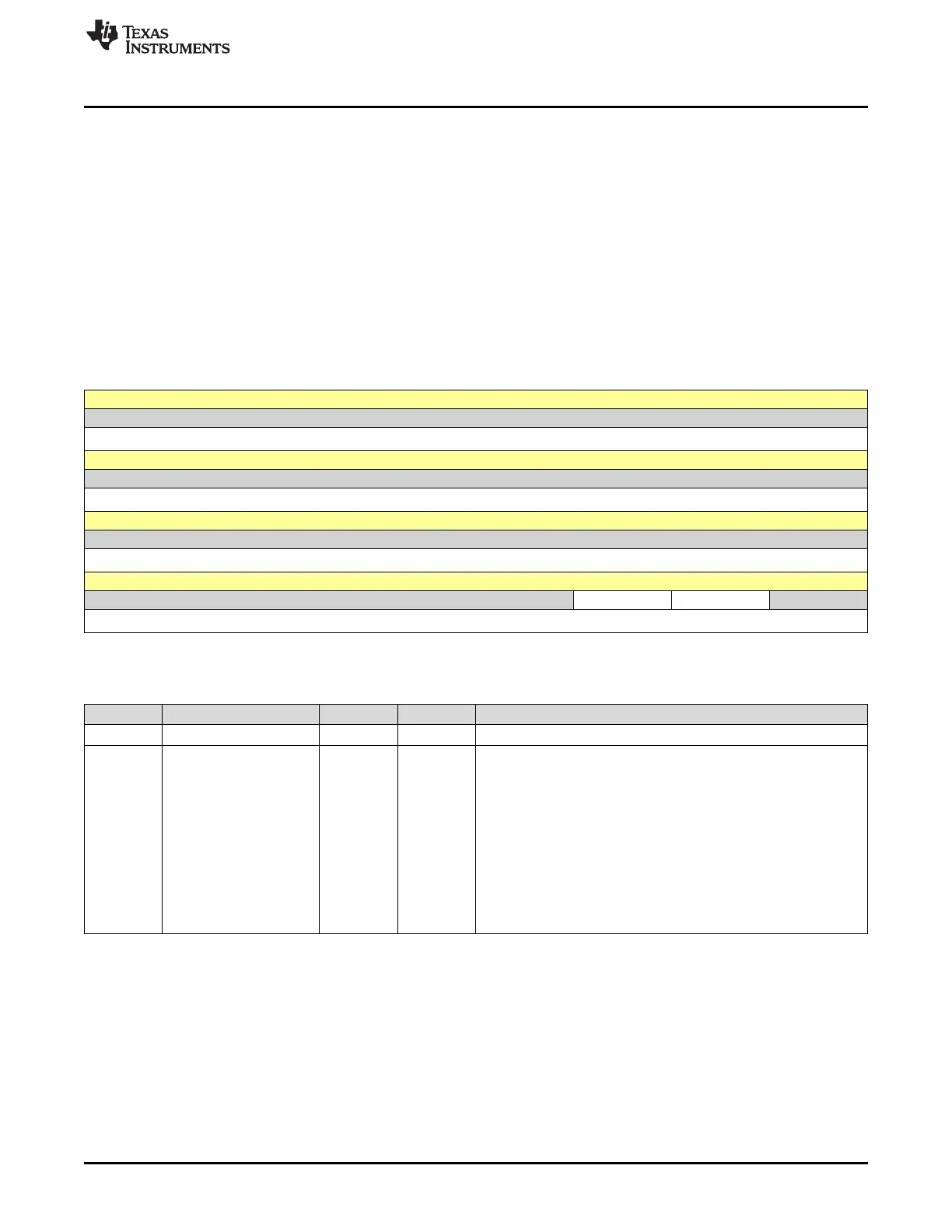

Table 11-6. MMCHS_CON Register Field Descriptions

Bit Field Type Reset Description

31-3 RESERVED R 0h

2 HR R/W 0h

Broadcast host response (only for MMC cards)

This register is used to force the host to generate a 48-bit response

for bc command type.

It can be used to terminate the interrupt mode by generating a

CMD40 response by the core. To have the host response to be

generated in open drain mode, the register MMCHS_CON[OD] must

be set to 1.

When MMCi.MMCHS_CON[12] CEATA bit is set to 1 and

MMCi.MMCHS_ARG set to 0x00000000, when writing 0x00000000

into MMCi.MMCHS_CMD register, the host controller performs a

'command completion signal disable' token (such as mmci_cmd line

held to 0 during 47 cycles followed by a 1).

Loading...

Loading...