SD-HOST Registers

www.ti.com

378

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

SD Host Controller Interface

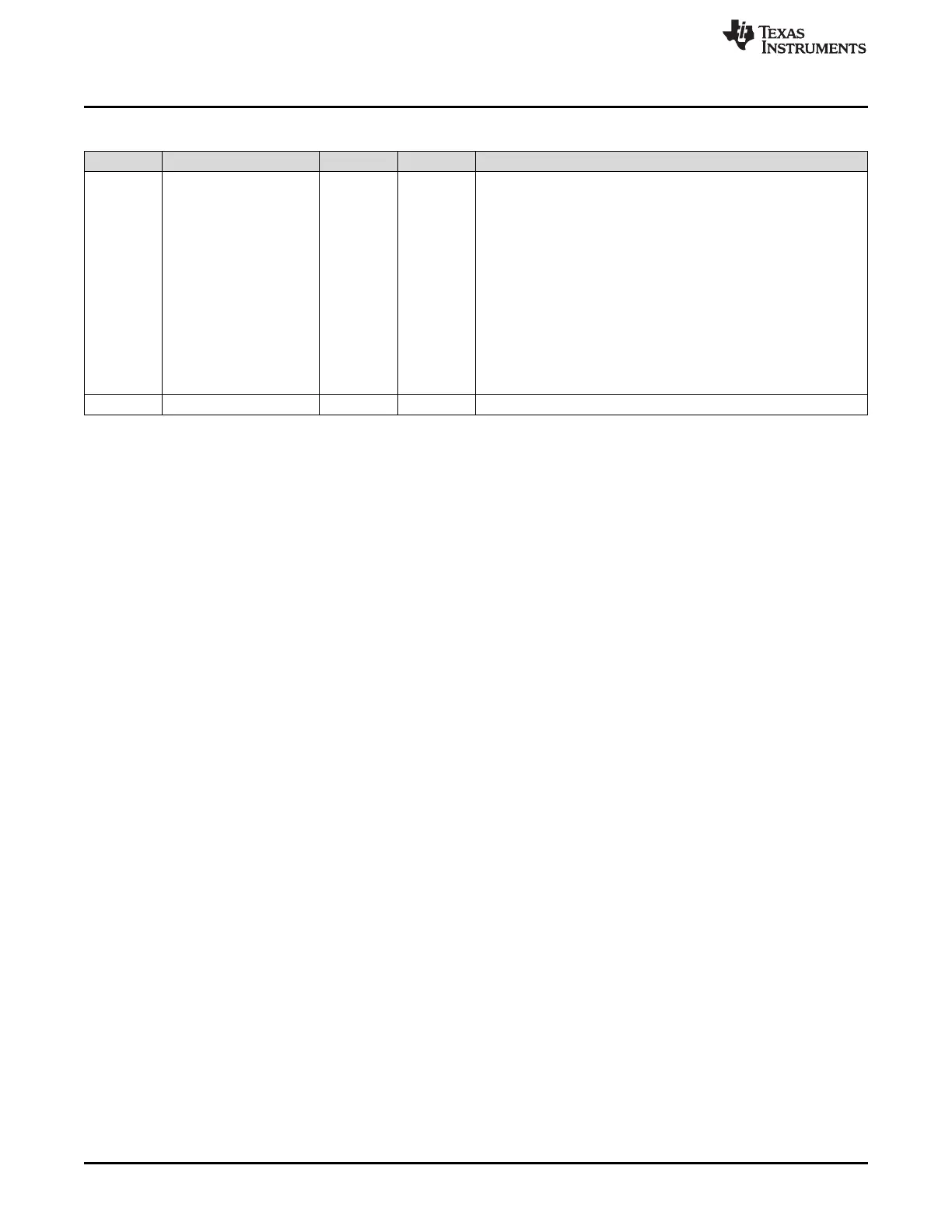

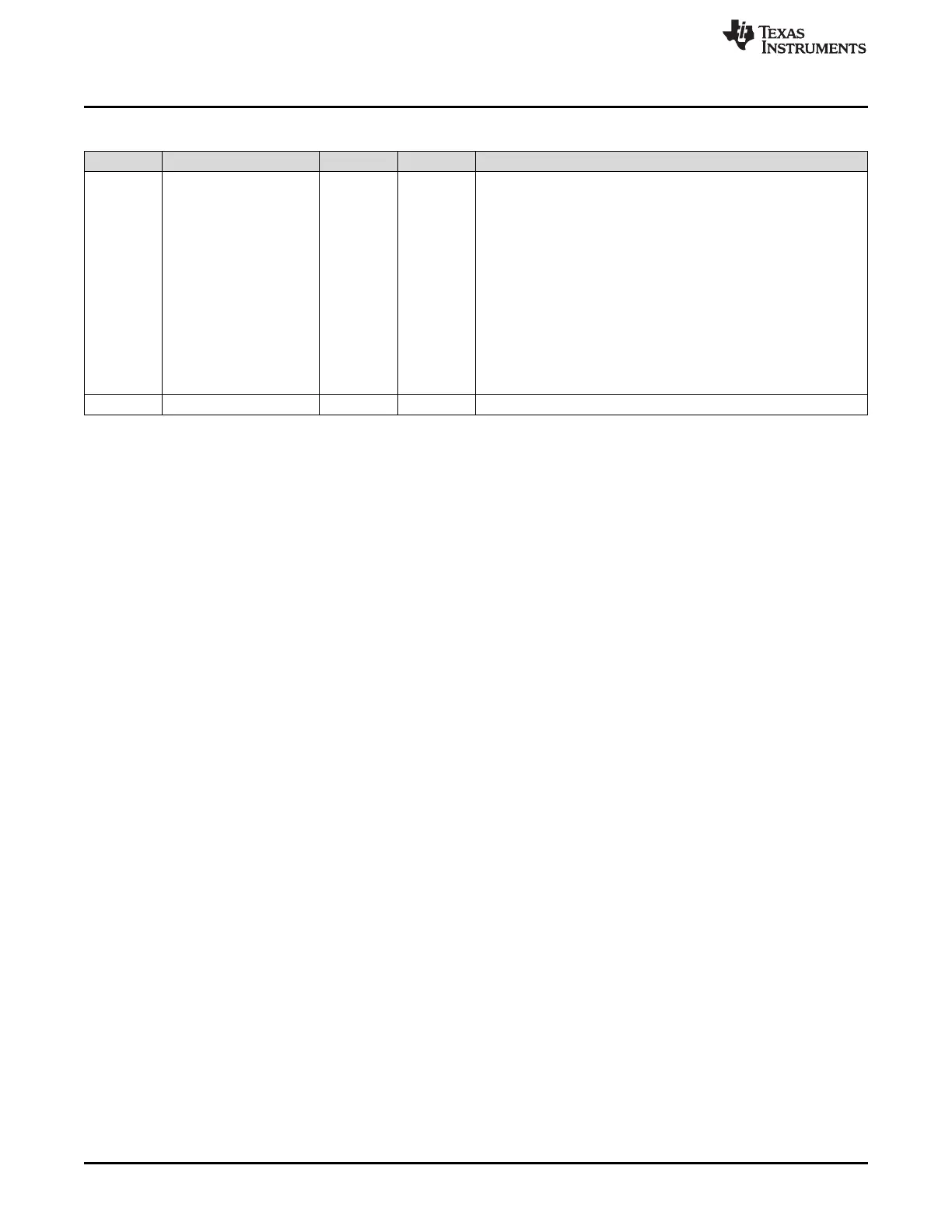

Table 11-6. MMCHS_CON Register Field Descriptions (continued)

Bit Field Type Reset Description

1 INIT R/W 0h

Send initialization stream (all cards)

When this bit is set to 1, and the card is idle, an initialization

sequence is sent to the card.

An initialization sequence consists of setting the mmci_cmd line to 1

during 80 clock cycles. The initialization sequence is mandatory - but

it is not required to do it through this bit - this bit makes it easier.

Clock divider (MMCi.MMCHS_SYSCTL[15:6] CLKD bits) should be

set to ensure that 80 clock periods are greater than 1ms.

Note: in this mode, there is no command sent to the card and no

response is expected. A command complete interrupt will be

generated once the initialization sequence is completed.

MMCi.MMCHS_STAT[0] CC bit can be polled.

0h = The host does not send an initialization sequence.

1h = The host sends an initialization sequence.

0 RESERVED R 0h

Loading...

Loading...