UART Registers

www.ti.com

182

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Universal Asynchronous Receivers/Transmitters (UARTs)

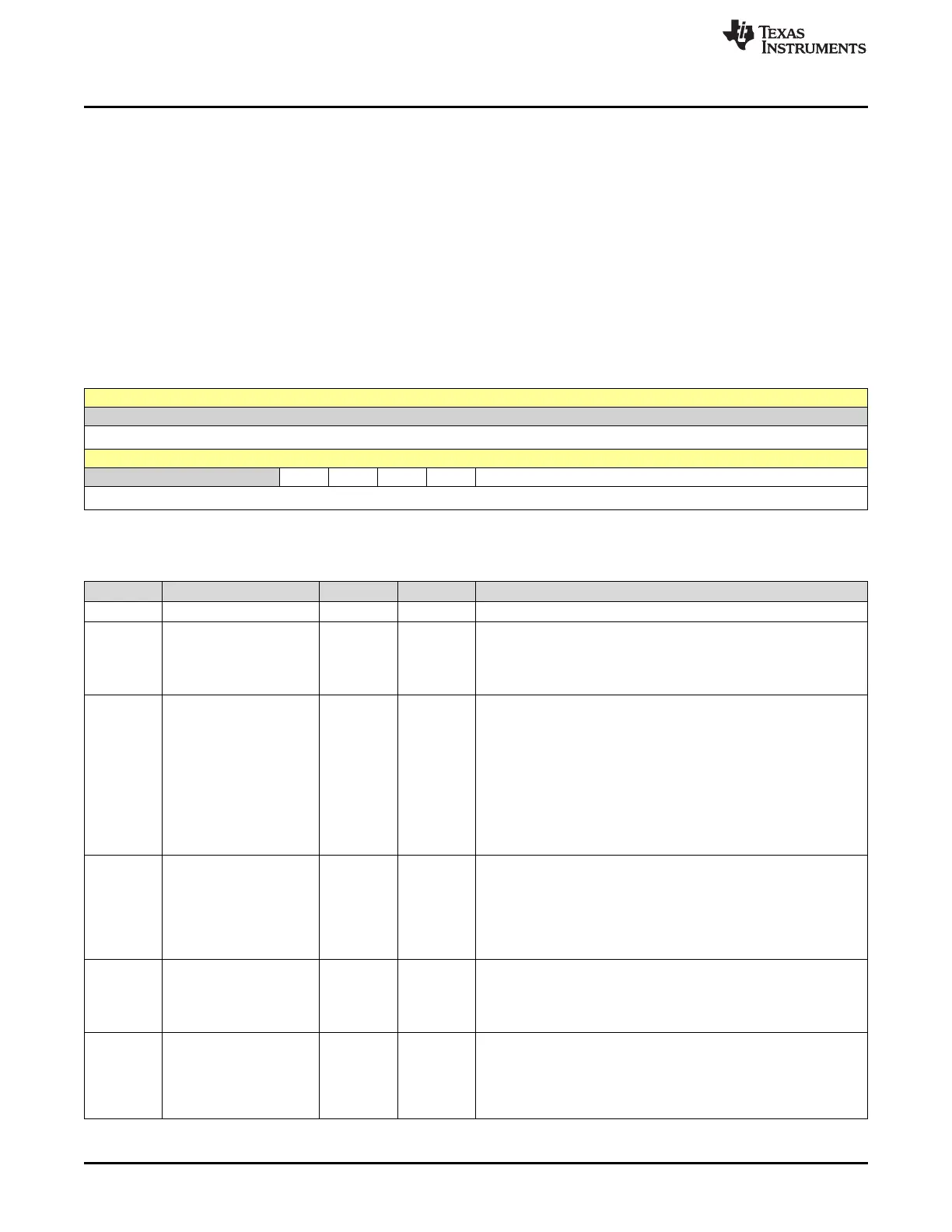

6.3.1 UARTDR Register (Offset = 0h) [reset = 0h]

UARTDR is shown in Figure 6-3 and described in Table 6-3.

Return to Summary Table.

This register is the data register (the interface to the FIFOs).

For transmitted data, if the FIFO is enabled, data written to this location is pushed onto the transmit FIFO.

If the FIFO is disabled, data is stored in the transmitter holding register (the bottom word of the transmit

FIFO). A write to this register initiates a transmission from the UART.

For received data, if the FIFO is enabled, the data byte and the 4-bit status (break, frame, parity, and

overrun) is pushed onto the 12-bit wide receive FIFO. If the FIFO is disabled, the data byte and status are

stored in the receiving holding register (the bottom word of the receive FIFO). The received data can be

retrieved by reading this register.

Figure 6-3. UARTDR Register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

RESERVED

R-0h

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RESERVED OE BE PE FE DATA

R-0h R-0h R-0h R-0h R-0h R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

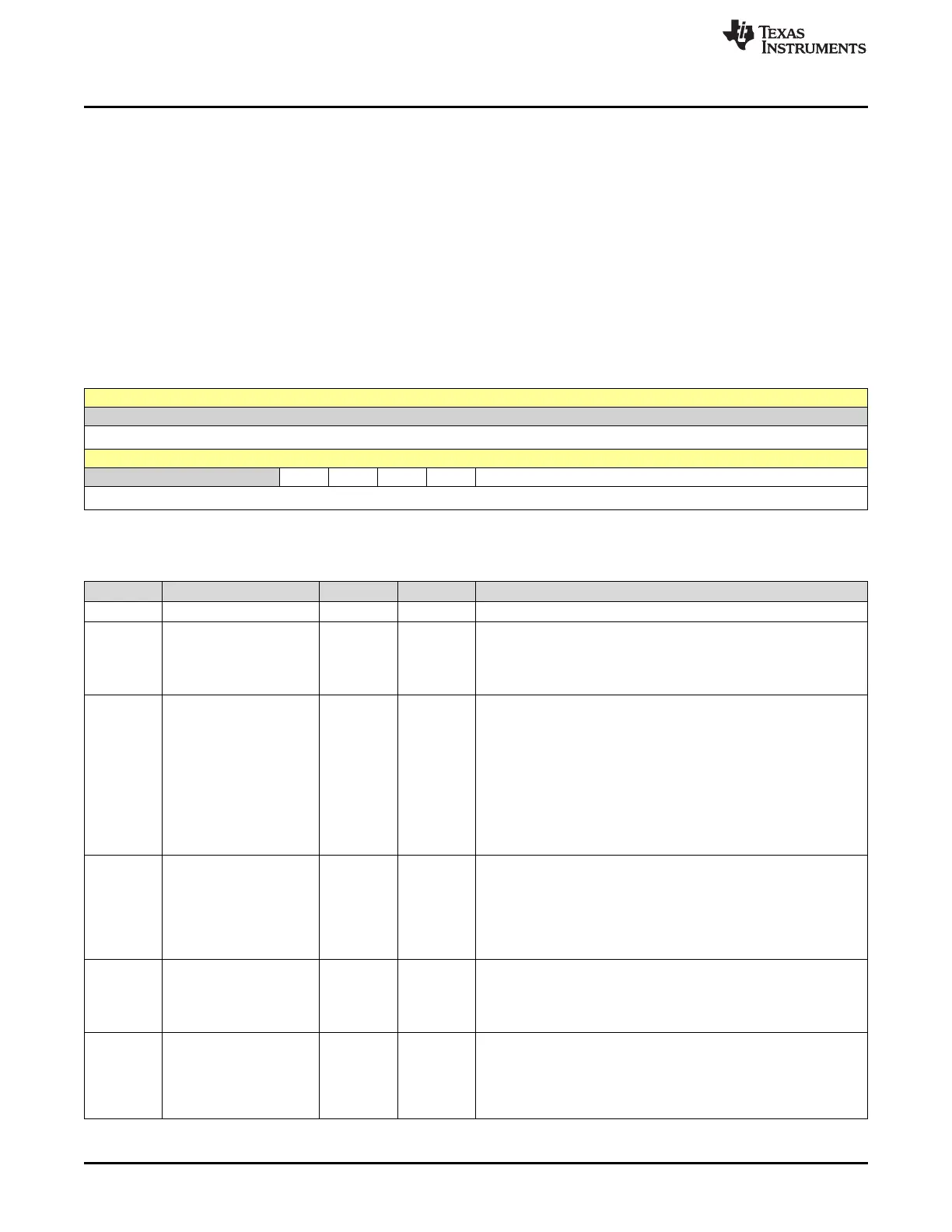

Table 6-3. UARTDR Register Field Descriptions

Bit Field Type Reset Description

31-12 RESERVED R 0h

11 OE R 0h

UART Overrun Error

0h = No data has been lost due to a FIFO overrun.

1h = New data was received when the FIFO was full, resulting in

data loss.

10 BE R 0h

UART Break Error

0h = No break condition has occurred

1h = A break condition has been detected, indicating that the receive

data input was held Low for longer than a full-word transmission time

(defined as start, data, parity, and stop bits).

In FIFO mode, this error is associated with the character at the top of

the FIFO. When a break occurs, only one 0 character is loaded into

the FIFO. The next character is only enabled after the received data

input goes to a 1 (marking state), and the next valid start bit is

received.

9 PE R 0h

UART Parity Error

0h = No parity error has occurred

1h = The parity of the received data character does not match the

parity defined by bits 2 and 7 of the UARTLCRH register.

In FIFO mode, this error is associated with the character at the top of

the FIFO.

8 FE R 0h

UART Framing Error

0h = No framing error has occurred

1h = The received character does not have a valid stop bit (a valid

stop bit is 1).

7-0 DATA R/W 0h

Data Transmitted or Received

Data that is to be transmitted through the UART is written to this

field.

When read, this field contains the data that was received by the

UART.

Loading...

Loading...