Analog Mux Control Registers

www.ti.com

588

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

I/O Pads and Pin Multiplexing

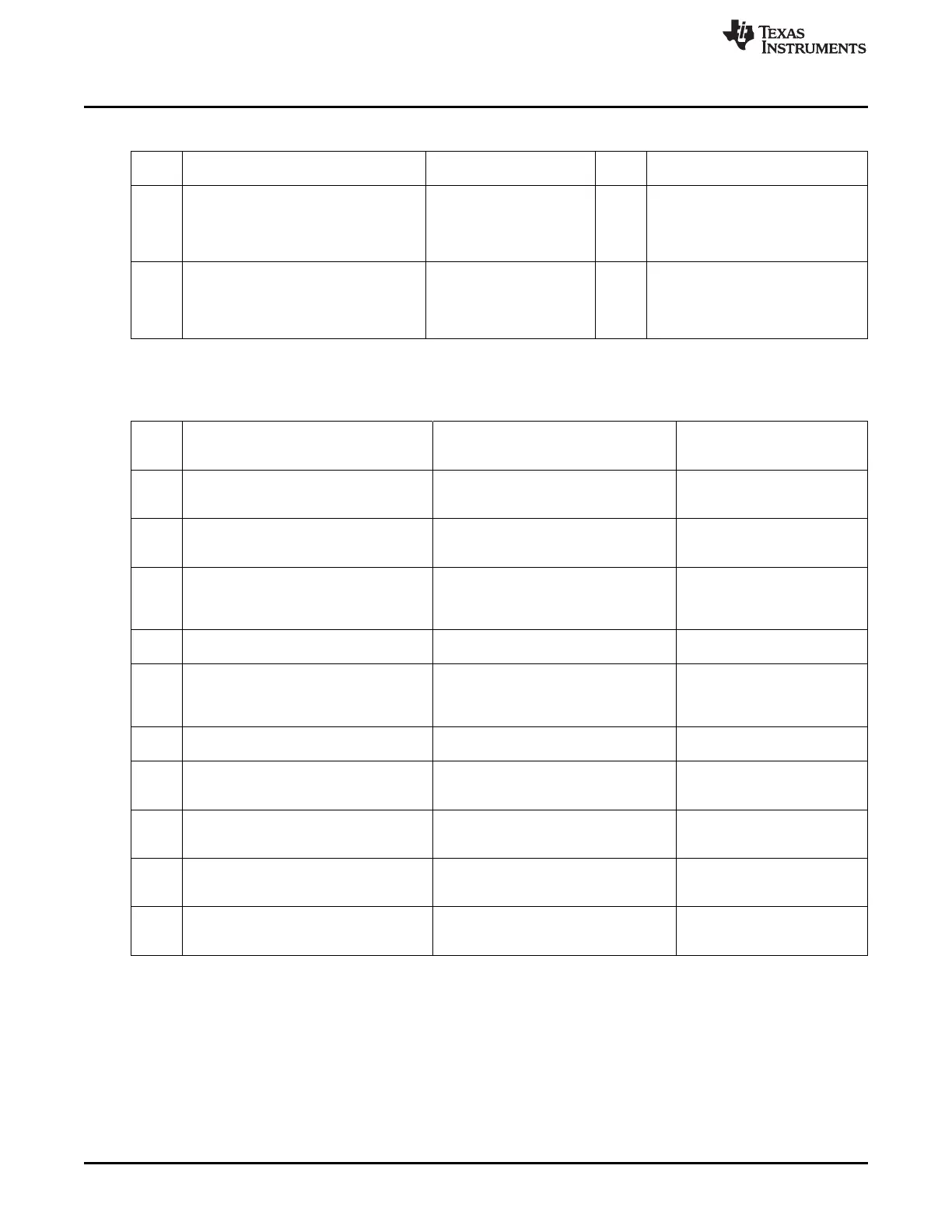

Table 16-4. Analog Mux Control Registers and Bits (continued)

Pin Analog Mux Control Register and Bit Write Values

Reset

Value

Notes

59

Register: ADCSPARE1

Address: 0x4402 E8B8

Bit [3]

0: ADC channel 2 path is not

enabled

1: ADC channel 2 path is

enabled

0

Digital I/O cell is always connected to

this pin, and application software

must make the digital I/O Hi-Z before

enabling analog mux, to prevent

damaging the device.

60

Register: ADCSPARE1

Address: 0x4402 E8B8

Bit [4]

0: ADC channel 3 path is not

enabled

1: ADC channel 3 path is

enabled

0

Digital I/O cell is always connected to

this pin, and application software

must make the digital I/O Hi-Z before

enabling analog mux, to prevent

damaging the device.

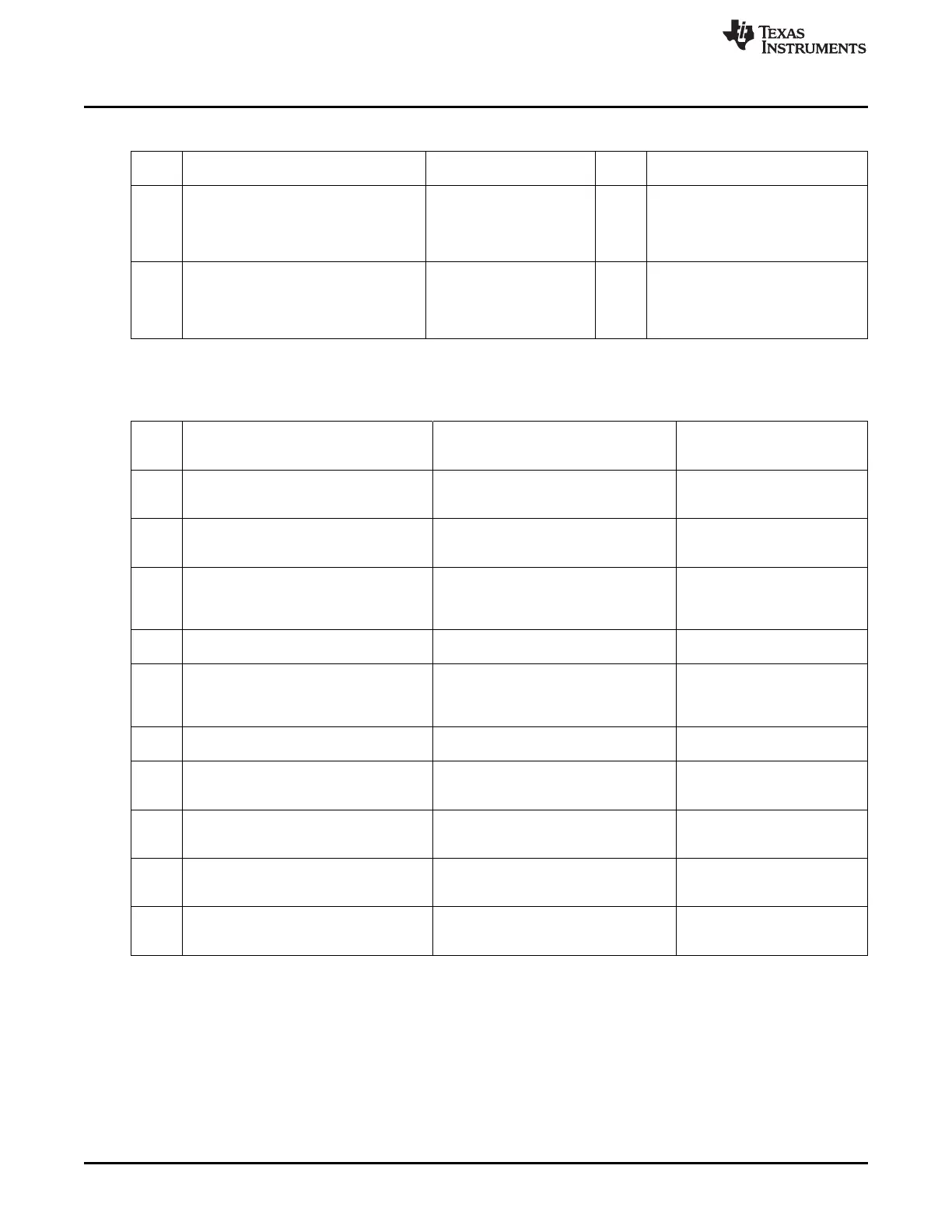

Table 16-5. Board-Level Behavior

Pin Board Level Configuration and Usage

Default State At First Powerup or

Forced Reset

State After Disabling Analog

Path (in ACTIVE, LPDS, HIB

power modes)

29

Connected to enable pin of RF switch

(ANTSEL1).

Other usage not recommended.

Analog is isolated.

Digital I/O cell is also isolated.

Determined by the I/O cell state,

like other digital I/Os.

30

Connected to enable pin of RF switch

(ANTSEL2).

Other usage not recommended.

Analog is isolated.

Digital I/O cell is also isolated.

Determined by the I/O cell state,

like other digital I/Os.

45

VDD_ANA2 (pin 47) must be shorted to

input supply rail.

Otherwise this pin will be driven by the

ANA2 DCDC

Analog is isolated.

Digital I/O cell is also isolated.

Determined by the I/O cell state,

like other digital I/Os.

50 Generic Input/Output

Analog is isolated.

Digital I/O cell is also isolated.

Determined by the I/O cell state,

like other digital I/Os.

52

This pin must have an external pullup of

100K to supply rail.

This pin must be used for output only

signals.

Analog is isolated.

Digital I/O cell is also isolated.

Determined by the I/O cell state,

like other digital I/Os.

53 Generic Input/Output

Analog is isolated.

Digital I/O cell is also isolated.

Determined by the I/O cell state,

like other digital I/Os.

57

Analog signal

(1.8-V absolute max. 1.46-V full scale)

ADC is isolated.

Digital I/O cell is directly connected but

Hi-Z.

Determined by the I/O cell state,

like other digital I/Os.

58

Analog signal

(1.8-V absolute max. 1.46-V full scale)

ADC is isolated.

Digital I/O cell is directly connected but

Hi-Z.

Determined by the I/O cell state,

like other digital I/Os.

59

Analog signal

(1.8-V absolute max. 1.46-V full scale)

ADC is isolated.

Digital I/O cell is directly connected but

Hi-Z.

Determined by the I/O cell state,

like other digital I/Os.

60

Analog signal

(1.8-V absolute max. 1.46-V full scale)

ADC is isolated.

Digital I/O cell is directly connected but

Hi-Z.

Determined by the I/O cell state,

like other digital I/Os.

Loading...

Loading...