www.ti.com

Register Description

137

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Direct Memory Access (DMA)

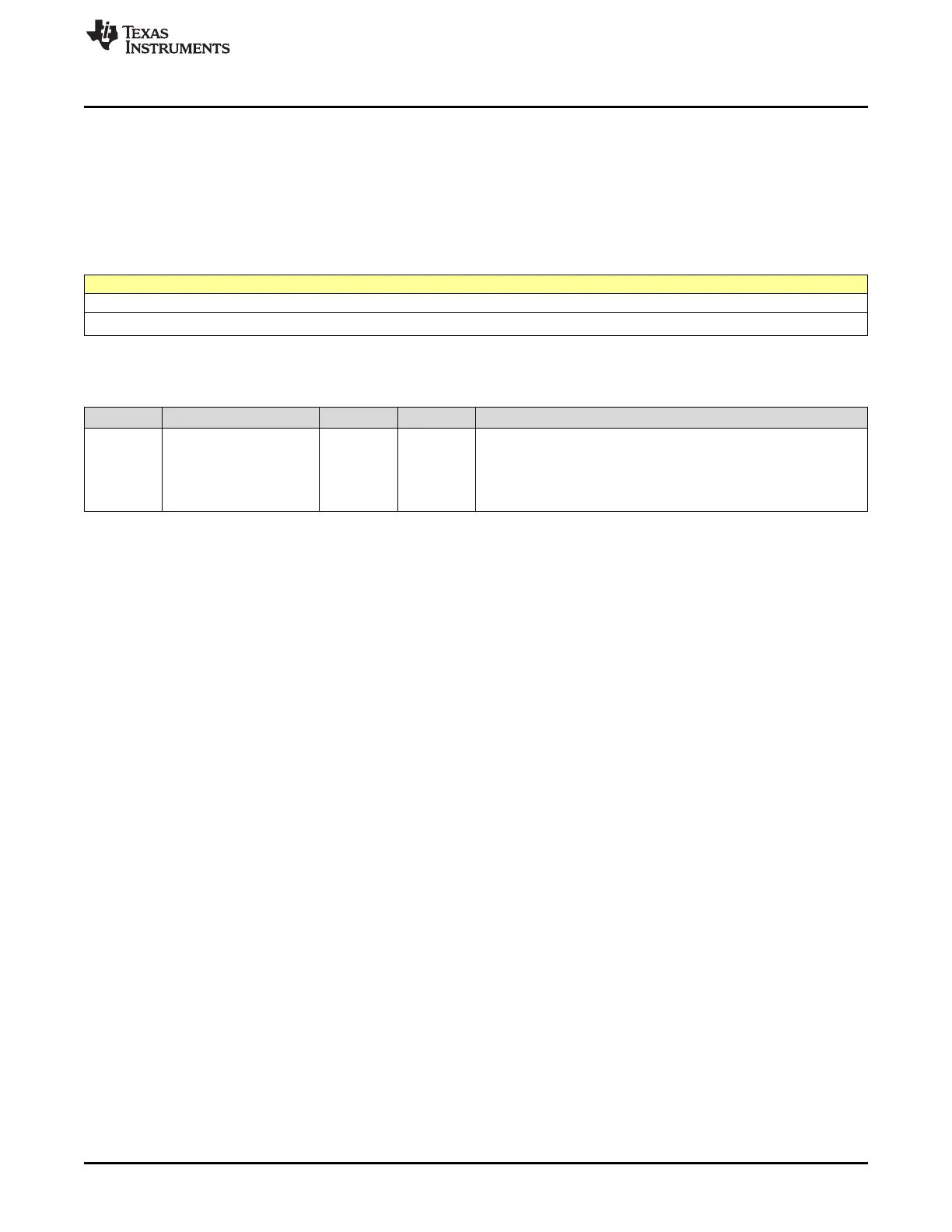

4.3.4.5 DMA_WAITSTAT Register (offset = 10h) [reset = 0h]

DMA_WAITSTAT is shown in Figure 4-11 and described in Table 4-15.

This Register indicates that the DMA channel is waiting on a request. A peripheral can hold off the DMA

from performing a single request until the peripheral is ready for a burst request to enhance the DMA

performance. The use of this feature is dependent on the design of the peripheral and is not controllable

by software in any way. This register cannot be read when the DMA controller is in the reset state.

Figure 4-11. DMA_WAITSTAT Register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

WAITREQ_n

R-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

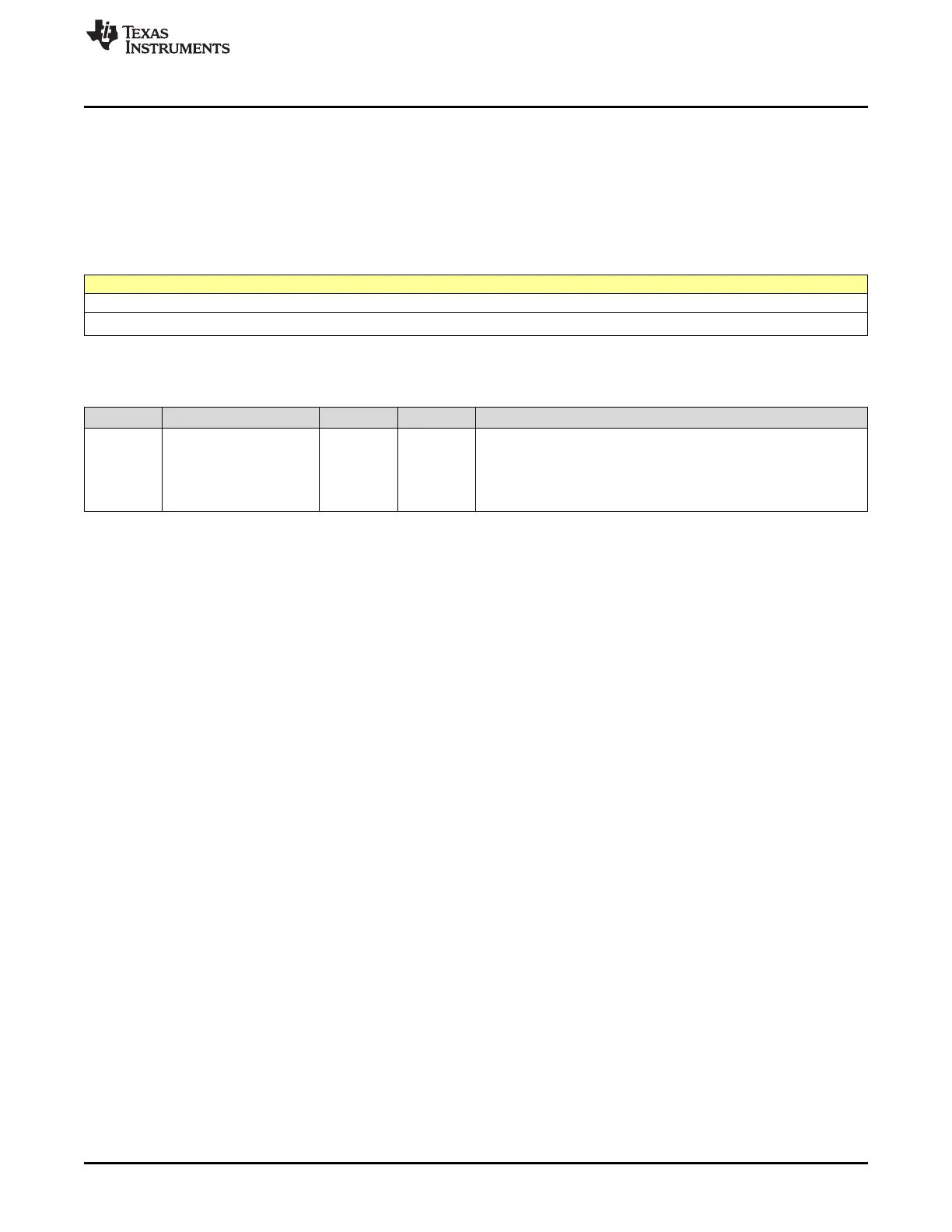

Table 4-15. DMA_WAITSTAT Register Field Descriptions

Bit Field Type Reset Description

31-0 WAITREQ_n R 0h Channel [n] Wait Status These bits provide the channel wait-on-

request status.

Bit 0 corresponds to channel 0.

0h = The corresponding channel is not waiting on a request.

1h = The corresponding channel is waiting on a request.

Loading...

Loading...