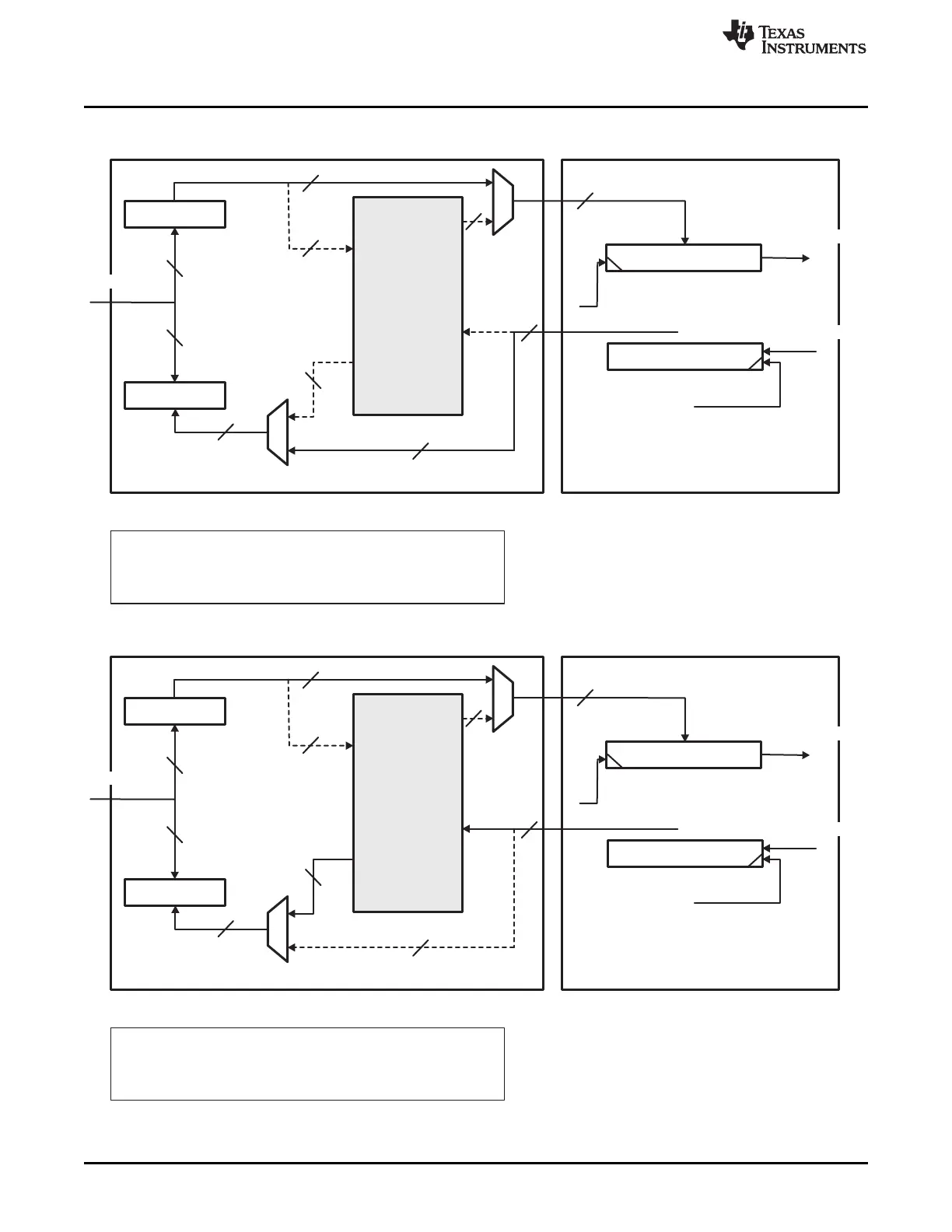

TX Register

RX Register

FIFO

FFNBYTE

Depth

TX Shift Register

RX Shift Register

TX Shift Clock

RX Shift Clock

SPI Domain

OCP Domain

Configuration:

MCSPI_CH(i)CONF[TRM] = 0 (Transmit/receive mode)

MCSPI_CH(i)CONF[FFER] = 1 (FIFO enabled on receive path)

MCSPI_CH(i)CONF[FFEW] = 0 (FIFO disabled on transmit path)

OCP Bus

SPI_D[n] (OUT)

SPI_D[n] (IN)

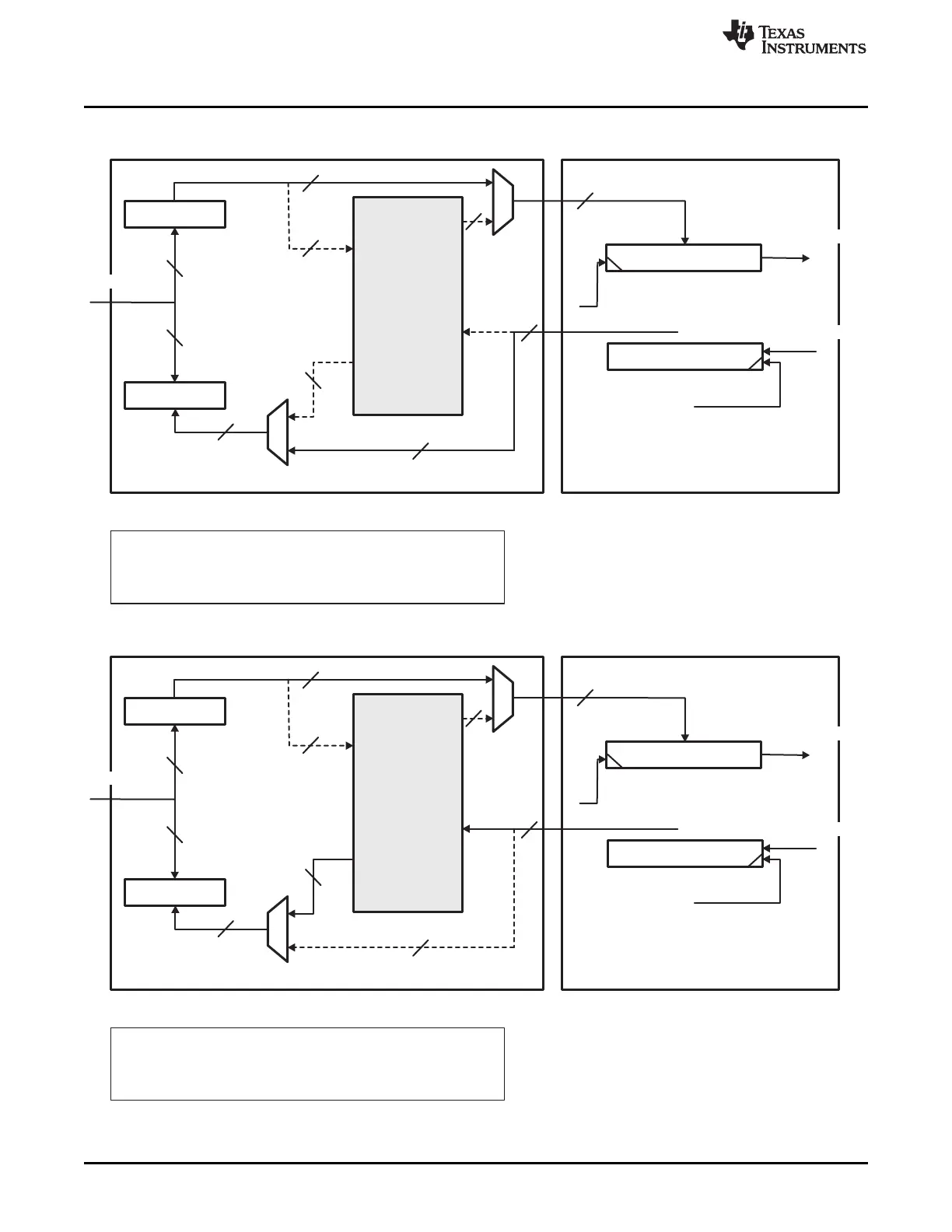

TX Register

RX Register

FIFO

FFNBYTE

Depth

TX Shift Register

RX Shift Register

TX Shift Clock

RX Shift Clock

SPI Domain

OCP Domain

Configuration:

MCSPI_CH(i)CONF[TRM ]= 0 (Transmit/receive mode)

MCSPI_CH(i)CONF[FFER] = 0 (FIFO disabled on receive path)

MCSPI_CH(i)CONF[FFEW] = 0 (FIFO disabled on transmit path)

OCP Bus

SPI_D[n] (OUT)

SPI_D[n] (IN)

Functional Description

www.ti.com

274

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

SPI (Serial Peripheral Interface)

Figure 8-7. Transmit/Receive Mode With No FIFO Used

Figure 8-8. Transmit/Receive Mode With Only Receive FIFO Enabled

Loading...

Loading...