www.ti.com

UART Registers

191

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Universal Asynchronous Receivers/Transmitters (UARTs)

6.3.7 UARTCTL Register (Offset = 30h) [reset = 300h]

UARTCTL is shown in Figure 6-9 and described in Table 6-9.

Return to Summary Table.

The UARTCTL register is the control register. All the bits are cleared on reset except for the Transmit

Enable (TXE) and Receive Enable (RXE) bits, which are set.

To enable the UART module, the UARTEN bit must be set. If software requires a configuration change in

the module, the UARTEN bit must be cleared before the configuration changes are written. If the UART is

disabled during a transmit or receive operation, the current transaction is completed prior to the UART

stopping.

NOTE: The UARTCTL register should not be changed while the UART is enabled or else the results

are unpredictable. The following sequence is recommended for making changes to the

UARTCTL register.

1. Disable the UART.

2. Wait for the end of transmission or reception of the current character.

3. Flush the transmit FIFO by clearing bit 4 (FEN) in the line control register

(UARTLCRH).

4. Reprogram the control register.

5. Enable the UART.

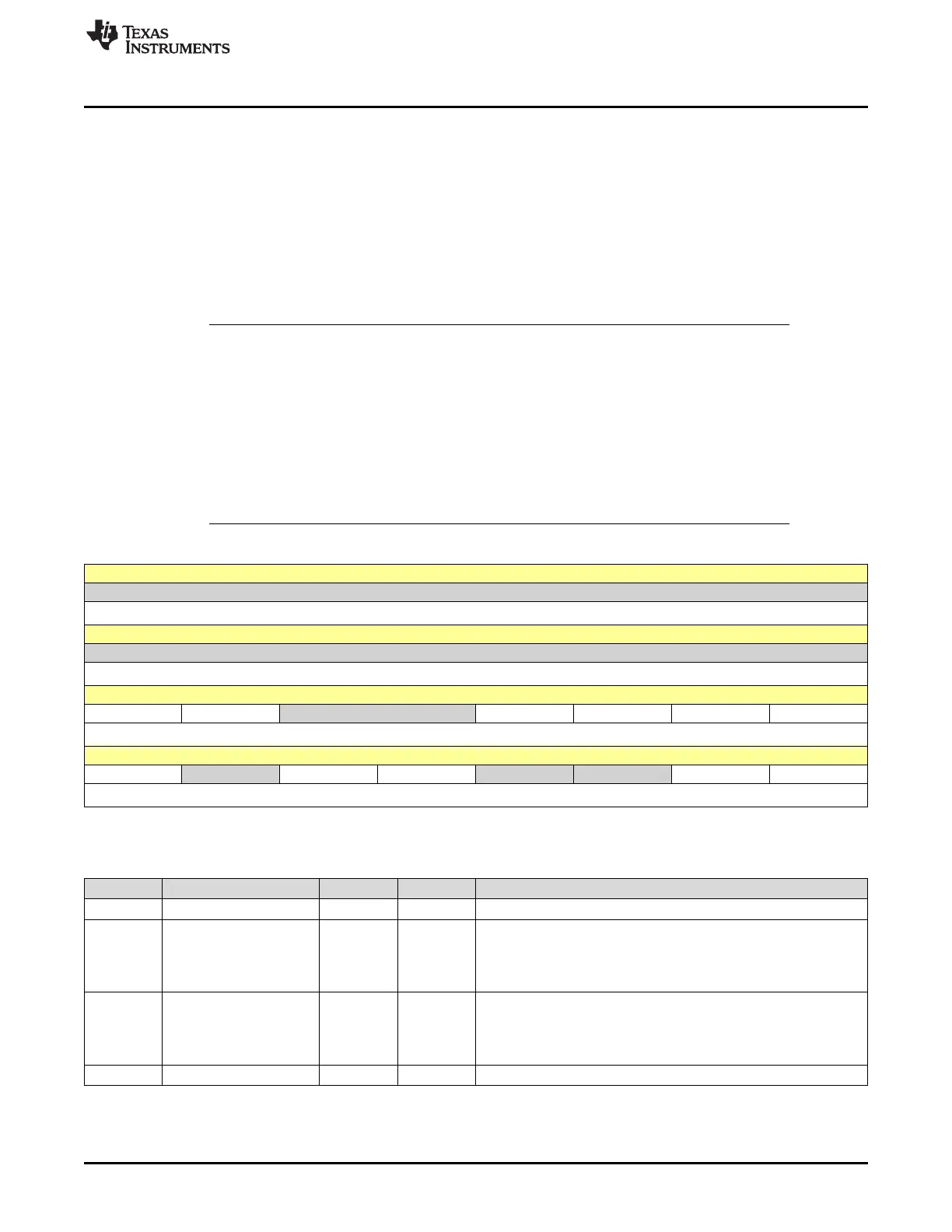

Figure 6-9. UARTCTL Register

31 30 29 28 27 26 25 24

RESERVED

R-0h

23 22 21 20 19 18 17 16

RESERVED

R-0h

15 14 13 12 11 10 9 8

CTSEN RTSEN RESERVED RTS DTR RXE TXE

R/W-0h R/W-0h R-0h R/W-0h R/W-0h R/W-1h R/W-1h

7 6 5 4 3 2 1 0

LBE RESERVED HSE EOT RESERVED RESERVED SIREN UARTEN

R/W-0h R-0h R/W-0h R/W-0h R-0h R-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

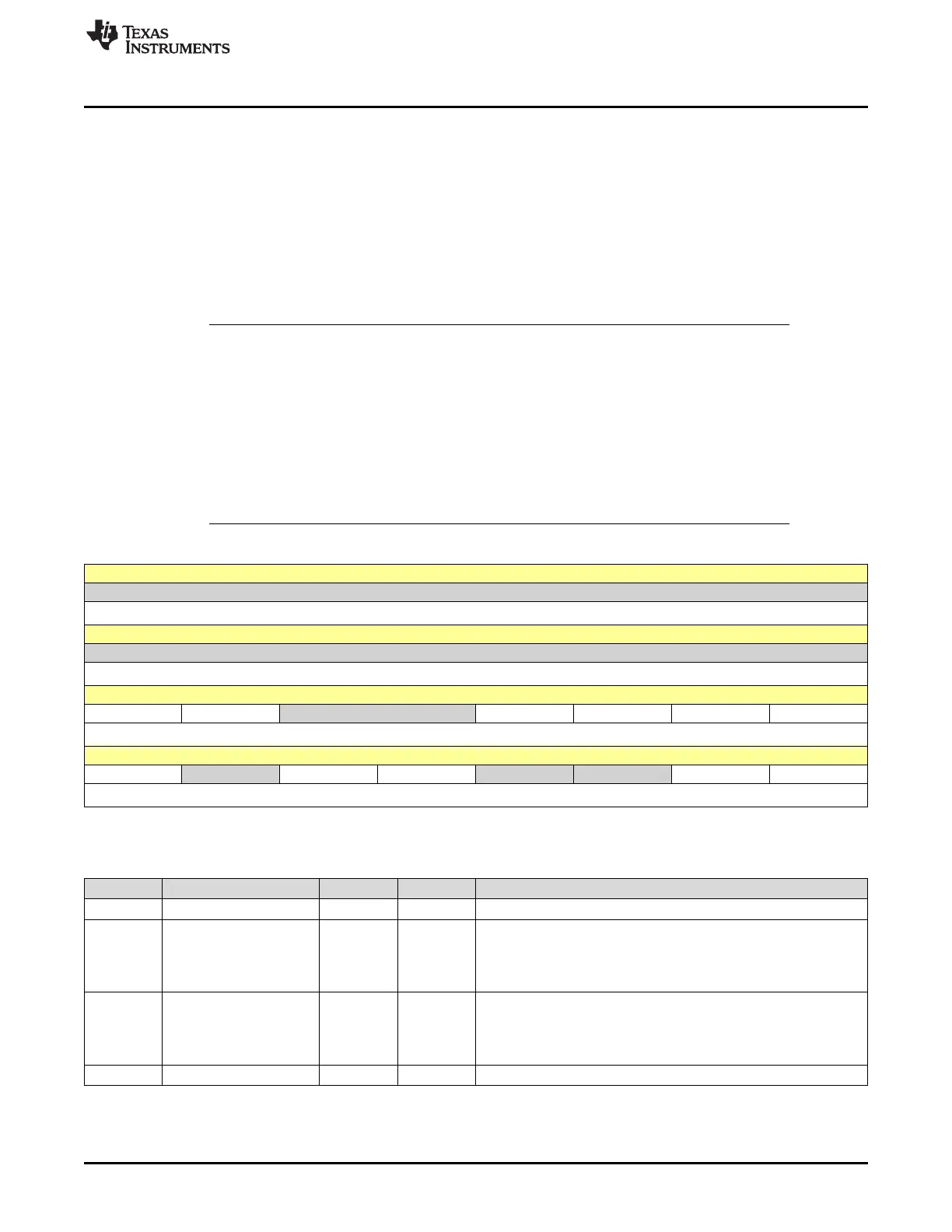

Table 6-9. UARTCTL Register Field Descriptions

Bit Field Type Reset Description

31-16 RESERVED R 0h

15 CTSEN R/W 0h

Enable Clear To Send

0h = CTS hardware flow control is disabled.

1h = CTS hardware flow control is enabled. Data is only transmitted

when the U1CTS signal is asserted.

14 RTSEN R/W 0h

Enable Request to Send

0h = RTS hardware flow control is disabled.

1h = RTS hardware flow control is enabled. Data is only requested

(by asserting U1RTS) when the receive FIFO has available entries.

13-12 RESERVED R 0h

Loading...

Loading...