AES Registers

www.ti.com

648

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Advance Encryption Standard Accelerator (AES)

17.4.24 AES_AUTH_LENGTH Register (Offset = 5Ch) [reset = 0h]

AES_AUTH_LENGTH is shown in Figure 17-37 and described in Table 17-27.

Return to Summary Table.

AAD data length. The authentication length register store the authentication data length in bytes for

combined modes only (GCM or CCM).

Supported AAD-lengths for CCM are from 0 to (2

16

– 2

8

) bytes. For GCM any value up to (2

32

– 1) bytes

can be used. Once processing with this context is started, this length decrements to zero.

A write to this register triggers the engine to start using this context for GCM and CCM. For XTS this

register is optionally used to load ‘j’. Loading of ‘j’ is only required if ‘j’ != 0. ‘j’ is a 28-bit value and must be

written to bits [31-4] of this register. ‘j’ represents the sequential number of the 128-bit block inside the

data unit. For the first block in a unit, this value is zero. It is not required to provide a ‘j’ for each new data

block within a unit. It is possible to start with a ‘j’ unequal to zero; refer to Table 4? Is this reference to

Table 4 valid? If so, need cross-ref. for more details. For a Host read operation, these registers return all-

zeroes.

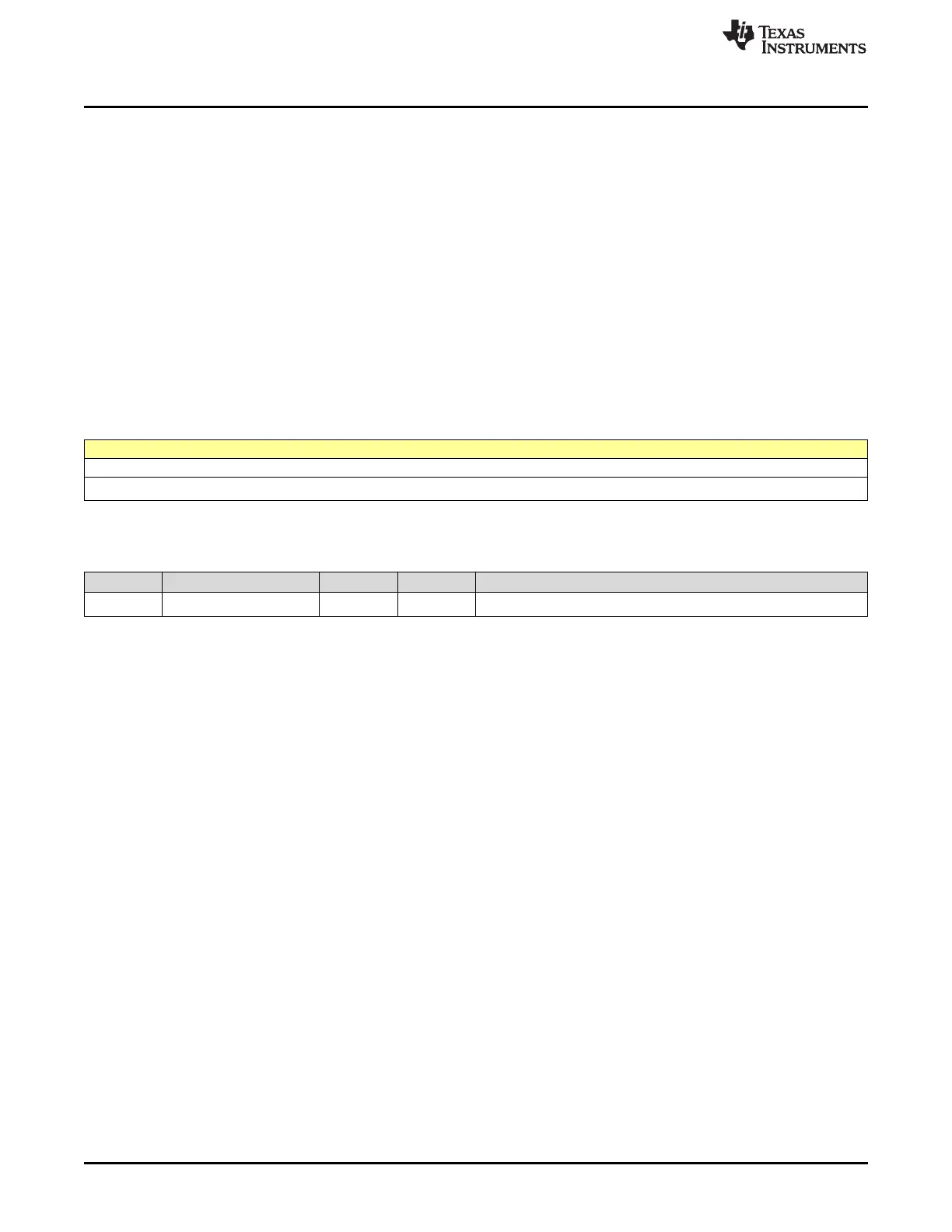

Figure 17-37. AES_AUTH_LENGTH Register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

AUTH

R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

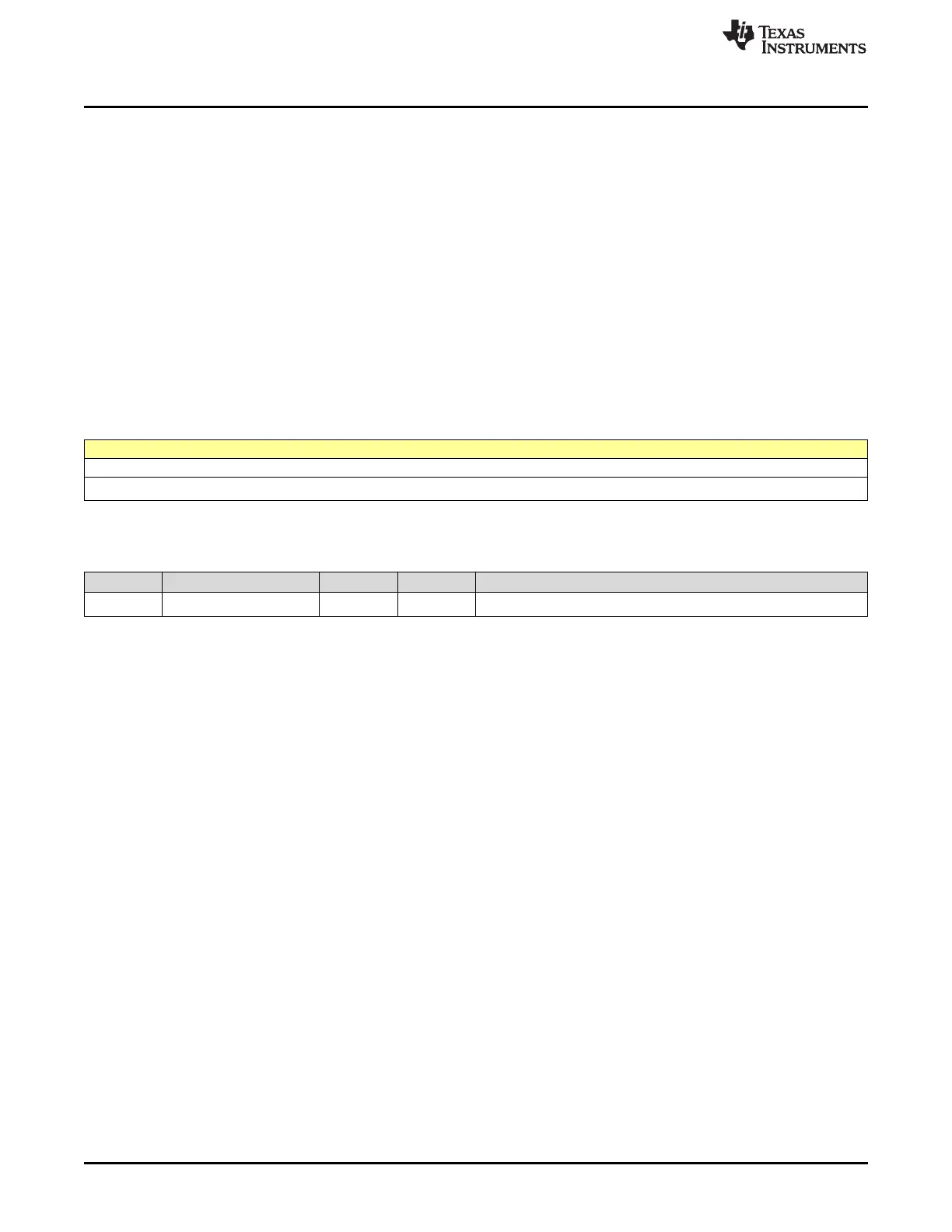

Table 17-27. AES_AUTH_LENGTH Register Field Descriptions

Bit Field Type Reset Description

31-0 AUTH R/W 0h

Data

Loading...

Loading...