Register Map

www.ti.com

102

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Cortex

®

-M4 Peripherals

3.3.1.16 CFGCTRL Register (Offset = D14h) [reset = 200h]

CFGCTRL is shown in Figure 3-16 and described in Table 3-19.

Return to Summary Table.

The CFGCTRL register controls entry to Thread mode and enables:

• The handlers for NMI, hard fault and faults escalated by the FAULTMASK register to ignore bus faults

• Trapping of divide by zero and unaligned accesses

• Access to the SWTRIG register by unprivileged software.

NOTE: This register can only be accessed from privileged mode.

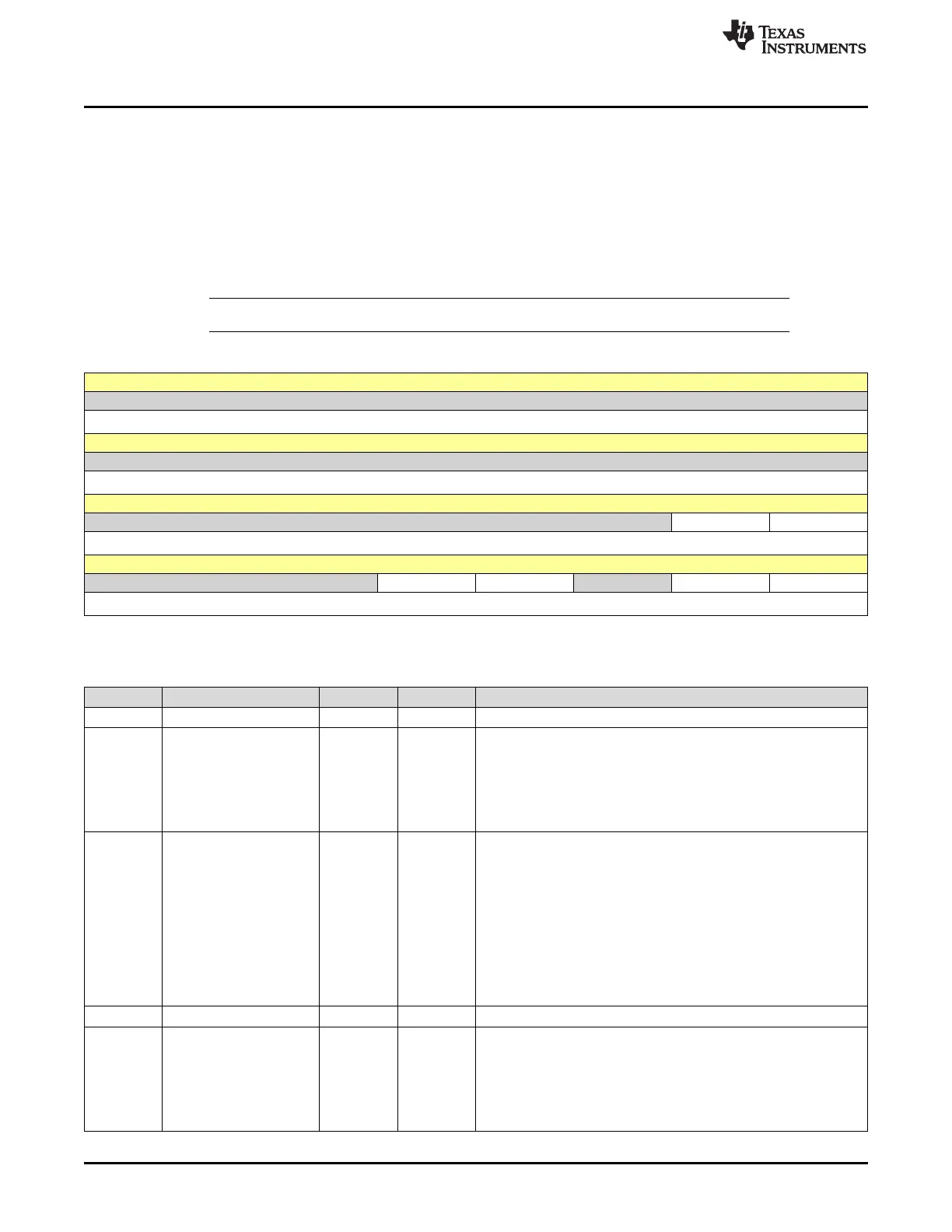

Figure 3-16. CFGCTRL Register

31 30 29 28 27 26 25 24

RESERVED

R-0h

23 22 21 20 19 18 17 16

RESERVED

R-0h

15 14 13 12 11 10 9 8

RESERVED STKALIGN BFHFMIGN

R-0h R/W-1h R/W-0h

7 6 5 4 3 2 1 0

RESERVED DIV0 UNALIGNED RESERVED MANIPEND BASETHR

R-0h R/W-0h R/W-0h R-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

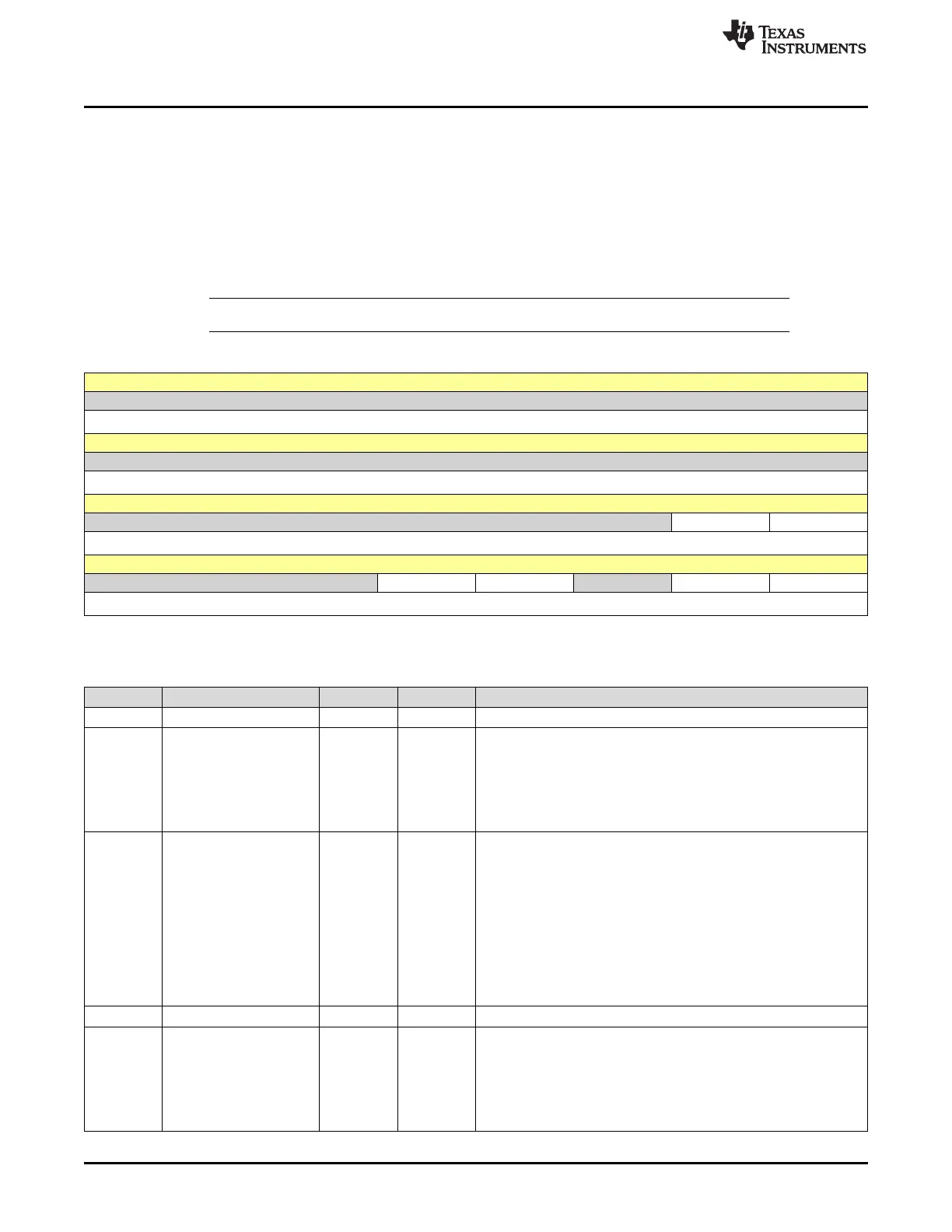

Table 3-19. CFGCTRL Register Field Descriptions

Bit Field Type Reset Description

31-10 RESERVED R 0h

9 STKALIGN R/W 1h

Stack Alignment on Exception Entry

On exception entry, the processor uses bit 9 of the stacked PSR to

indicate the stack alignment. On return from the exception, it uses

this stacked bit to restore the correct stack alignment.

0h = The stack is 4-byte aligned.

1h = The stack is 8-byte aligned.

8 BFHFMIGN R/W 0h

Ignore Bus Fault in NMI and Fault

This bit enables handlers with priority -1 or -2 to ignore data bus

faults caused by load and store instructions. The setting of this bit

applies to the hard fault, NMI, and FAULTMASK-escalated handlers.

Set this bit only when the handler and its data are in absolutely safe

memory. The normal use of this bit is to probe system devices and

bridges to detect control path problems and fix them.

0h = Data bus faults caused by load and store instructions cause a

lock-up.

1h = Handlers running at priority -1 and -2 ignore data bus faults

caused by load and store instructions.

7-5 RESERVED R 0h

4 DIV0 R/W 0h

Trap on Divide by 0

This bit enables faulting or halting when the processor executes an

SDIV or UDIV instruction with a divisor of 0.

0h = Do not trap on divide by 0. A divide by zero returns a quotient

of 0.

1h = Trap on divide by 0.

Loading...

Loading...