www.ti.com

UART Registers

189

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Universal Asynchronous Receivers/Transmitters (UARTs)

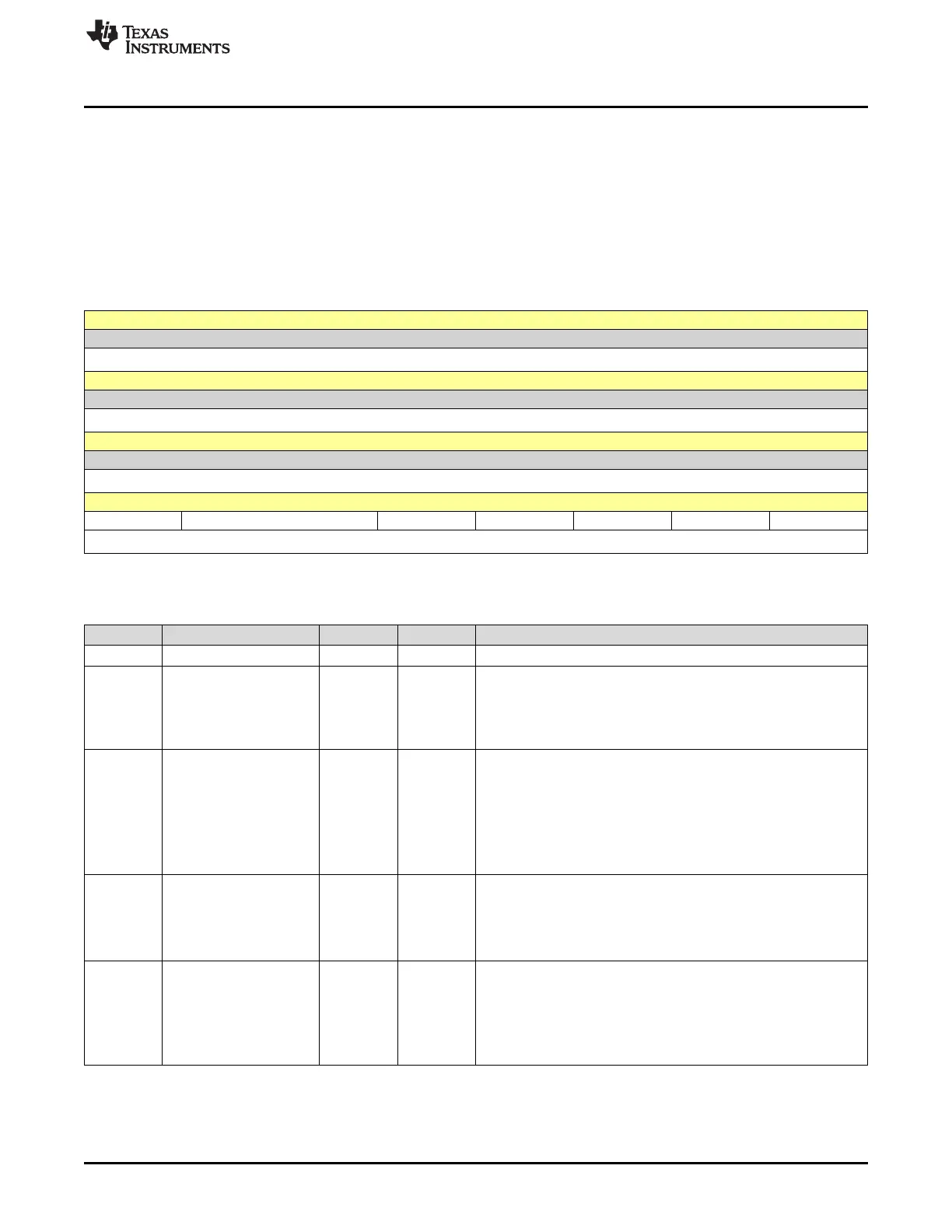

6.3.6 UARTLCRH Register (Offset = 2Ch) [reset = 0h]

UARTLCRH is shown in Figure 6-8 and described in Table 6-8.

Return to Summary Table.

The UARTLCRH register is the line control register. Serial parameters such as data length, parity, and

stop bit selection are implemented in this register.

When updating the baud-rate divisor (UARTIBRD or UARTIFRD), the UARTLCRH register must also be

written. The write strobe for the baud-rate divisor registers is tied to the UARTLCRH register.

Figure 6-8. UARTLCRH Register

31 30 29 28 27 26 25 24

RESERVED

R-0h

23 22 21 20 19 18 17 16

RESERVED

R-0h

15 14 13 12 11 10 9 8

RESERVED

R-0h

7 6 5 4 3 2 1 0

SPS WLEN FEN STP2 EPS PEN BRK

R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

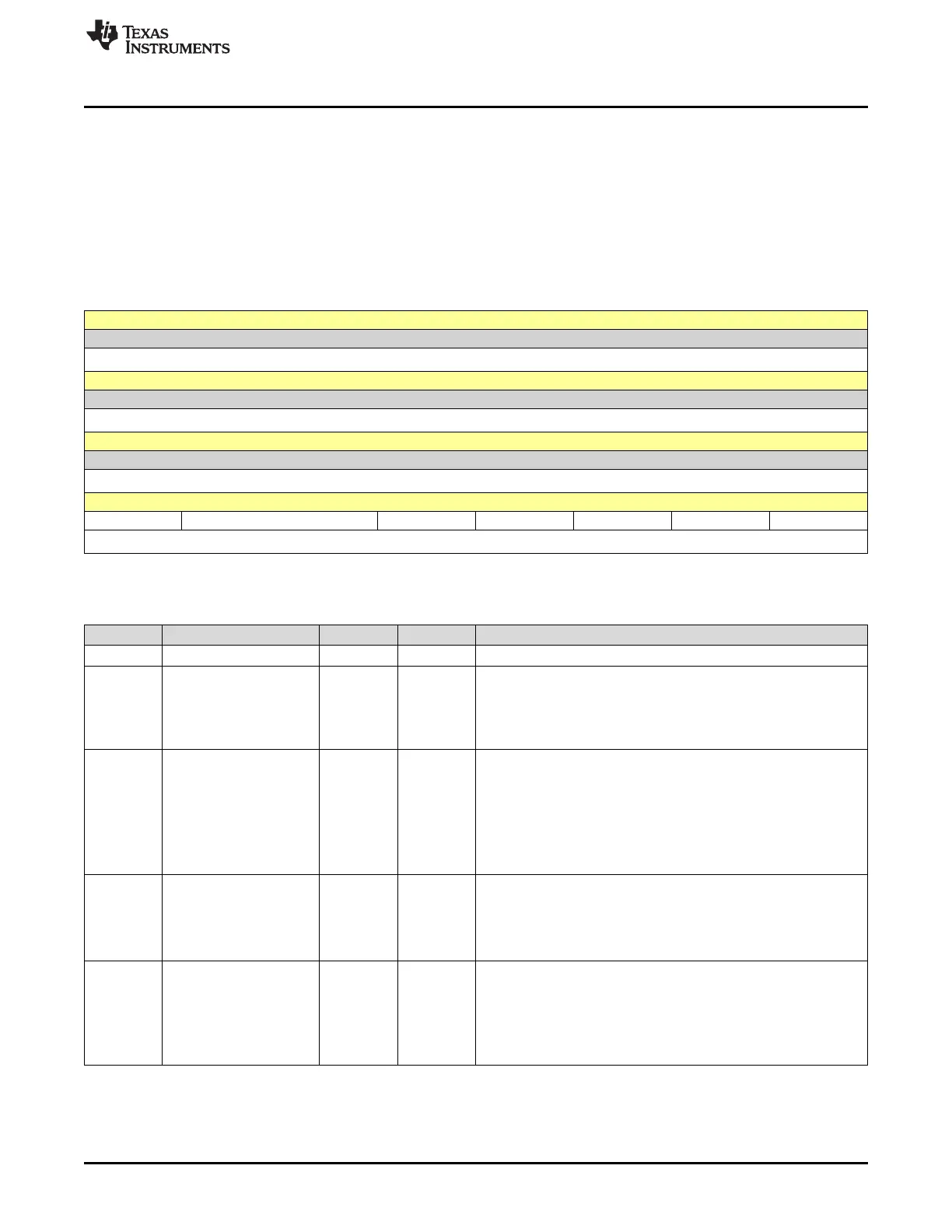

Table 6-8. UARTLCRH Register Field Descriptions

Bit Field Type Reset Description

31-8 RESERVED R 0h

7 SPS R/W 0h

UART Stick Parity Select

When bits 1, 2, and 7 of UARTLCRH are set, the parity bit is

transmitted and checked as a 0. When bits 1 and 7 are set and 2 is

cleared, the parity bit is transmitted and checked as a 1. When this

bit is cleared, stick parity is disabled.

6-5 WLEN R/W 0h

UART Word Length

The bits indicate the number of data bits transmitted or received in a

frame as follows:

0h = 5 bits (default)

1h = 6 bits

2h = 7 bits

3h = 8 bits

4 FEN R/W 0h

UART Enable FIFOs

0h = The FIFOs are disabled (Character mode). The FIFOs become

1-byte-deep holding registers.

1h = The transmit and receive FIFO buffers are enabled (FIFO

mode).

3 STP2 R/W 0h

UART Two Stop Bits Select

When in 7816 smartcard mode (the SMART bit is set in the

UARTCTL register), the number of stop bits is forced to 2.

0h = One stop bit is transmitted at the end of a frame.

1h = Two stop bits are transmitted at the end of a frame. The receive

logic does not check for two stop bits being received.

Loading...

Loading...