SD-HOST Registers

www.ti.com

382

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

SD Host Controller Interface

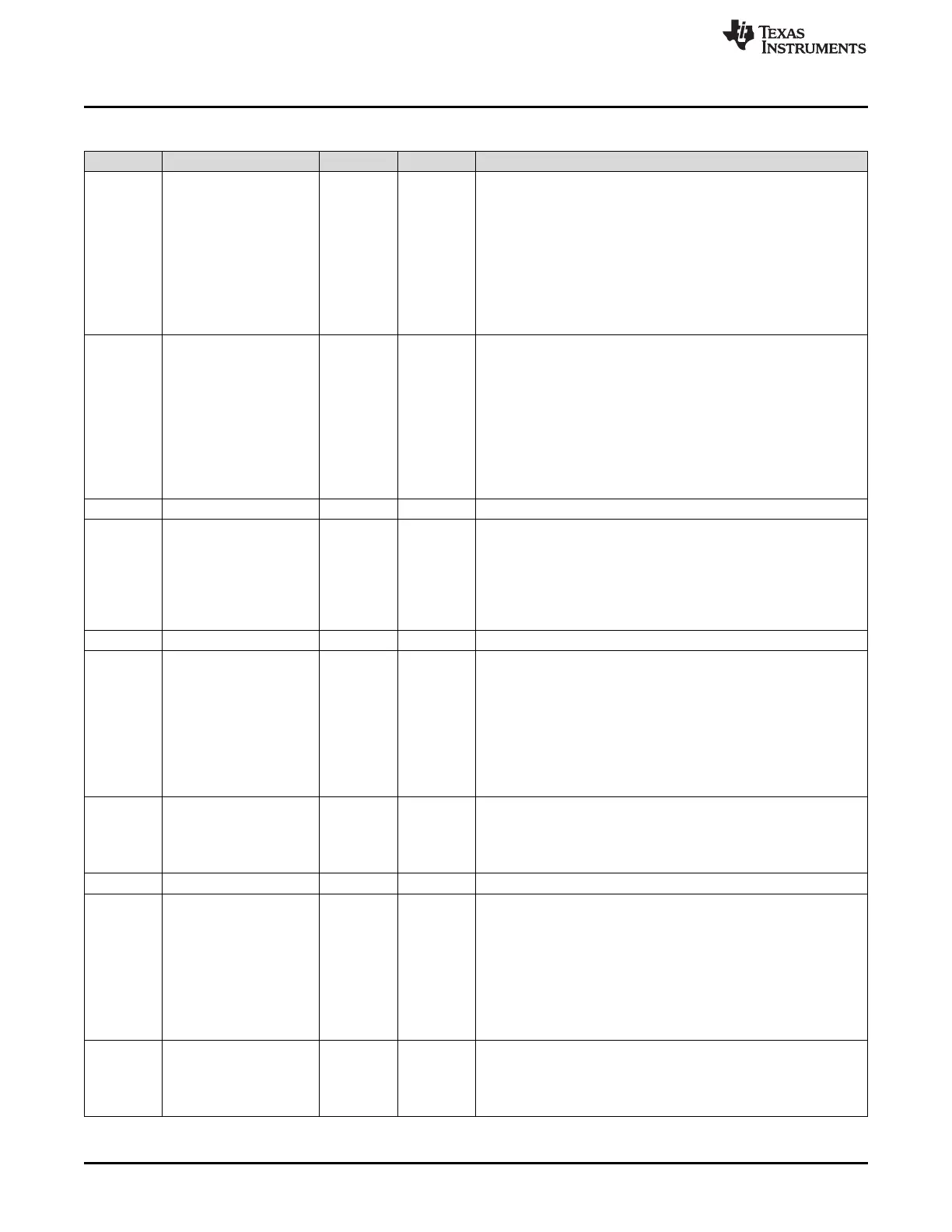

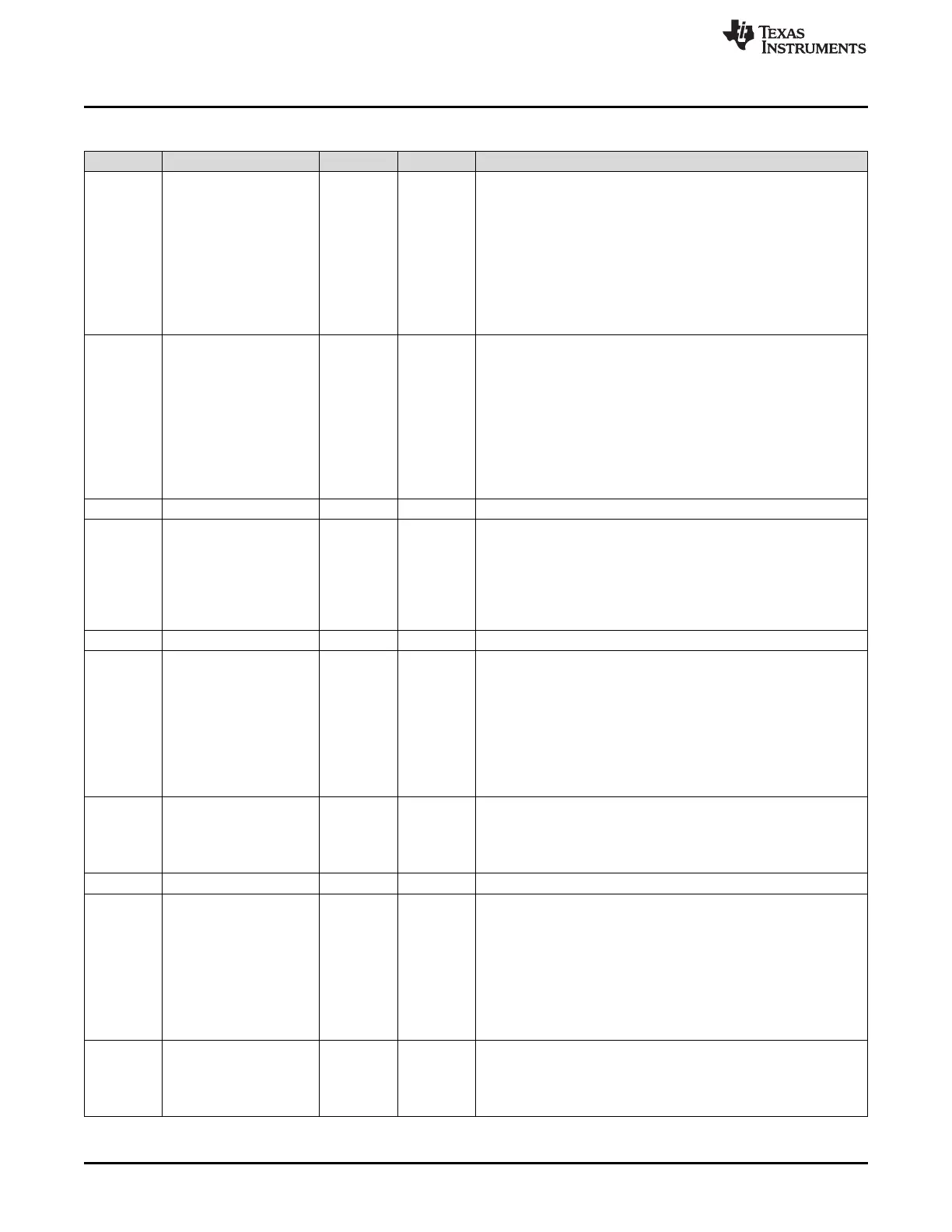

Table 11-9. MMCHS_CMD Register Field Descriptions (continued)

Bit Field Type Reset Description

20 CICE R/W 0h

Command Index check enable

This bit must be set to 1 to enable index check on command

response to compare the index field in the response against the

index of the command. If the index is not the same in the response

as in the command, it is reported as a command index error

(MMCi.MMCHS_STAT[19] CIE bit set to1)

Note: The CICE bit cannot be configured for an Auto CMD12, then

index check is automatically checked when this command is issued.

0h = Index check disable

1h = Index check enable

19 CCCE R/W 0h

Command CRC check enable

This bit must be set to 1 to enable CRC7 check on command

response to protect the response against transmission errors on the

bus. If an error is detected, it is reported as a command CRC error

(MMCi.MMCHS_STAT[17] CCRC bit set to 1).

Note: The CCCE bit cannot be configured for an Auto CMD12, and

then CRC check is automatically checked when this command is

issued.

0h = CRC7 check disable

1h = CRC7 check enable

18 RESERVED R 0h

17-16 RSP_TYPE R/W 0h

Response type

These bits define the response type of the command.

0h = No response

1h = Response Length 136 bits

2h = Response Length 48 bits

3h = Response Length 48 bits with busy after response

15-6 RESERVED R 0h

5 MSBS R/W 0h

Multi/Single block select

This bit must be set to 1 for data transfer in case of multi-block

command. For any others command, this bit is set to 0.

0h = Single block. If this bit is 0, it is not necessary to set the register

MMCi.MMCHS_BLK[31:16] NBLK bits.

1h = Multi-block. When Block Count is disabled

(MMCi.MMCHS_CMD[1] BCE bit is set to 0) in Multiple block

transfers (MMCi.MMCHS_CMD[5] MSBS bit is set to 1), the module

can perform infinite transfer.

4 DDIR R/W 0h

Data transfer direction

This bit defines whether either data transfer is a read or a write.

0h = Data Write (host to card)

1h = Data Read (card to host)

3-2 RESERVED R 0h

1 BCE R/W 0h

Block Count Enable (multiple block transfers only)

This bit is used to enable the block count register

(MMCHS_BLK[31:16] NBLK bits). When Block Count is disabled

(MMCHS_CMD[1] BCE bit is set to 0) in multiple block transfers

(MMCHS_CMD[5] MSBS bits is set to 1), the module can perform

infinite transfer.

0h = Block count disabled for infinite transfer

1h = Block count enabled for multiple block transfer with known

number of blocks

0 DE R/W 0h

DMA enable

This bit is used to enable DMA mode for host data access.

0h = DMA mode disable

1h = DMA mode enable

Loading...

Loading...