www.ti.com

I2S Registers

423

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Inter-Integrated Sound (I2S) Multichannel Audio Serial Port

12.5.6 GBLCTL Register (Offset = 44h) [reset = 0h]

GBLCTL is shown in Figure 12-9 and described in Table 12-11.

Return to Summary Table.

The global control register (GBLCTL) provides initialization of the transmit and receive sections.

The bit fields in GBLCTL are synchronized and latched by the corresponding clocks (ACLKX for bits 12-8

and ACLKR for bits 4-0). Before GBLCTL is programmed, ensure that serial clocks are running. If the

corresponding external serial clocks, ACLKX and ACLKR, are not yet running, select the internal serial

clock source in AHCLKXCTL, AHCLKRCTL, ACLKXCTL, and ACLKRCTL before GBLCTL is

programmed. Also, after programming any bits in GBLCTL do not proceed until you have read back from

GBLCTL and verified that the bits are latched in GBLCTL.

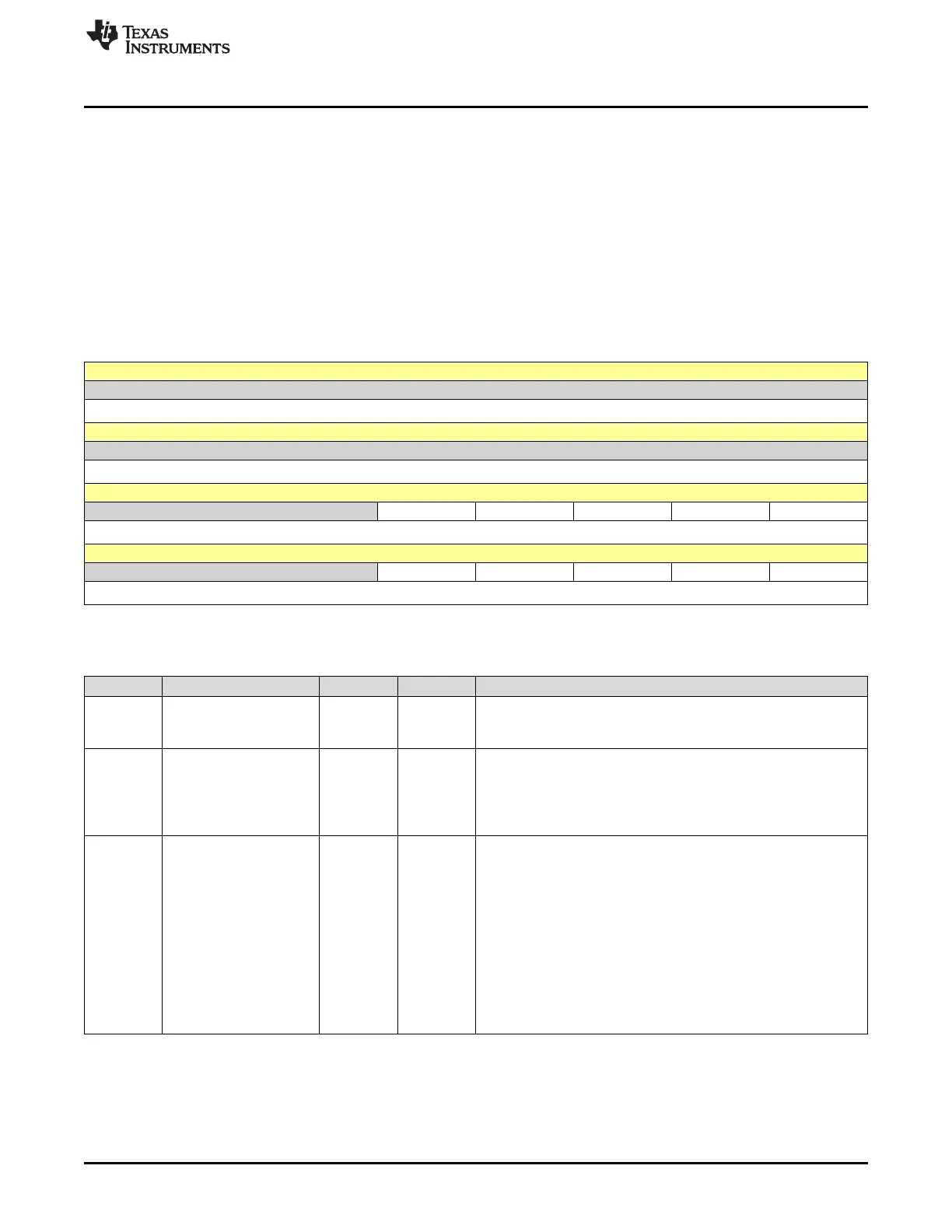

Figure 12-9. GBLCTL Register

31 30 29 28 27 26 25 24

RESERVED

R-0h

23 22 21 20 19 18 17 16

RESERVED

R-0h

15 14 13 12 11 10 9 8

RESERVED XFRST XSMRST XSRCLR XHCLKRST XCLKRST

R-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h

7 6 5 4 3 2 1 0

RESERVED RFRST RSMRST RSRCLR RHCLKRST RCLKRST

R-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

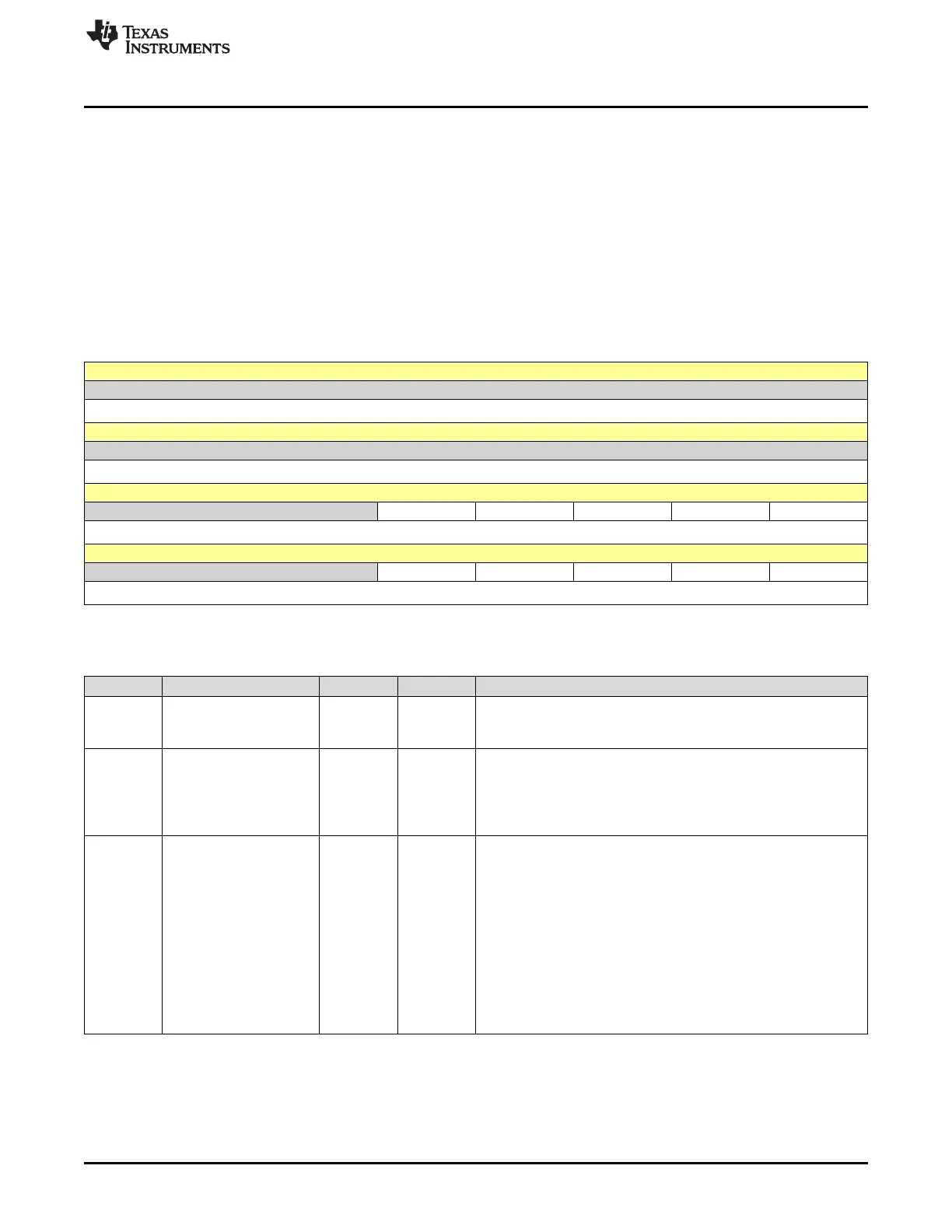

Table 12-11. GBLCTL Register Field Descriptions

Bit Field Type Reset Description

31-13 RESERVED R 0h

Reserved. The reserved bit location always returns the default value.

A value written to this field has no effect. If writing to this field,

always write the default value for future device compatibility.

12 XFRST R/W 0h

Transmit frame sync generator reset enable bit.

0h = Transmit frame sync generator is reset.

1h = Transmit frame sync generator is active. When released from

reset, the transmit frame sync generator begins counting serial

clocks and generating frame sync as programmed.

11 XSMRST R/W 0h

Transmit state machine reset enable bit.

0h = Transmit state machine is held in reset. AXR[n] pin state: If

PFUNC[n] = 0 and PDIR[n] = 1; then the serializer drives the AXR[n]

pin to the state specified for inactive time slot (as determined by

DISMOD bits in SRCTL).

1h = Transmit state machine is released from reset. When released

from reset, the transmit state machine immediately transfers data

from XRBUF[n] to XRSR[n]. The transmit state machine sets the

underrun flag (XUNDRN) in XSTAT, if XRBUF[n] have not been

preloaded with data before reset is released. The transmit state

machine also immediately begins detecting frame sync and is ready

to transmit. Transmit TDM time slot begins at slot 0 after reset is

released.

Loading...

Loading...