www.ti.com

Timer Registers

327

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

General-Purpose Timers

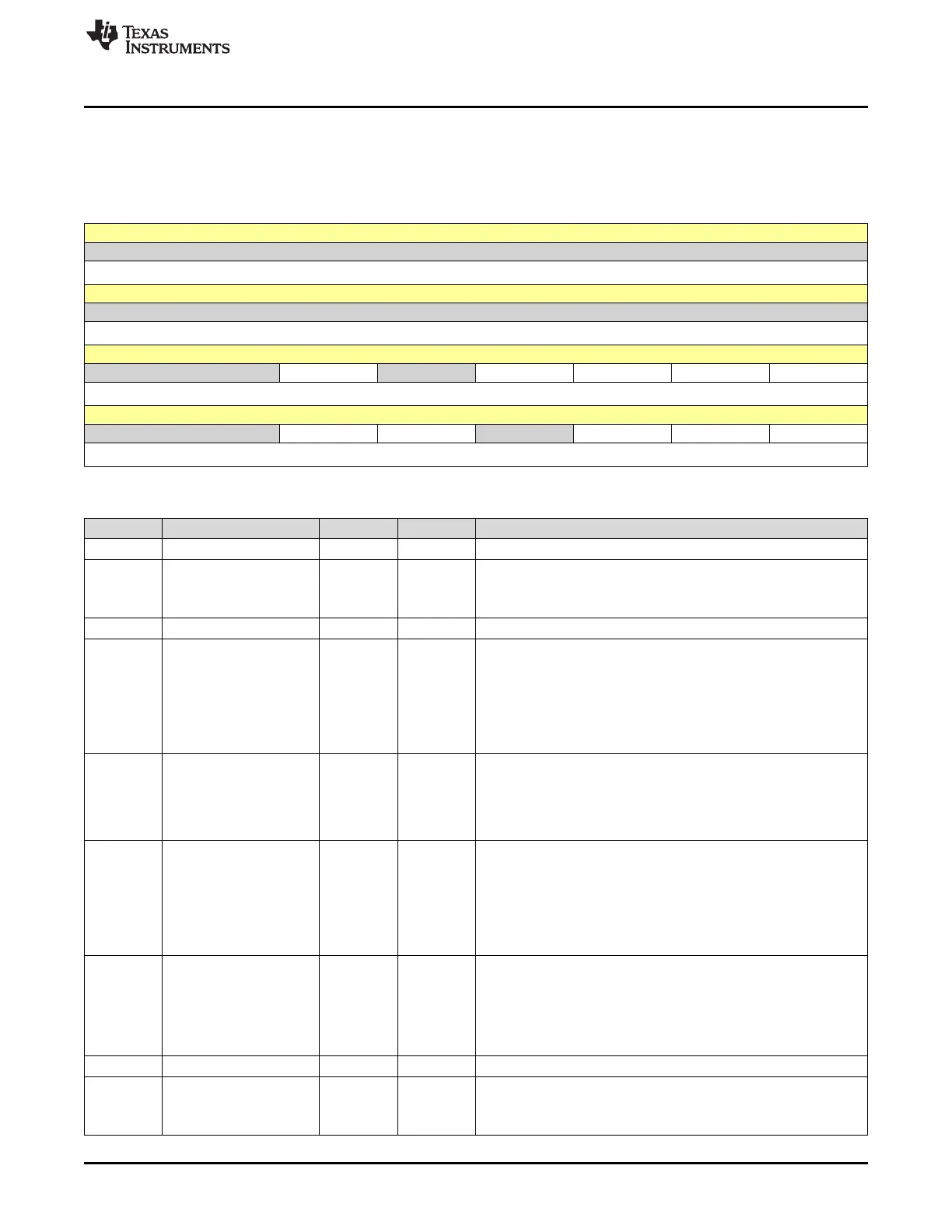

9.5.6 GPTMRIS Register (offset = 1Ch) [reset = 0h]

Register mask: 0h

GPTMRIS is shown in Figure 9-10 and described in Table 9-14.

Figure 9-10. GPTMRIS Register

31 30 29 28 27 26 25 24

RESERVED

R-X

23 22 21 20 19 18 17 16

RESERVED

R-X

15 14 13 12 11 10 9 8

RESERVED DMABRIS RESERVED TBMRIS CBERIS CBMRIS TBTORIS

R-X R-X R-X R-X R-X R-X R-X

7 6 5 4 3 2 1 0

RESERVED DMAARIS TAMRIS RESERVED CAERIS CAMRIS TATORIS

R-X R-X R-X R-X R-X R-X R-X

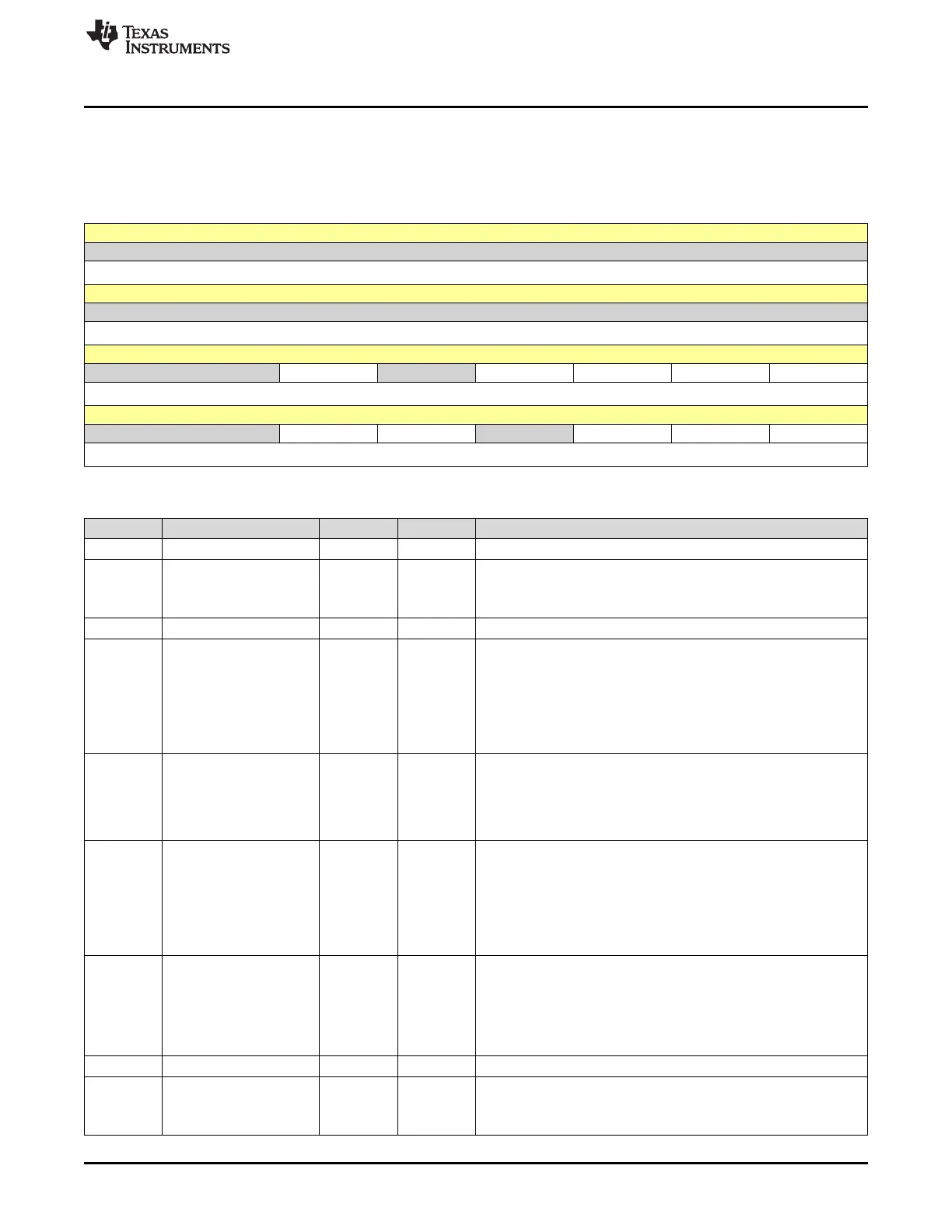

Table 9-14. GPTMRIS Register Field Descriptions

Bit Field Type Reset Description

31-14 RESERVED R X

13 DMABRIS R X

GPTM Timer B DMA Done Raw Interrupt Status

0h = The Timer B DMA transfer has not completed.

1h = The Timer B DMA transfer has completed.

12 RESERVED R X

11 TBMRIS R X

GPTM Timer B Match Raw Interrupt. This bit is cleared by writing 1

to the TBMCINT bit in the GPTMICR register.

0h = The match value has not been reached.

1h = The TBMIE bit is set in the GPTMTBMR register, and the

match values in the GPTMTBMATCHR and (optionally)

GPTMTBPMR registers have been reached when configured in one-

shot or periodic mode.

10 CBERIS R X

GPTM Timer B Capture Mode Event Raw Interrupt. This bit is

cleared by writing 1 to the CBECINT bit in the GPTMICR register.

0h = The capture mode event for Timer B has not occurred.

1h = A capture mode event has occurred for Timer B. This interrupt

asserts when the subtimer is configured in input edge-time mode.

9 CBMRIS R X

GPTM Timer B Capture Mode Match Raw Interrupt. This bit is

cleared by writing 1 to the CBMCINT bit in the GPTMICR register.

0h = The capture mode match for Timer B has not occurred.

1h = The capture mode match has occurred for Timer B. This

interrupt asserts when the values in the GPTMTBR and GPTMTBPR

match the values in the GPTMTBMATCHR and GPTMTBPMR when

configured in input edge-time mode.

8 TBTORIS R X

GPTM Timer B Time-Out Raw Interrupt. This bit is cleared by writing

1 to the TBTOCINT bit in the GPTMICR register.

0h = Timer B has not timed out.

1h = Timer B has timed out. This interrupt is asserted when a one-

shot or periodic mode timer reaches the count limit (0 or the value

loaded into GPTMTBILR, depending on the count direction).

7-6 RESERVED R X

5 DMAARIS R X

GPTM Timer A DMA Done Raw Interrupt Status

0h = The Timer A DMA transfer has not completed.

1h = The Timer A DMA transfer has completed.

Loading...

Loading...