www.ti.com

SHA-MD5 Registers

727

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

SHA/MD5 Accelerator

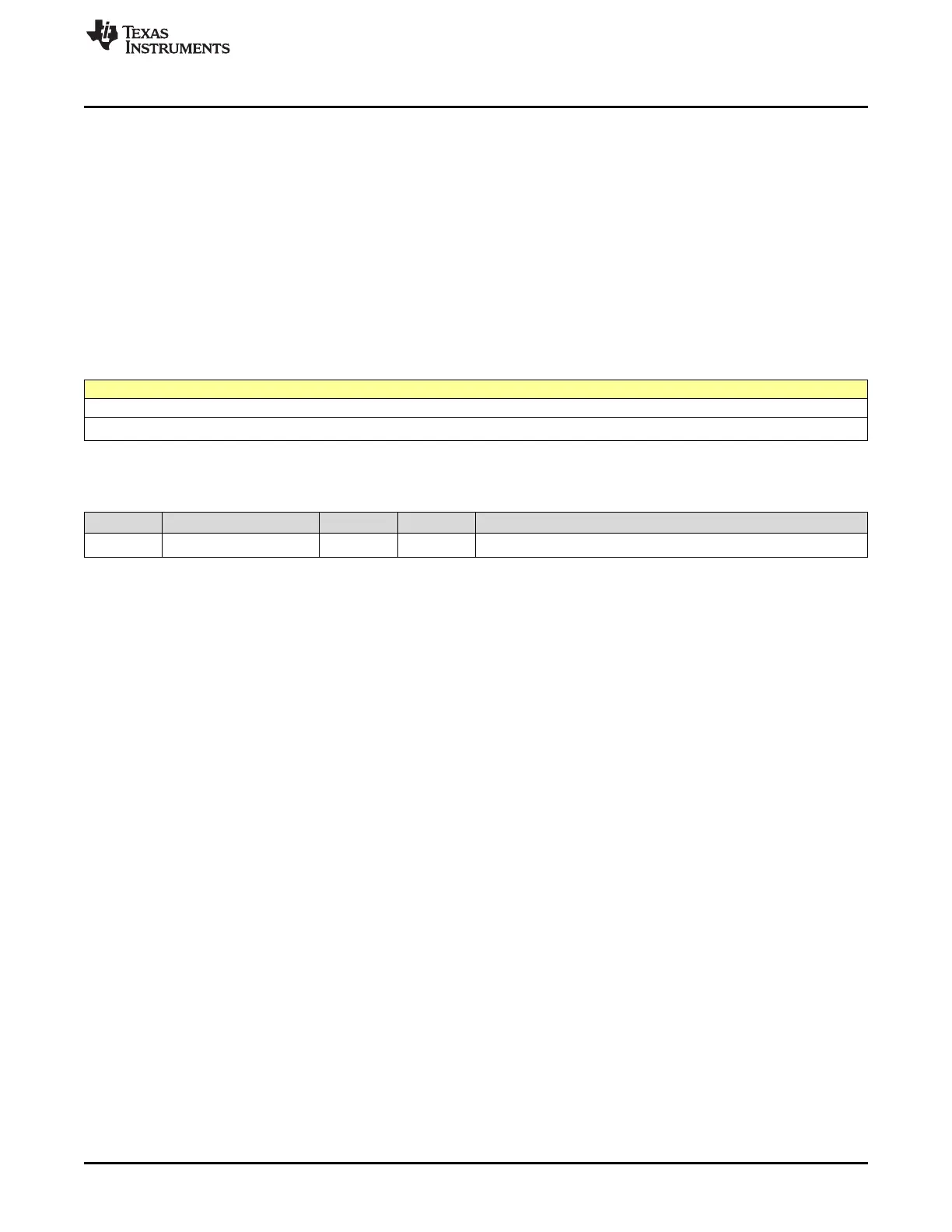

19.2.19 SHAMD5_LENGTH Register (Offset = 48h) [reset = 0h]

SHAMD5_LENGTH is shown in Figure 19-23 and described in Table 19-30.

Return to Summary Table.

WRITE: Block length / remaining byte count (bytes)

READ: Remaining byte count.

The value programmed must be a 64-byte multiple if close hash is set to 0. This register is also the trigger

to start processing: once this register is written, the core commences requesting input data through DMA

or IRQ (if programmed length > 0) and start processing.

The remaining byte count for the active operation can be read from this register when the interrupt status

register indicates that the operation is suspended due to a context switch request.

Figure 19-23. SHAMD5_LENGTH Register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

DATA

R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

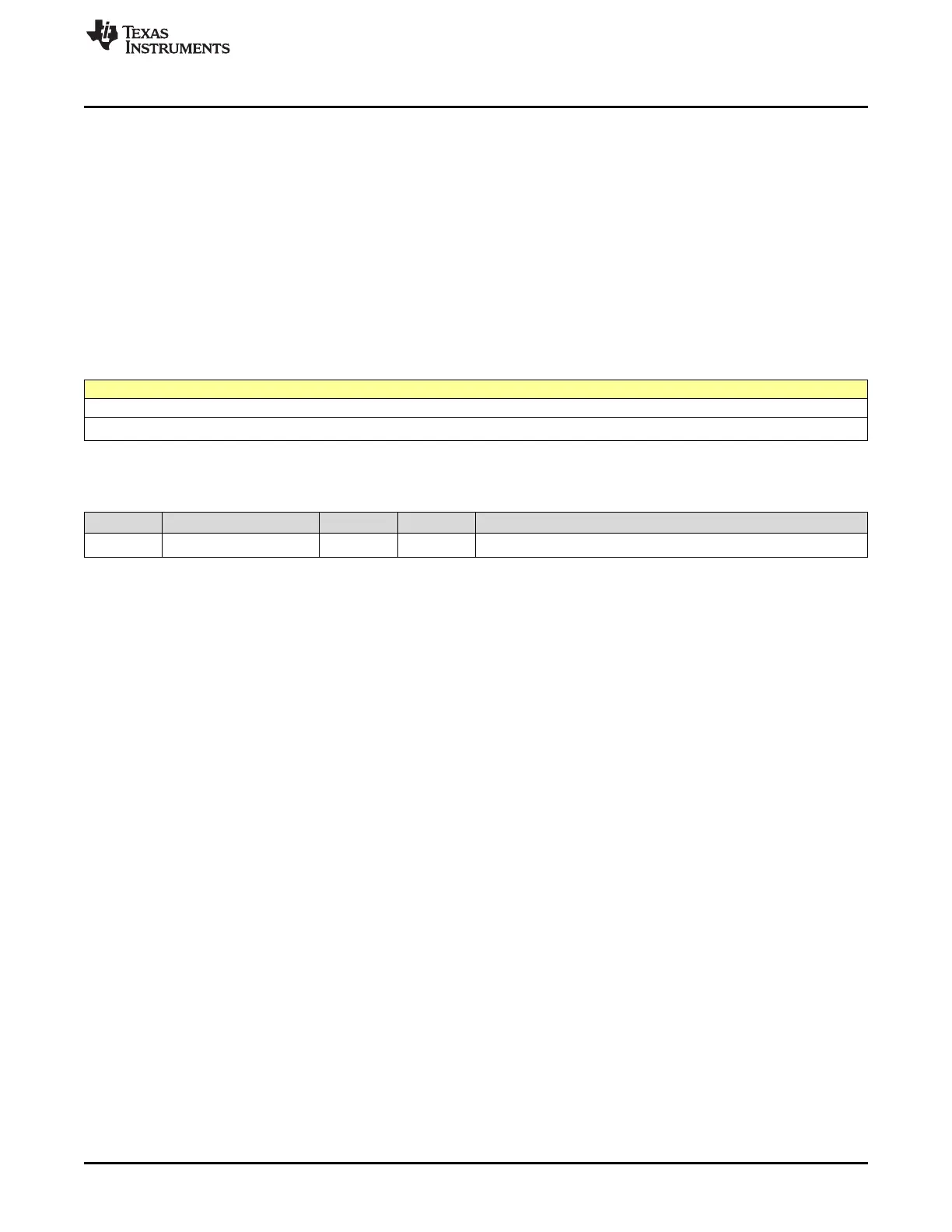

Table 19-30. SHAMD5_LENGTH Register Field Descriptions

Bit Field Type Reset Description

31-0 DATA R/W 0h

Data

Hash Input Data Registers: The following are input data registers for the Hash/HMAC engine:

• SHAMD5_DATA0_IN

• SHAMD5_DATA1_IN

• SHAMD5_DATA2_IN

• SHAMD5_DATA3_IN

• SHAMD5_DATA4_IN

• SHAMD5_DATA5_IN

• SHAMD5_DATA6_IN

• SHAMD5_DATA7_IN

• SHAMD5_DATA8_IN

• SHAMD5_DATA9_IN

• SHAMD5_DATA10_IN

• SHAMD5_DATA11_IN

• SHAMD5_DATA12_IN

• SHAMD5_DATA13_IN

• SHAMD5_DATA14_IN

• SHAMD5_DATA15_IN

Writing 4-byte words to a word-aligned offset within this address range pushes the data into the 32-word

deep (128 bytes = 1024 bits for one SHA-384/512 hash block) data-input FIFO. Although the actual

address used within the range is not important, the order of the data words is. Also, do not exceed the

FIFO size: check the status signals after writing a full block of 16 words or 32 words for SHA-384 and

SHA-512.

Loading...

Loading...