www.ti.com

Module Initialization

285

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

SPI (Serial Peripheral Interface)

The executed transfer has size of N. If the requests are configured in DMA, write_count and read_count

are assigned with N.

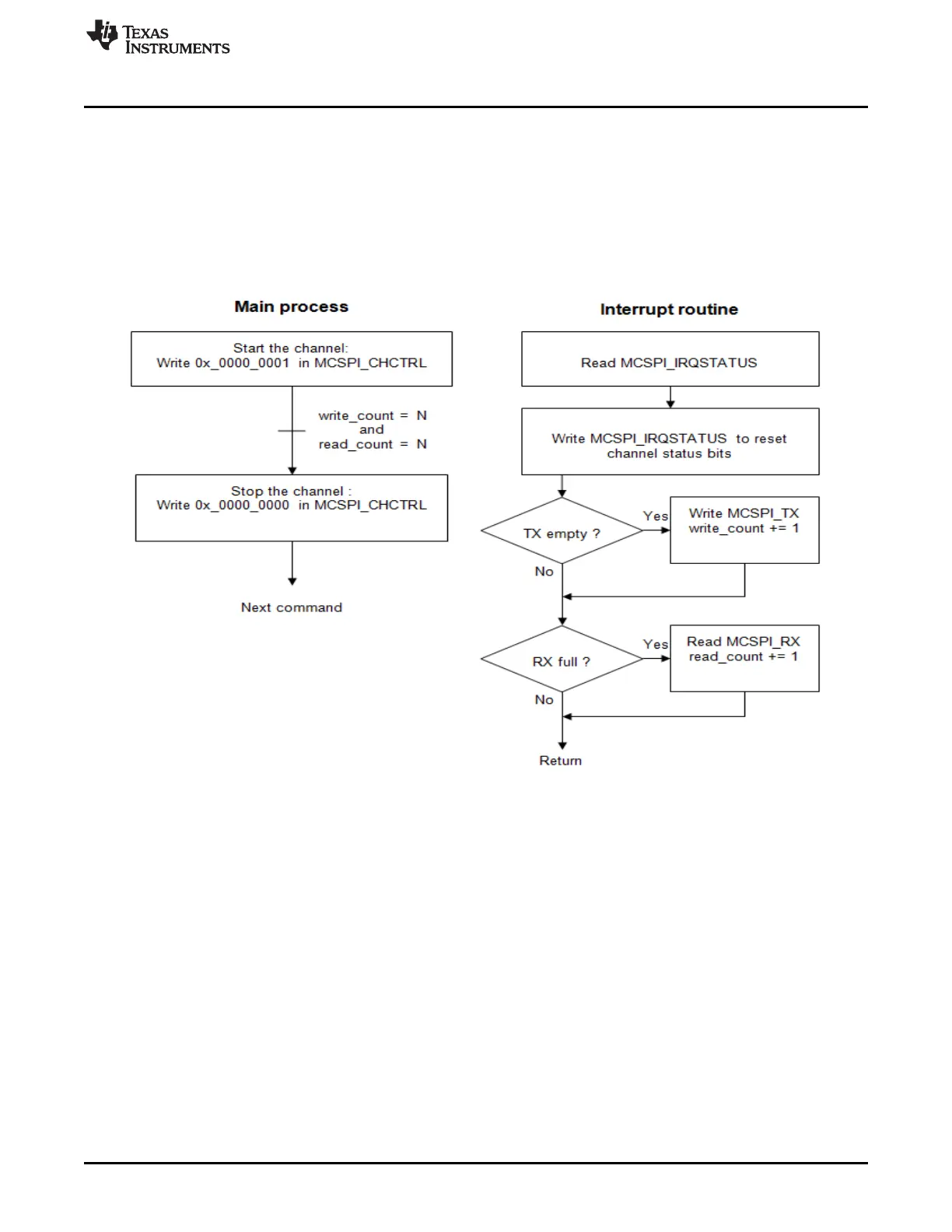

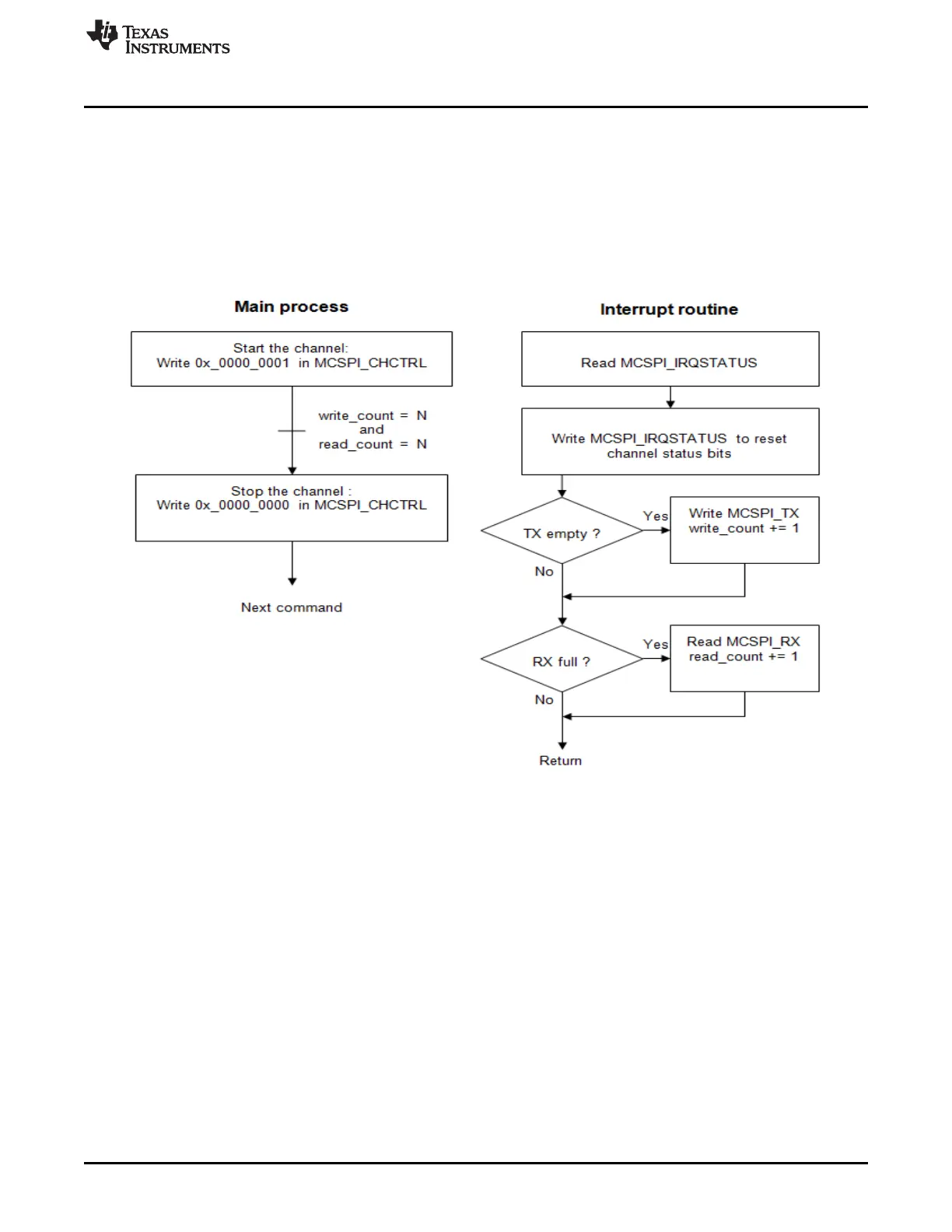

Figure 8-16 highlights the interrupt routine executed for N times until write_count and read_count reached

value N, after which the transfer is over and the main process disables the channel.

Figure 8-16. Flow Chart – Transmit and Receive (Master and Slave)

8.5.3 FIFO Mode

These flows describe the transfer with FIFO.

The SPI module allows the transfer of one or several words, according to different modes:

• Master normal, master turbo, slave

• Transmit – receive

• Write and read requests: IRQ, DMA

For each flow, the host process contains the main process and the interrupt routine. This routine is called

on the IRQ signals, or by an internal call if the module is used in polling mode.

8.5.3.1 Common Transfer Sequence

In transmit and receive mode, the FIFO can be enabled for write or read request only. The SPI module

starts the transfer only when the first write request is released, by writing the SPI_TX register. See

Figure 8-17.

Loading...

Loading...