www.ti.com

AES Registers

655

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Advance Encryption Standard Accelerator (AES)

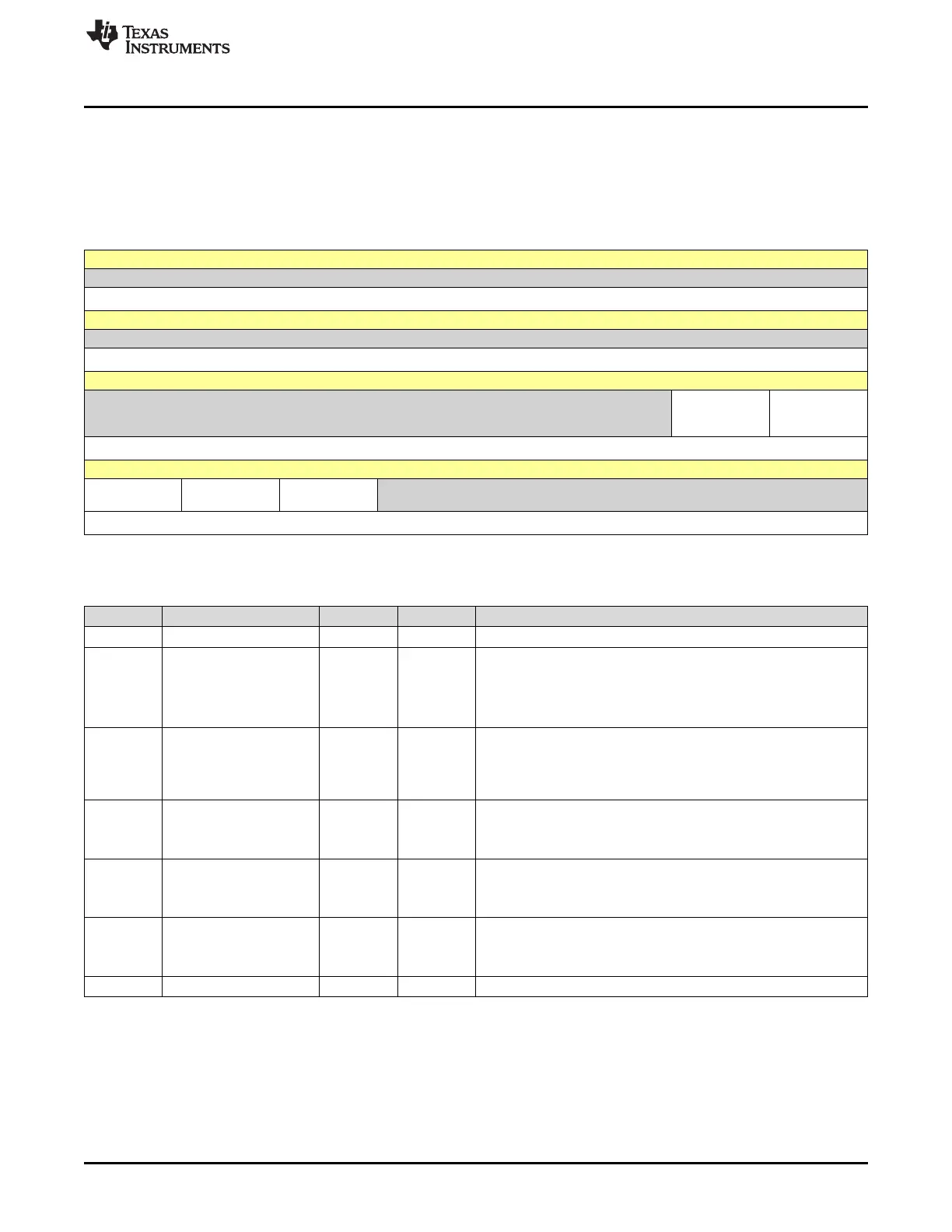

17.4.34 AES_SYSCONFIG Register (Offset = 84h) [reset = X]

AES_SYSCONFIG is shown in Figure 17-47 and described in Table 17-37.

Return to Summary Table.

This register configures the DMA signals.

Figure 17-47. AES_SYSCONFIG Register

31 30 29 28 27 26 25 24

RESERVED

R-X

23 22 21 20 19 18 17 16

RESERVED

R-X

15 14 13 12 11 10 9 8

RESERVED MAP_CONTEX

T_OUT_ON_D

ATA_OUT

DMA_REQ_CO

NTEXT_OUT_

EN

R-X R/W-0h R/W-0h

7 6 5 4 3 2 1 0

DMA_REQ_CO

NTEXT_IN_EN

DMA_REQ_DA

TA_OUT_EN

DMA_REQ_DA

TA_IN_EN

RESERVED

R/W-0h R/W-0h R/W-0h R-X

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

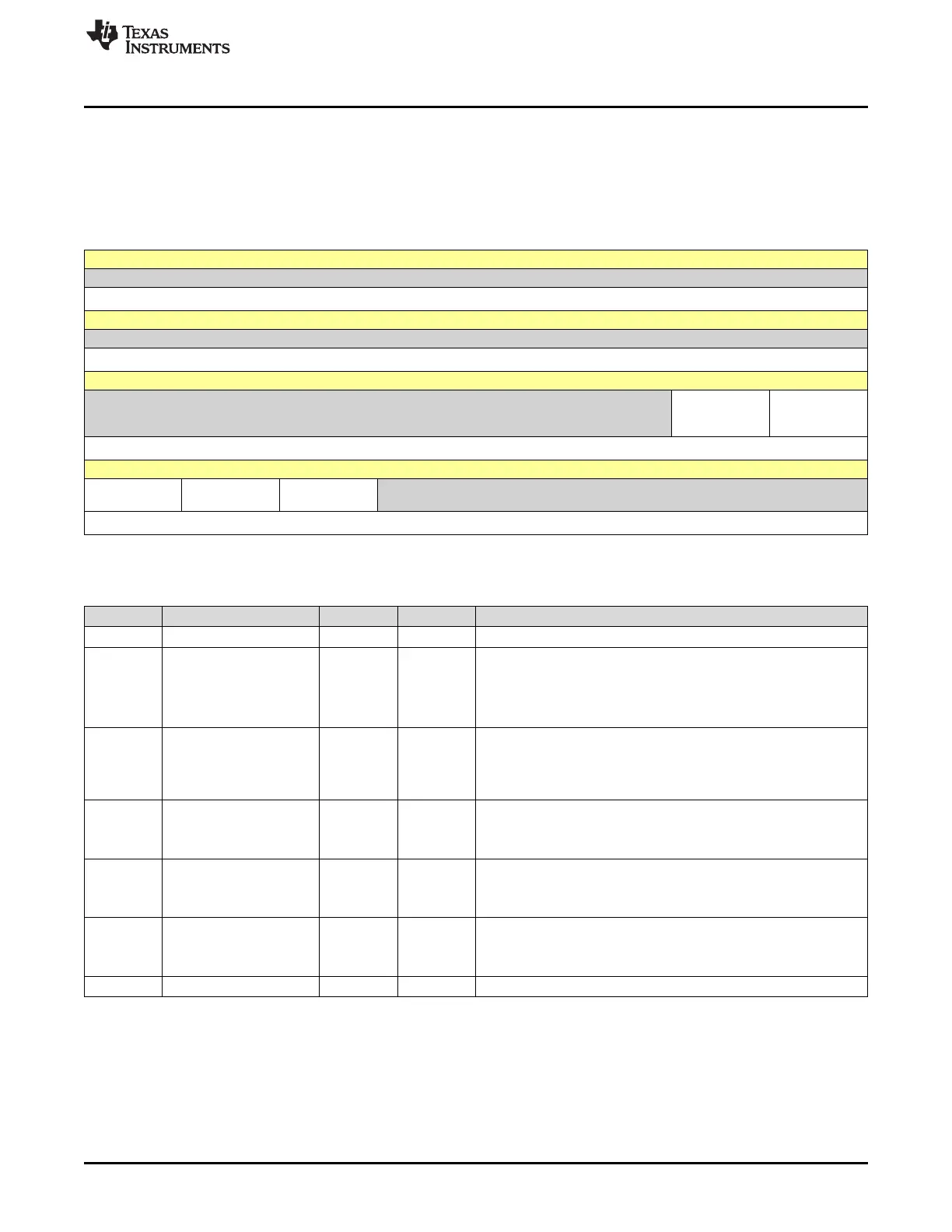

Table 17-37. AES_SYSCONFIG Register Field Descriptions

Bit Field Type Reset Description

31-10 RESERVED R X

9 MAP_CONTEXT_OUT_O

N_DATA_OUT

R/W 0h

If set to 1, the two context out requests (dma_req_context_out_en,

Bit [8] above, and context_out interrupt enable, Bit [3] of

AES_IRQENABLE register) are mapped on the corresponding data

output request bit. In this case, the original ‘context out’ bit values

are ignored.

8 DMA_REQ_CONTEXT_O

UT_EN

R/W 0h

If set to 1, the DMA context output request is enabled (for context

data out, for example, TAG for authentication modes).

0h = DMA disabled

1h = DMA enabled

7 DMA_REQ_CONTEXT_IN

_EN

R/W 0h

If set to 1, the DMA context request is enabled.

0h = DMA disabled

1h = DMA enabled

6 DMA_REQ_DATA_OUT_

EN

R/W 0h

If set to 1, the DMA output request is enabled.

0h = DMA disabled

1h = DMA enabled

5 DMA_REQ_DATA_IN_EN R/W 0h

If set to 1, the DMA input request is enabled.

0h = DMA disabled

1h = DMA enabled

4-0 RESERVED R X

Loading...

Loading...