www.ti.com

SD-HOST Registers

391

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

SD Host Controller Interface

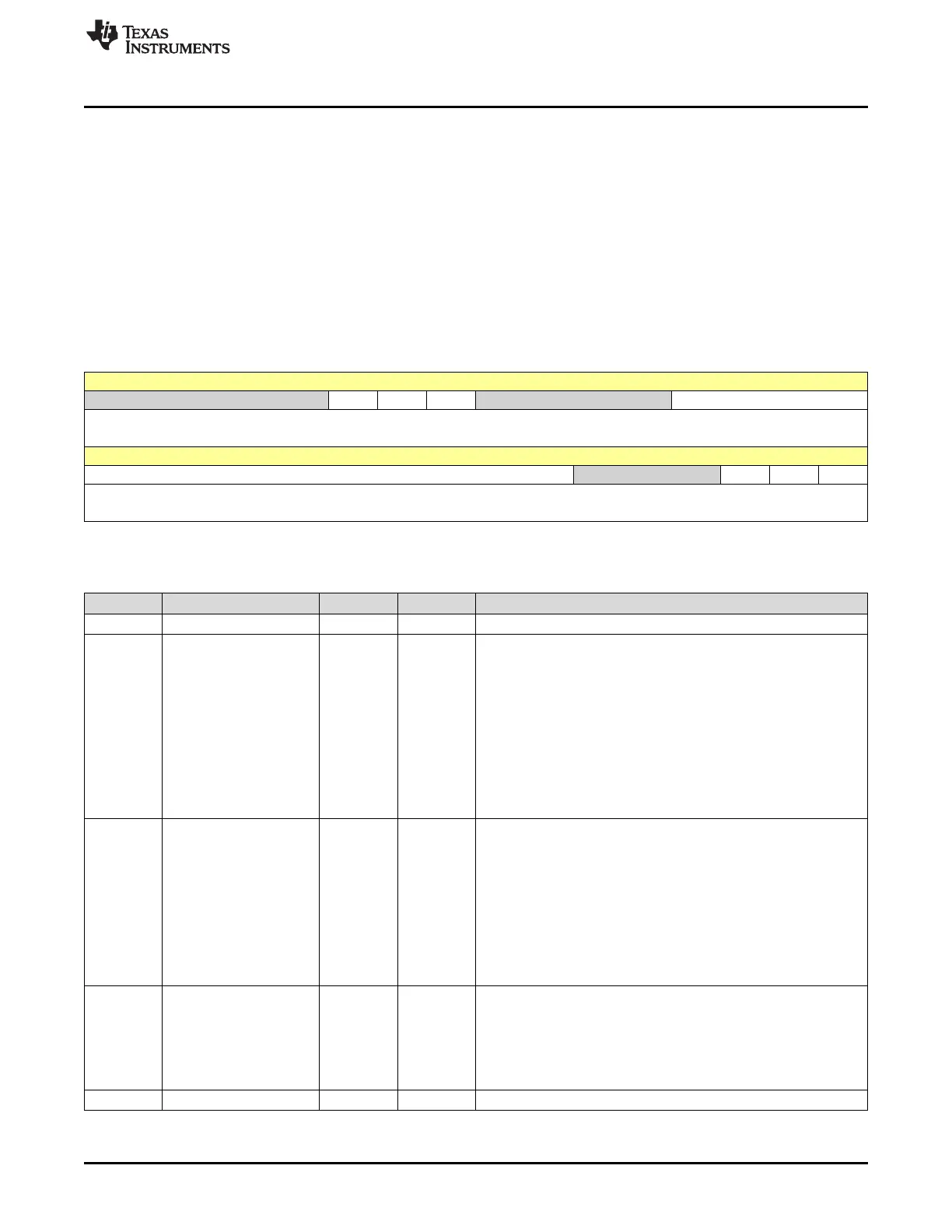

11.7.13 MMCHS_SYSCTL Register (Offset = 22Ch) [reset = 0h]

SD System Control register

MMCHS_SYSCTL is shown in Figure 11-14 and described in Table 11-17.

Return to Summary Table.

This register defines the system controls to set software resets, clock frequency management, and data

time-out.

MMCHS_SYSCTL[31:24] = Software resets

MMCHS_SYSCTL[23:16] = Timeout control

MMCHS_SYSCTL[15:0] = Clock control

Figure 11-14. MMCHS_SYSCTL Register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

RESERVED SRD SRC SRA RESERVED DTO

R-0h R/W-

0h

R/W-

0h

R/W-

0h

R-0h R/W-0h

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

CLKD RESERVED CEN ICS ICE

R/W-0h R-0h R/W-

0h

R-0h R/W-

0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

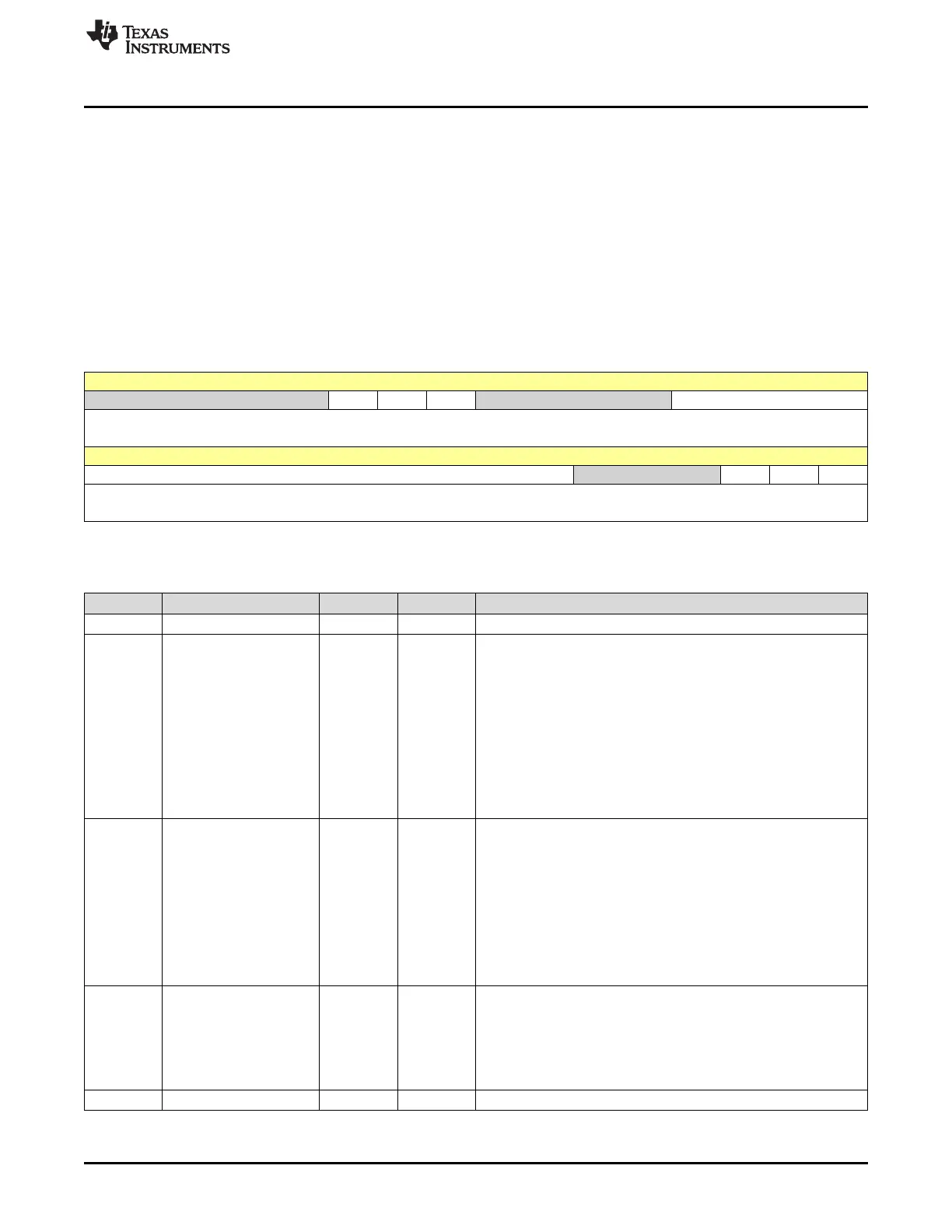

Table 11-17. MMCHS_SYSCTL Register Field Descriptions

Bit Field Type Reset Description

31-27 RESERVED R 0h

26 SRD R/W 0h

Software reset for mmci_dat line

This bit is set to 1 for reset and released to 0 when completed

.mmci_dat finite state machine in both clock domain are also reset.

These registers are cleared by the MMCHS_SYSCTL[26] SRD bit:

MMCi.MMCHS_DATA MMCi.MMCHS_PSTATE: BRE, BWE, RTA,

WTA, DLA and DATI

MMCi.MMCHS_HCTL: SBGR and CR

MMCi.MMCHS_STAT: BRR, BWR, BGE and TC Interconnect and

MMC buffer data management is reinitialized.

0h = Reset completed

1h = Software reset for mmci_dat line

25 SRC R/W 0h

Software reset for mmci_cmd line

This bit is set to 1 for reset and released to 0 when completed.

mmci_cmd finite state machine in both clock domain are also reset.

These are the registers cleared by the MMCi.MMCHS_SYSCTL[25]

SRC bit:

MMCi.MMCHS_PSTATE: CMDI

MMCi.MMCHS_STAT: CC Interconnect and MMC command status

management is reinitialized.

0h = Reset completed

1h = Software reset for mmci_dat line

24 SRA R/W 0h

Software reset for all

This bit is set to 1 for reset , and released to 0 when RW 0

completed. This reset affects the entire host controller except for the

card detection circuit and capabilities registers.

0h = Reset completed

1h = Software reset for all the designs

23-20 RESERVED R 0h

Loading...

Loading...