SD-HOST Registers

www.ti.com

392

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

SD Host Controller Interface

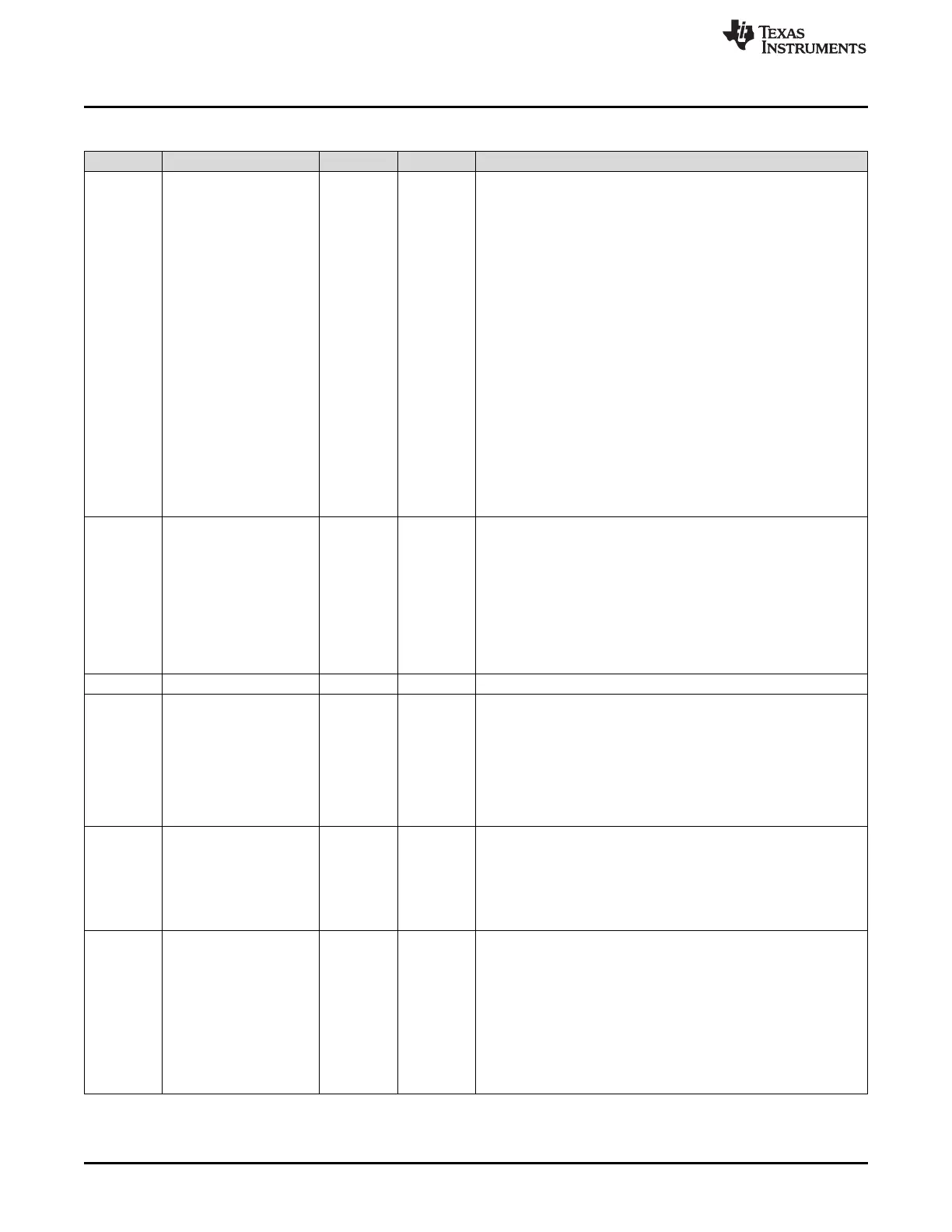

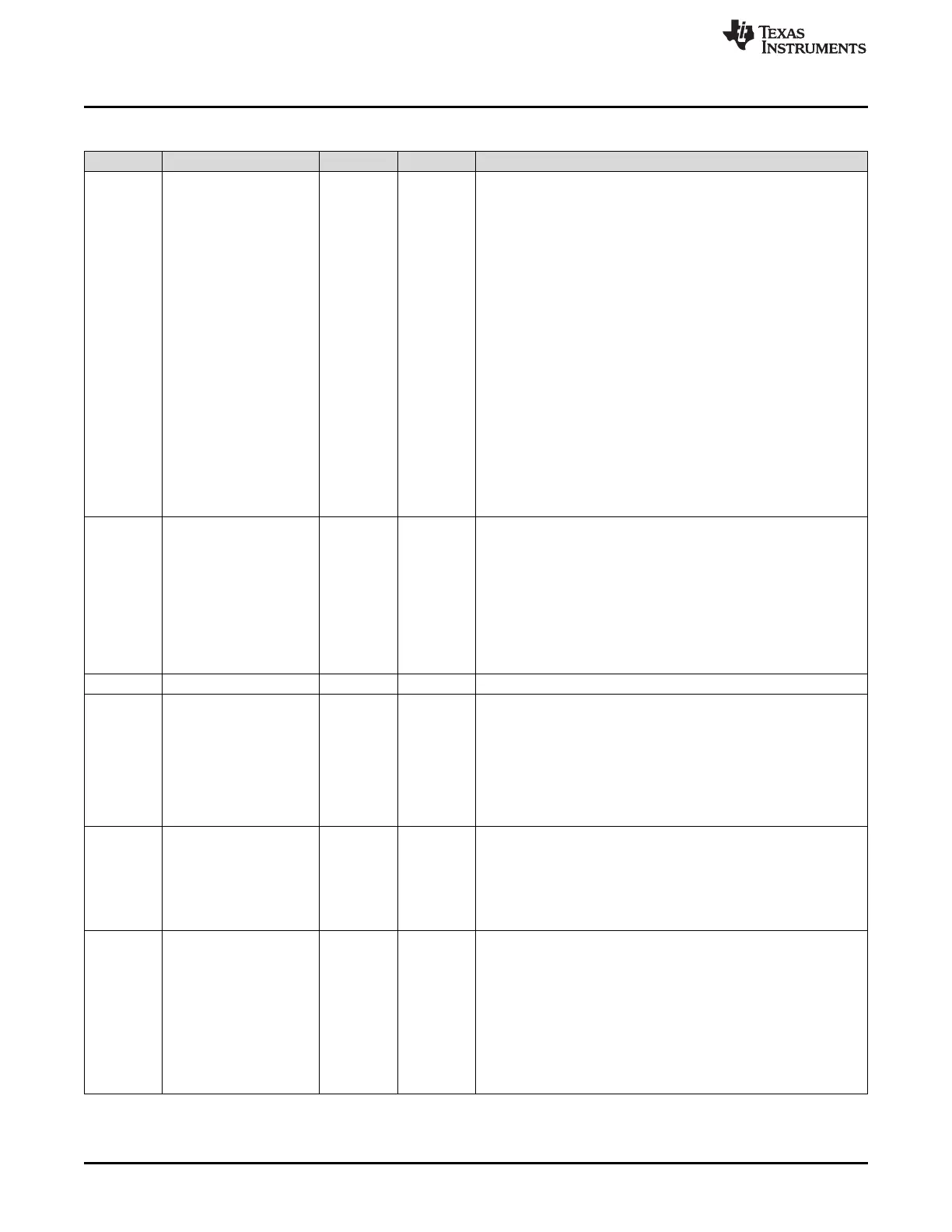

Table 11-17. MMCHS_SYSCTL Register Field Descriptions (continued)

Bit Field Type Reset Description

19-16 DTO R/W 0h

Data time-out counter value and busy time-out

The host driver must set this bit field based on:

• The maximum read access time (NAC) (refer to the

SD Specification Part1 Physical Layer)

• The data read access time values (TAAC and

NSAC) in the card-specific data register (CSD) of

the card

• The time-out clock base frequency

(MMCi.MMCHS_CAPA[5:0] TCF bits)

If the card does not respond within the specified number of cycles, a

data time-out error occurs (MMCi.MMCHS_STAT[20] DTO bit). The

MMCi.MMCHS_SYSCTL[19,16] DTO bitfield is also used to check

busy duration, to generate busy time-out for commands with busy

response or for busy programming during a write command. Timeout

on CRC status is generated if no CRC token is present after a block

write.

0h = TCF × 2

13

1h = TCF × 2

14

Eh = TCF × 2

27

Fh = Reserved

15-6 CLKD R/W 0h

Clock frequency select

These bits define the ratio between a reference RW 0x000 clock

frequency (system-dependant) and the output clock frequency on the

mmci_clk pin of either the memory card (MMC, SD or SDIO).

0h = Clock Ref bypass

1h = Clock Ref bypass

2h = Clock Ref / 2

3h = Clock Ref / 3

3FFh = Clock Ref / 1023

5-3 RESERVED R 0h

2 CEN R/W 0h

Clock enable

This bit controls whether the clock is provided to the card or not.

0h = The clock is not provided to the card. Clock frequency can be

changed.

1h = The clock is provided to the card and can be automatically

gated when MMCi.MMCHS_SYSCONFIG[0] AUTOIDLE bit is set to

1 (default value). The host driver waits to set this bit to 1 until the

internal clock is stable (MMCi.MMCHS_SYSCTL[1] ICS bit).

1 ICS R 0h

Internal clock stable (status)

This bit indicates either the internal clock is stable or not.

0h = The internal clock is not stable

1h = The internal clock is stable after enabling the clock

(MMCi.MMCHS_SYSCTL[0] ICE bit) or after changing the clock ratio

(MMCi.MMCHS_SYSCTL[15:6] CLKD bits).

0 ICE R/W 0h

Internal clock enable

This register controls the internal clock activity. In a very low-power

state, the internal clock is stopped.

Note: The activity of the debounce clock (used for wakeup events)

and the interface clock (used for reads and writes to the module

register map) are not affected by this register.

0h = The internal clock is stopped (very low power state).

1h = The internal clock oscillates and can be automatically gated

when MMCi.MMCHS_SYSCONFIG[0] AUTOIDLE bit is set to 1

(default value).

Loading...

Loading...