Functional Pin Mux Configurations

www.ti.com

592

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

I/O Pads and Pin Multiplexing

(1)

LPDS mode: The state of unused GPIOs in LPDS is input with 500-kΩ pulldown. For all used GPIOs , the user can enable internal pulls, which would hold them in a valid state.

(2)

Hibernate mode: The CC32xx device leaves the digital pins in a Hi-Z state without any internal pulls when the device enters hibernate state. This can cause glitches on output lines, unless

held at valid levels by external resistors.

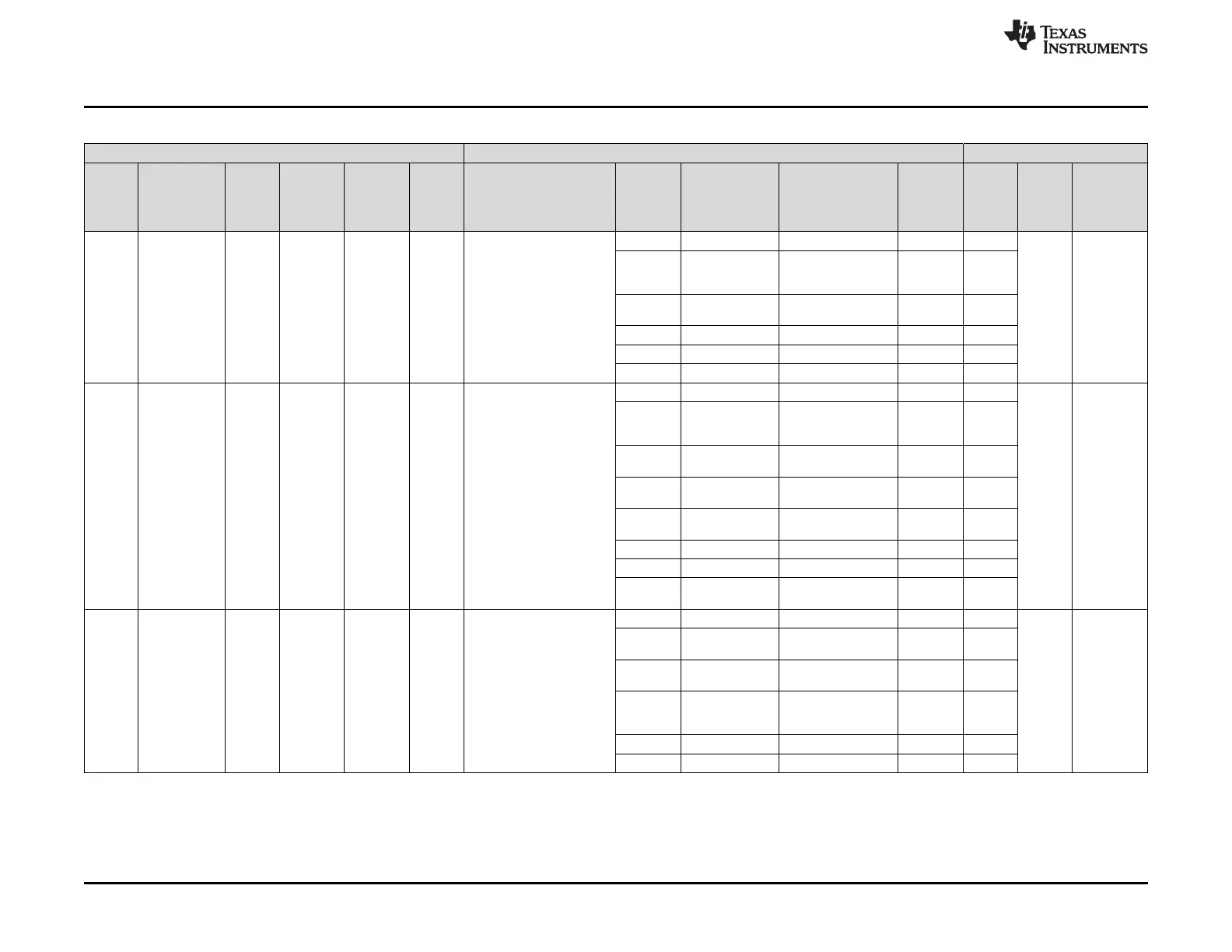

Table 16-7. Pin Multiplexing

General Pin Attributes Function Pad States

Pkg Pin Pin Alias Use Select as

Wakeup

Source

Config

Addl

Analog

Mux

Muxed

with

JTAG

Dig. Pin Mux Config Reg Dig. Pin

Mux

Config

Mode

Value

Signal Name Signal Description Signal

Direction

LPDS

(1)

Hib

(2)

nRESET = 0

1 GPIO10 I/O No No No

GPIO_PAD_CONFIG_10

(0x4402 E0C8)

0 GPIO10 General-Purpose I/O I/O Hi-Z

Hi-Z Hi-Z

1 I2C_SCL I2C Clock O

(Open

Drain)

Hi-Z

3 GT_PWM06 Pulse-Width

Modulated O/P

O Hi-Z

7 UART1_TX UART TX Data O 1

6 SDCARD_CLK SD Card Clock O 0

12 GT_CCP01 Timer Capture Port I Hi-Z

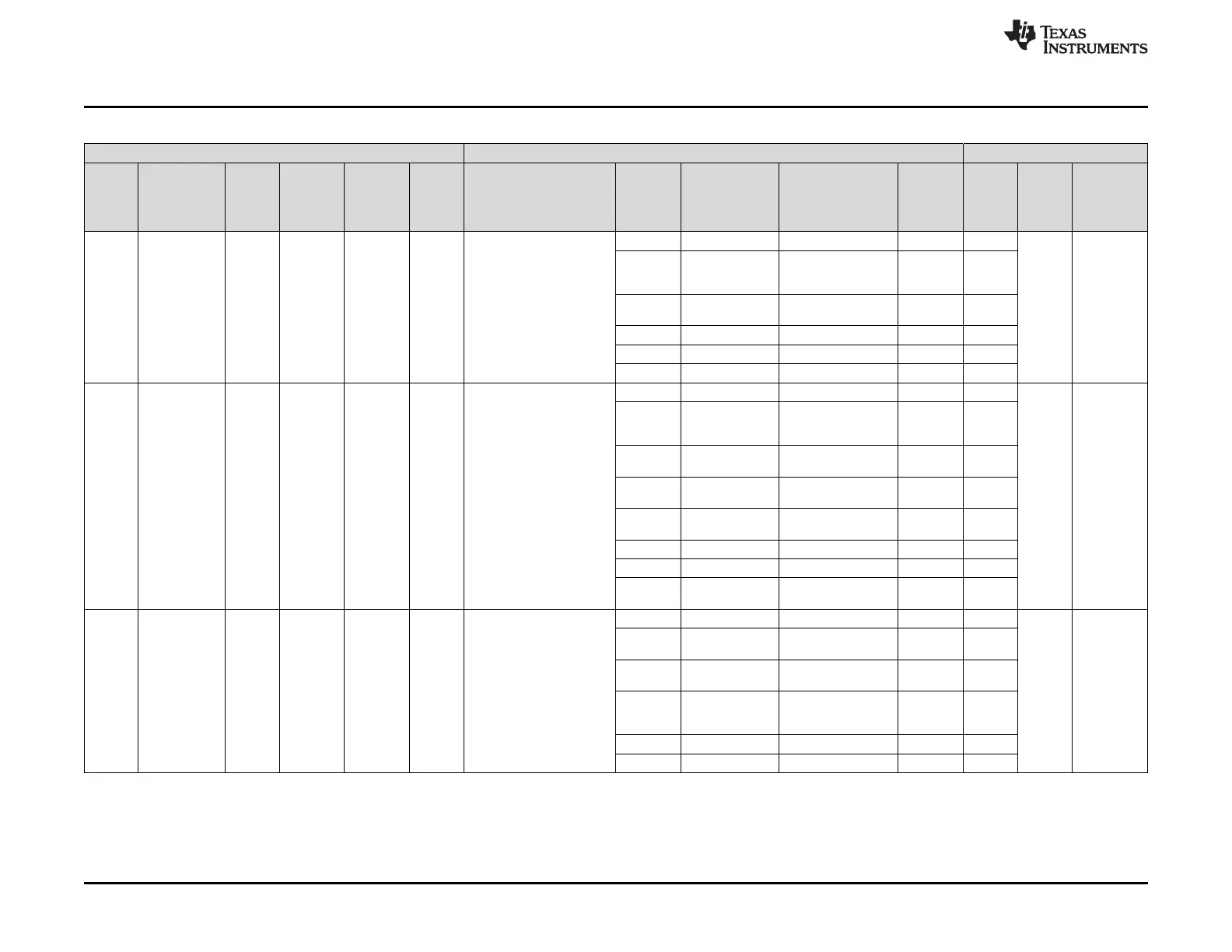

2 GPIO11 I/O Yes No No

GPIO_PAD_CONFIG_11

(0x4402 E0CC)

0 GPIO11 General-Purpose I/O I/O Hi-Z

Hi-Z Hi-Z

1 I2C_SDA I2C Data I/O

(Open

Drain)

Hi-Z

3 GT_PWM07 Pulse-Width

Modulated O/P

O Hi-Z

4 pXCLK (XVCLK) Free Clock To Parallel

Camera

O 0

6 SDCARD_CMD SD Card Command

Line

I/O Hi-Z

7 UART1_RX UART RX Data I Hi-Z

12 GT_CCP02 Timer Capture Port I Hi-Z

13 McAFSX I2S Audio Port Frame

Sync

O Hi-Z

3 GPIO12 I/O No No No

GPIO_PAD_CONFIG_12

(0x4402 E0D0)

0 GPIO12 General-Purpose I/O I/O Hi-Z

Hi-Z Hi-Z

3 McACLK I2S Audio Port Clock

O

O Hi-Z

4 pVS (VSYNC) Parallel Camera

Vertical Sync

I Hi-Z

5 I2C_SCL I2C Clock I/O

(Open

Drain)

Hi-Z

7 UART0_TX UART0 TX Data O 1

12 GT_CCP03 Timer Capture Port I Hi-Z

Loading...

Loading...