Functional Description

www.ti.com

56

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Cortex

®

-M4 Processor

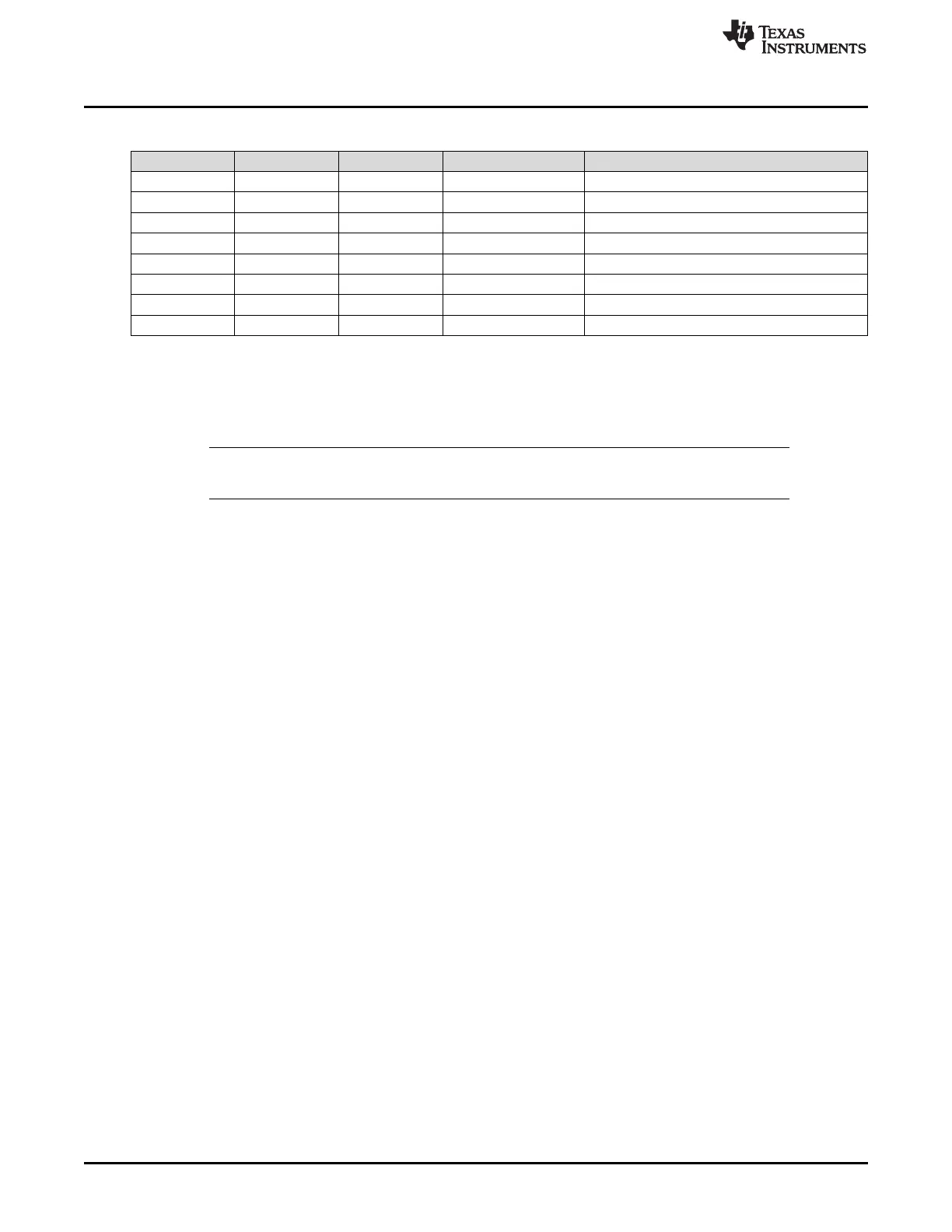

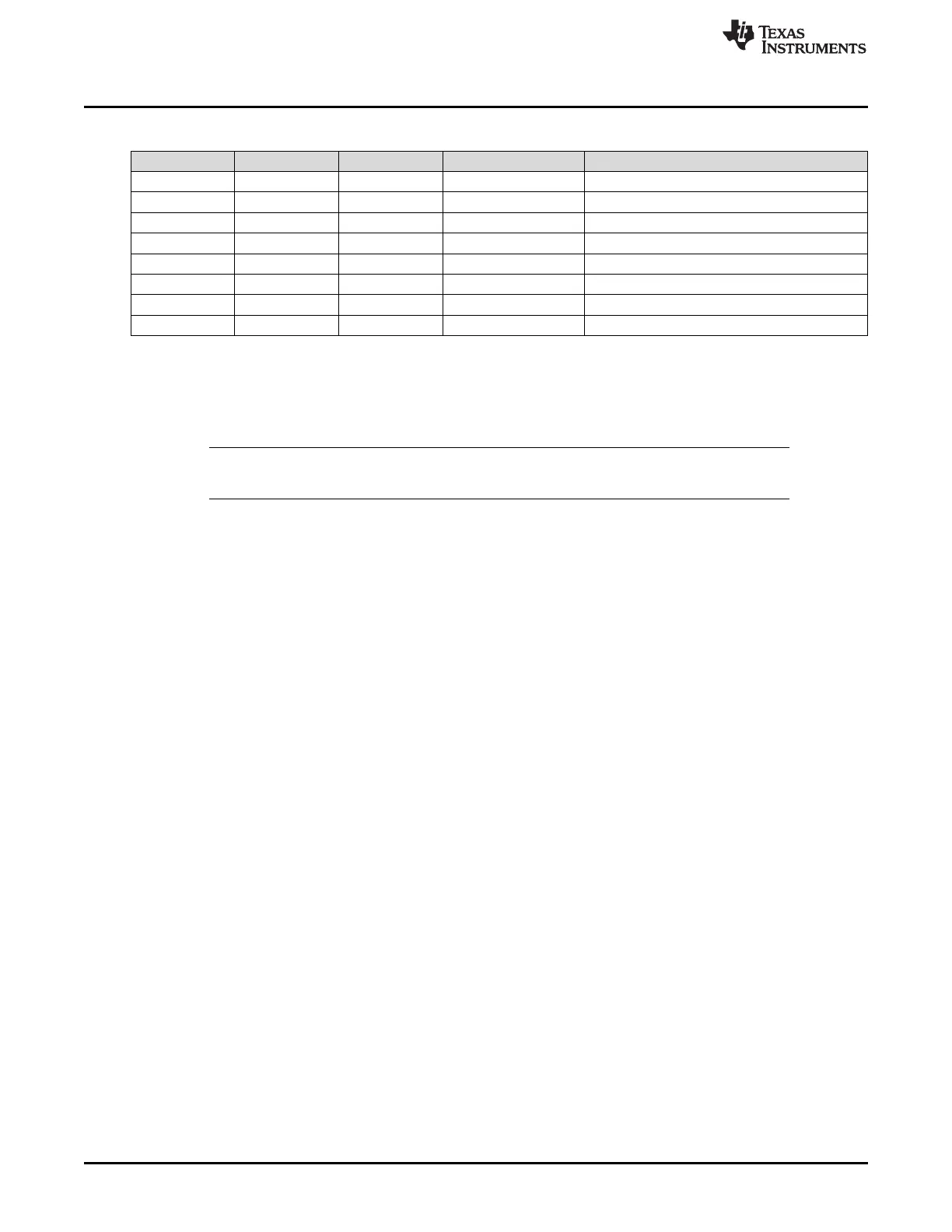

Table 2-2. Processor Register Map (continued)

Offset Name Type Reset Description

– LR R/W 0xFFFF.FFFF Link register

– PC R/W – Program counter

– PSR R/W 0x0100.0000 Program Status register

– PRIMASK R/W 0x0000.0000 Priority Mask register

– FAULTMASK R/W 0x0000.0000 Fault Mask register

– BASEPRI R/W 0x0000.0000 Base Priority Mask register

– CONTROL R/W 0x0000.0000 Control register

– FPSC R/W – Floating-Point Status Control (N/A for CC32xx)

2.2.2.2 Register Descriptions

This section lists and describes the Cortex

®

-M4 registers. The core registers are not memory-mapped, and

are accessed by register name rather than offset.

NOTE: The register type shown in the register descriptions refers to type during program execution

in thread mode and handler mode. Debug access may differ.

The R0–R12 registers are 32-bit general-purpose registers for data operations, and can be accessed from

either privileged or unprivileged mode.

2.2.2.2.1 Stack Pointer (SP)

In thread mode, the function of this register changes depending on the ASP bit in the Control (CONTROL)

register. When the ASP bit is clear, this register is the main stack pointer (MSP). When the ASP bit is set,

this register is the process stack pointer (PSP). On reset, the ASP bit is clear, and the processor loads the

MSP with the value from address 0x0000 0000. The MSP can be accessed only in privileged mode; the

PSP can be accessed in either privileged or unprivileged mode.

2.2.2.2.2 Link Register (LR)

The Link register (LR) stores the return information for subroutines, function calls, and exceptions. The

Link register can be accessed from either privileged or unprivileged mode.

EXC_RETURN is loaded into the LR on exception entry.

2.2.2.2.3 Program Counter (PC)

The program counter (PC) register contains the current program address. On reset, the processor loads

the PC with the value of the reset vector, which is at address 0x0000 0004. Bit 0 of the reset vector is

loaded into the THUMB bit of the EPSR at reset and must be 1. The PC register can be accessed in either

privileged or unprivileged mode.

Loading...

Loading...