UART Registers

www.ti.com

186

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Universal Asynchronous Receivers/Transmitters (UARTs)

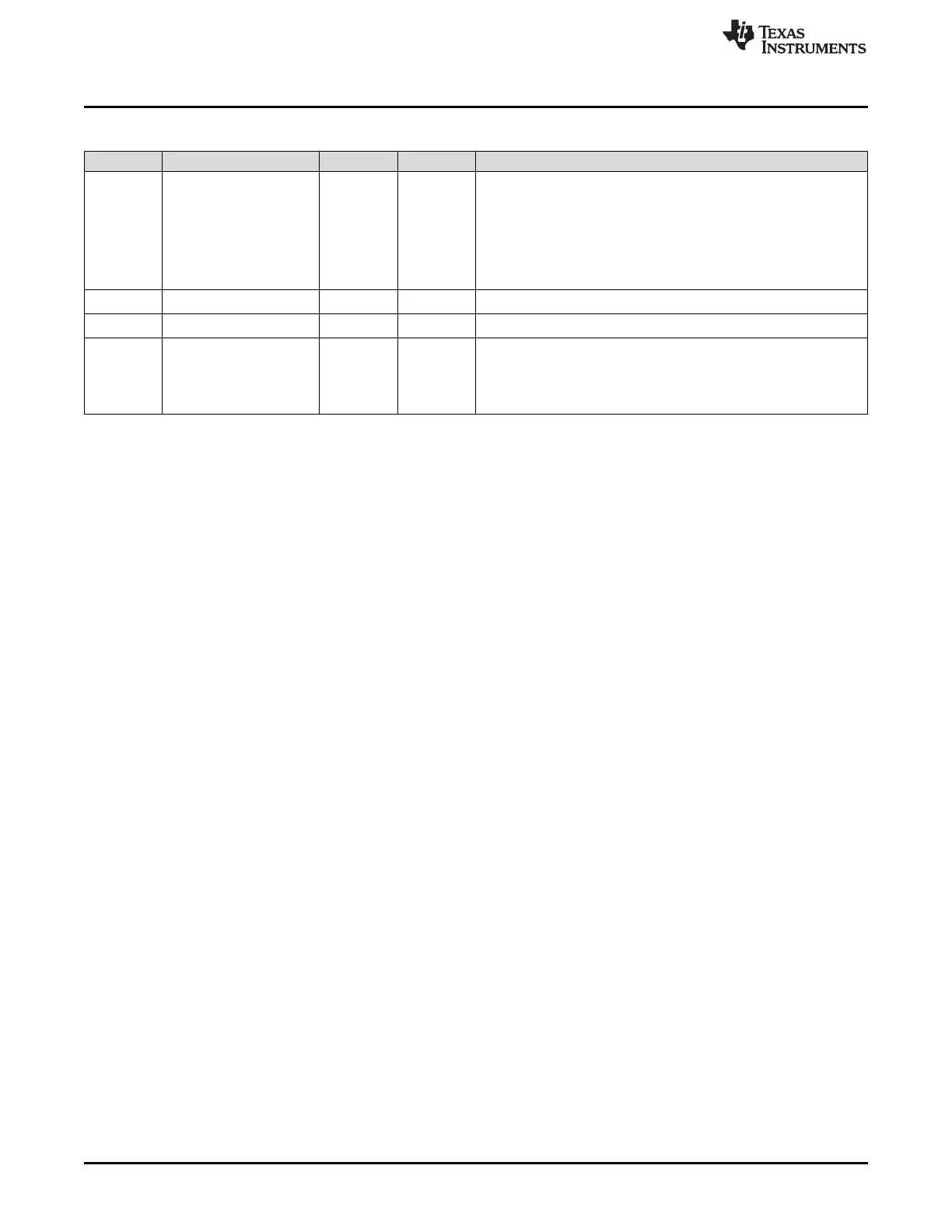

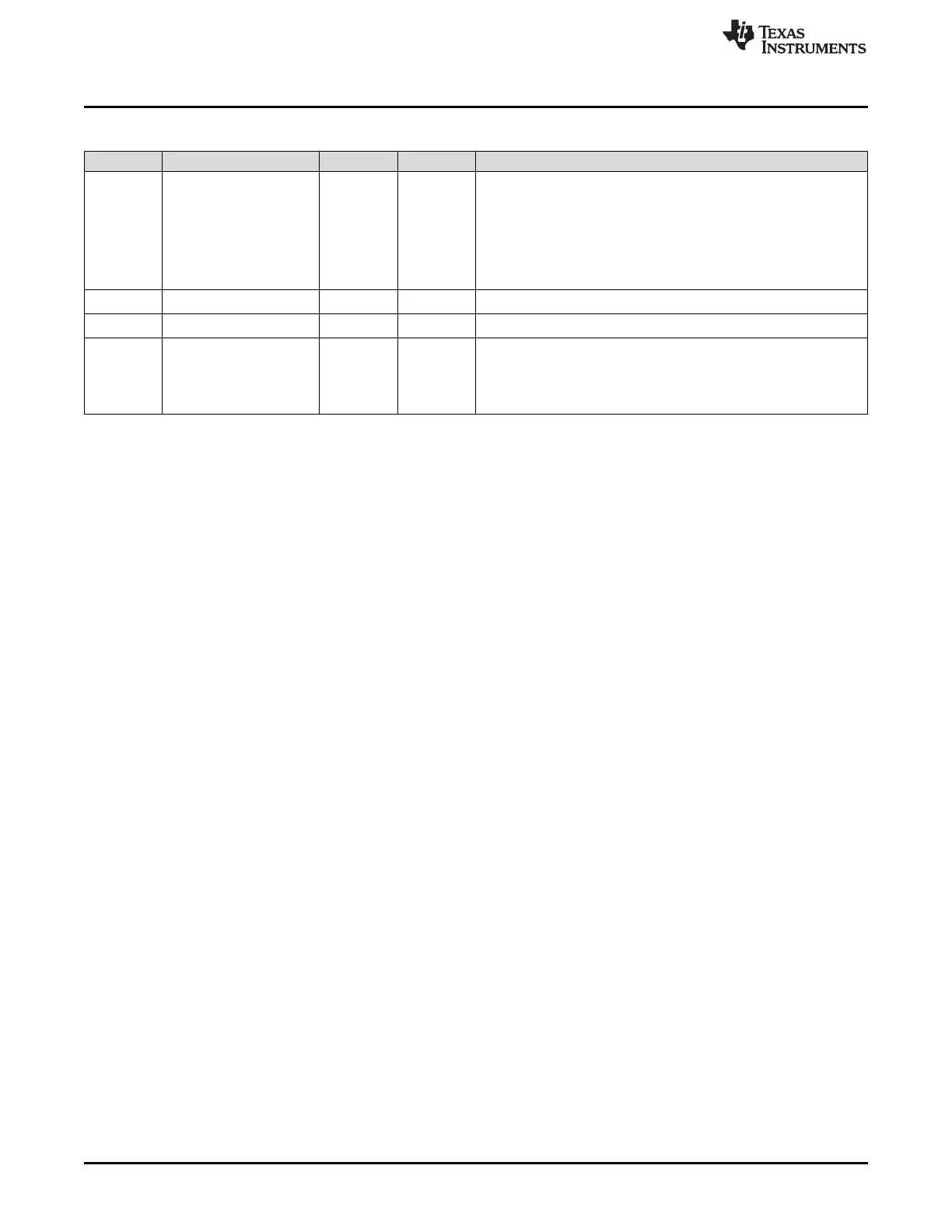

Table 6-5. UARTFR Register Field Descriptions (continued)

Bit Field Type Reset Description

3 BUSY R 0h

UART Busy

This bit is set when the transmit FIFO becomes non-empty

(regardless of whether UART is enabled).

0h = The UART is not busy.

1h = The UART is busy transmitting data. This bit remains set until

the complete byte, including all stop bits, has been sent from the

shift register.

2 DCD R 0h

Reserved

1 DSR R 0h

Reserved

0 CTS R 0h

Clear To Send

This bit is implemented only on UART1 and is reserved for UART0

0h = The U1CTS signal is not asserted.

1h = The U1CTS signal is asserted.

Loading...

Loading...