I2C Registers

www.ti.com

232

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Inter-Integrated Circuit (I

2

C) Interface

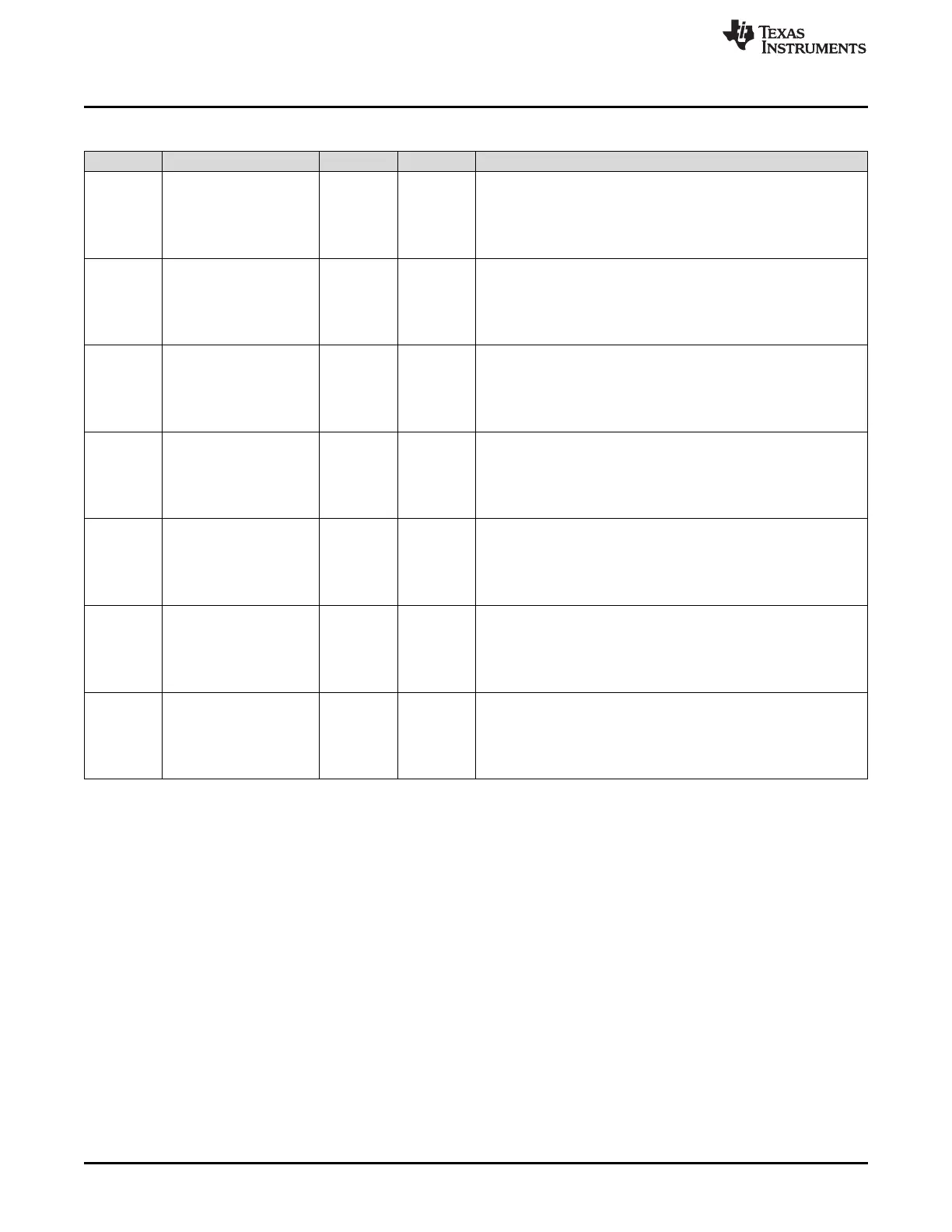

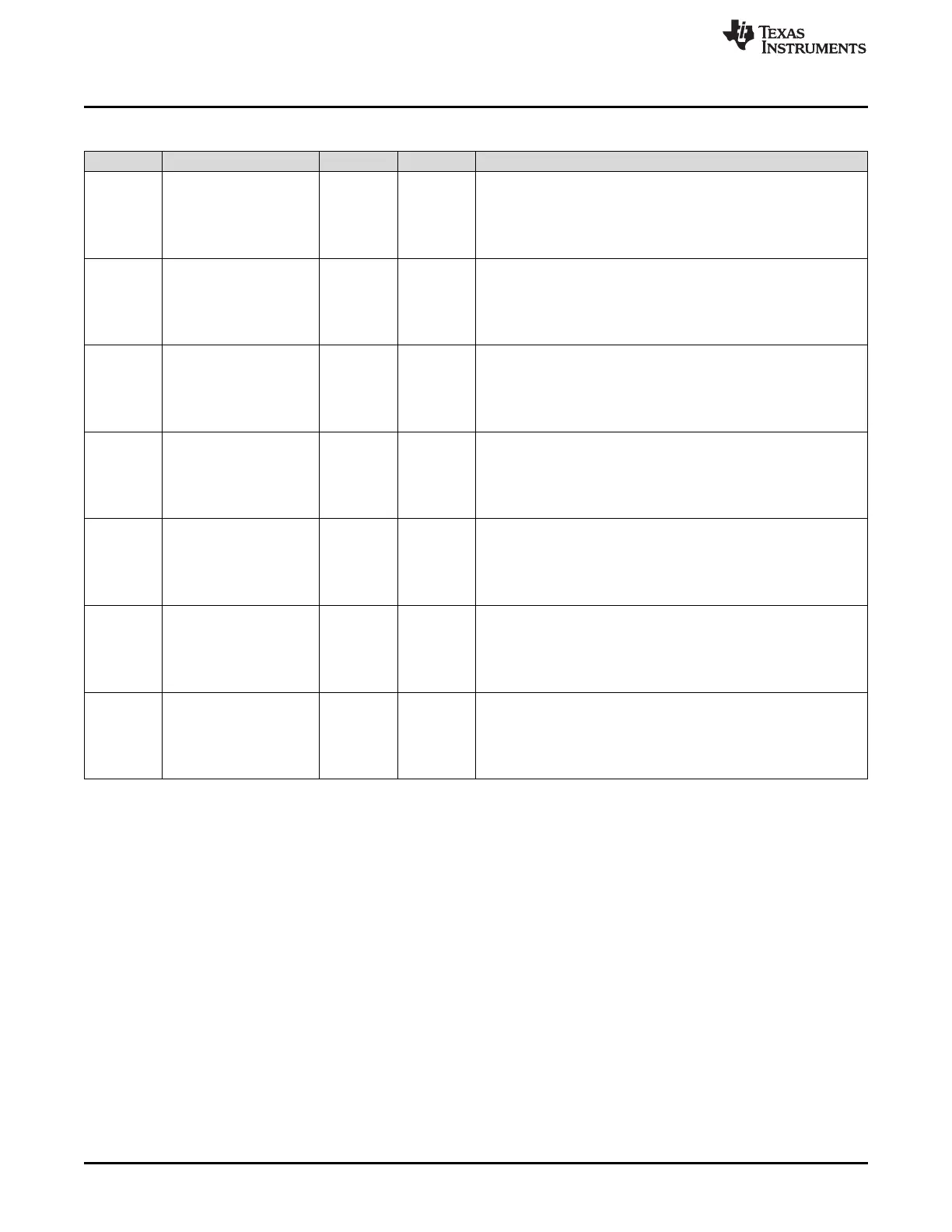

Table 7-9. I2CMIMR Register Field Descriptions (continued)

Bit Field Type Reset Description

6 STOPIM R/W 0h

STOP Detection Interrupt Mask

0h = The STOPRIS interrupt is suppressed and not sent to the

interrupt controller.

1h = The STOP detection interrupt is sent to the interrupt controller

when the STOPRIS bit in the I2CMRIS register is set.

5 STARTIM R/W 0h

START Detection Interrupt Mask

0h = The STARTRIS interrupt is suppressed and not sent to the

interrupt controller.

1h = The START detection interrupt is sent to the interrupt controller

when the STARTRIS bit in the I2CMRIS register is set.

4 NACKIM R/W 0h

Address/Data NACK Interrupt Mask

0h = The NACKRIS interrupt is suppressed and not sent to the

interrupt controller.

1h = The address/data NACK interrupt is sent to the interrupt

controller when the NACKRIS bit in the I2CMRIS register is set.

3 DMATXIM R/W 0h

Transmit DMA Interrupt Mask

0h = The DMATXRIS interrupt is suppressed and not sent to the

interrupt controller.

1h = The transmit DMA complete interrupt is sent to the interrupt

controller when the DMATXRIS bit in the I2CMRIS register is set.

2 DMARXIM R/W 0h

Receive DMA Interrupt Mask

0h = The DMARXRIS interrupt is suppressed and not sent to the

interrupt controller.

1h = The receive DMA complete interrupt is sent to the interrupt

controller when the DMARXRIS bit in the I2CMRIS register is set.

1 CLKIM R/W 0h

Clock Timeout Interrupt Mask

0h = The CLKRIS interrupt is suppressed and not sent to the

interrupt controller.

1h = The clock timeout interrupt is sent to the interrupt controller

when the CLKRIS bit in the I2CMRIS register is set.

0 IM R/W 0h

Master Interrupt Mask

0h = The RIS interrupt is suppressed and not sent to the interrupt

controller.

1h = The master interrupt is sent to the interrupt controller when the

RIS bit in the I2CMRIS register is set.

Loading...

Loading...