I2C Registers

www.ti.com

246

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Inter-Integrated Circuit (I

2

C) Interface

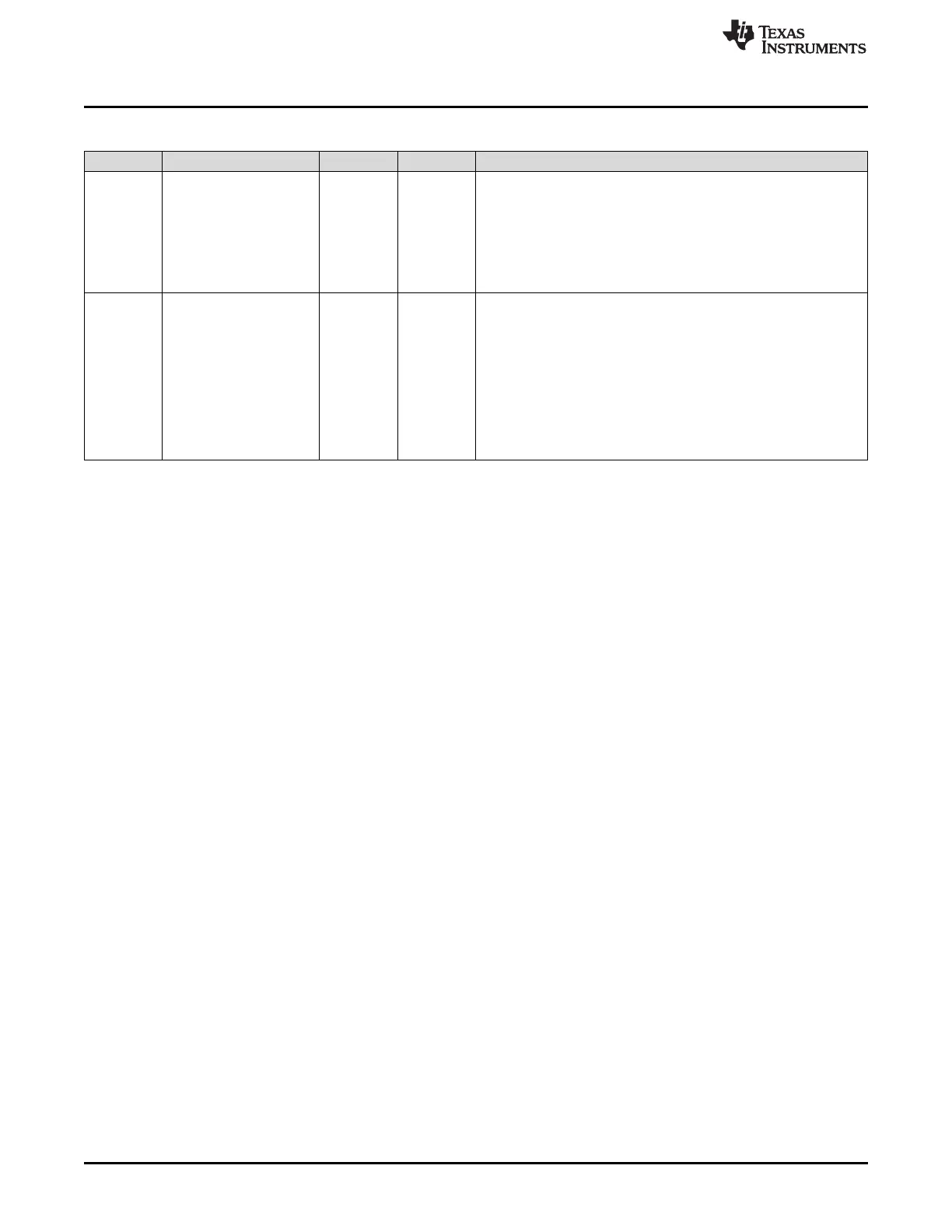

Table 7-19. I2CSCSR Register Field Descriptions (continued)

Bit Field Type Reset Description

1 TREQ_OR_TXFIFO R/W 0h

Transmit Request (R) or TX FIFO Enable (W)

0h (W) = Disables TX FIFO

0h (R) = No outstanding transmit request.

1h (W) = Enables TX FIFO

1h (R) = The I2C controller has been addressed as a slave

transmitter and is using clock stretching to delay the master until

data has been written to the I2CSDR register.

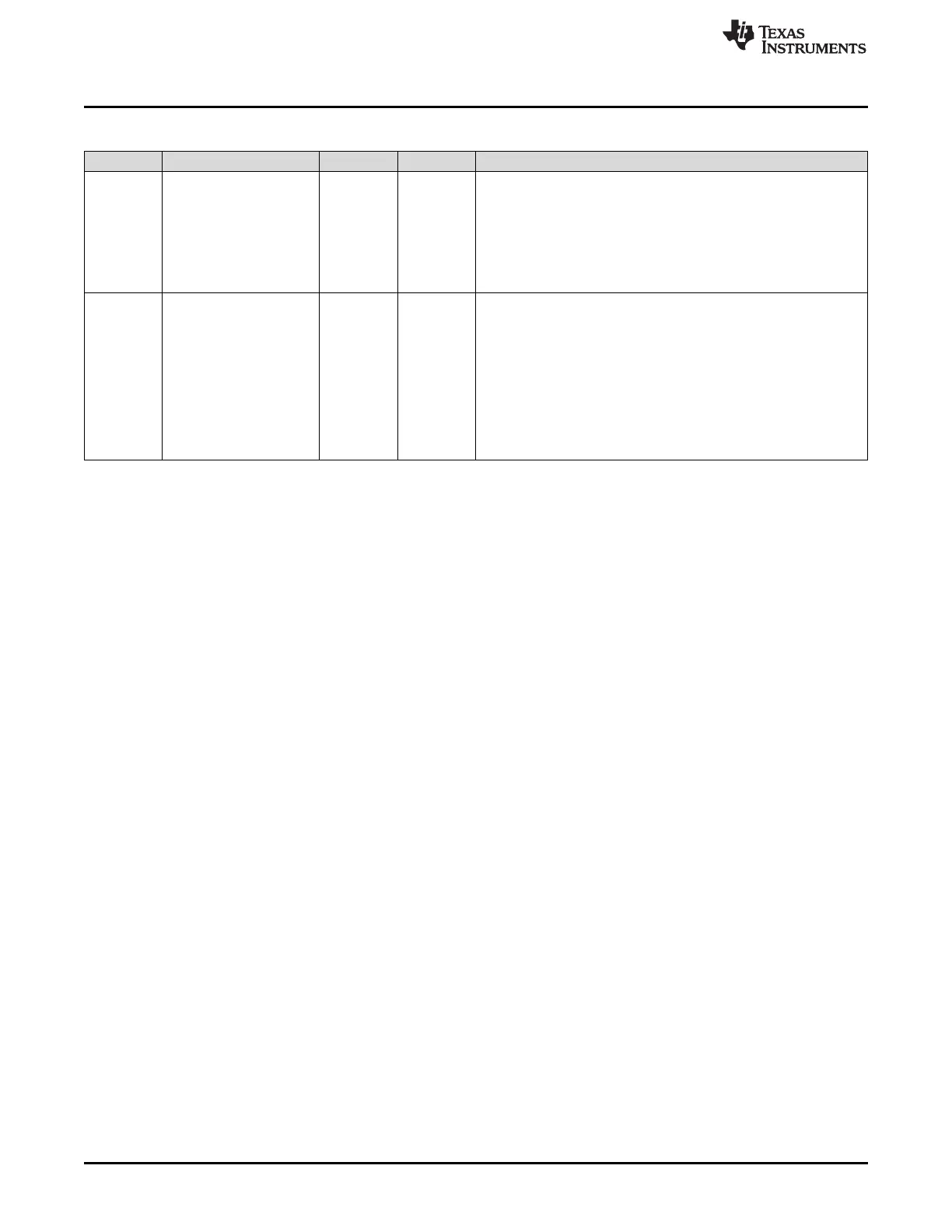

0 RREQ_OR_DA R/W 0h

Receive Request (R) or Device Active (W)

Once this bit has been set, it should not be set again unless it has

been cleared by writing a 0 or by a reset, otherwise transfer failures

may occur.

0h (W) = Disables the I2C slave operation.

0h (R) = No outstanding receive data.

1h (W) = Enables the I2C slave operation.

1h (R) = The I2C controller has outstanding receive data from the

I2C master and is using clock stretching to delay the master until the

data has been read from the I2CSDR register.

Loading...

Loading...