www.ti.com

I2C Registers

251

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Inter-Integrated Circuit (I

2

C) Interface

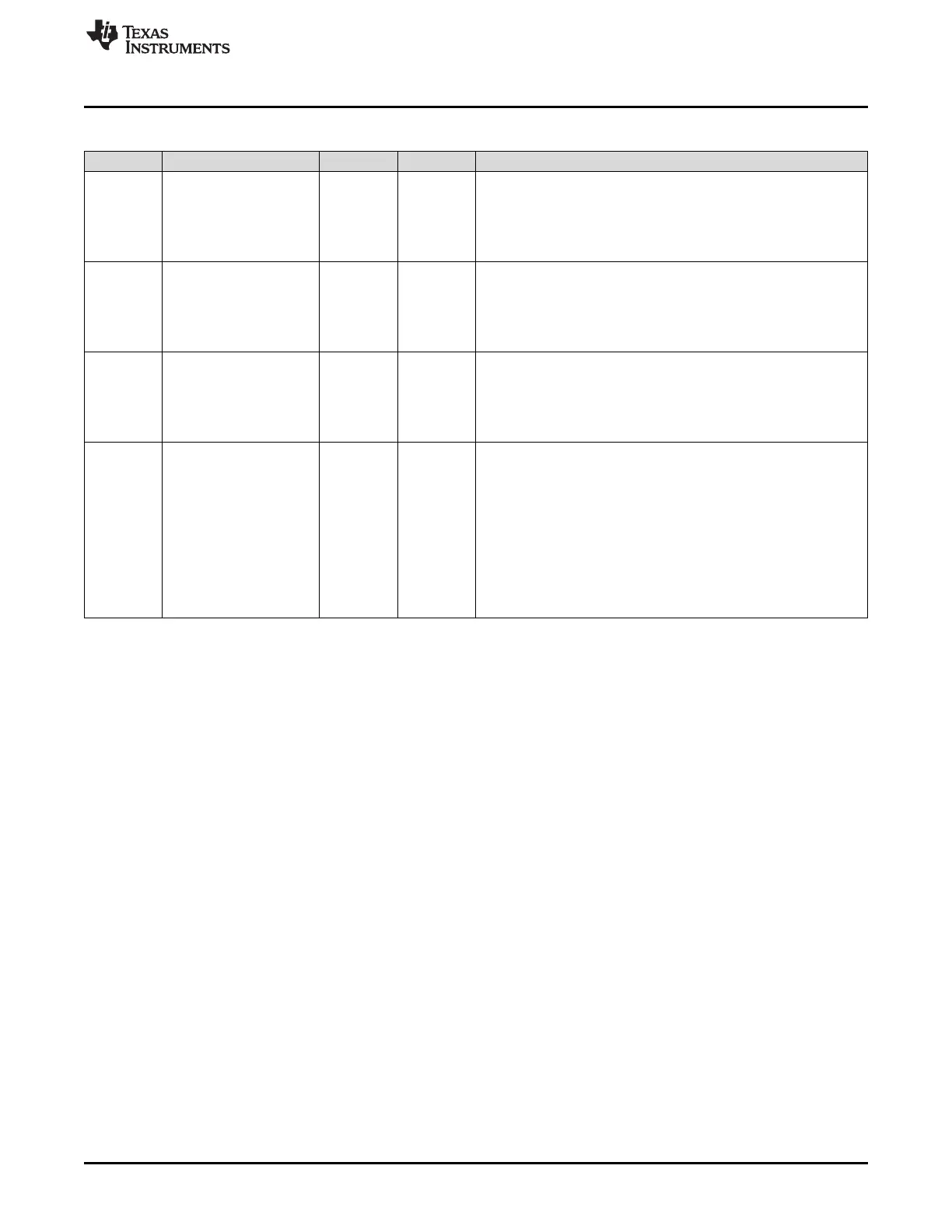

Table 7-22. I2CSRIS Register Field Descriptions (continued)

Bit Field Type Reset Description

3 DMARXRIS R 0h

Receive DMA Raw Interrupt Status

This bit is cleared by writing a 1 to the DMARXIC bit in the I2CSICR

register.

0h = No interrupt

1h = A receive DMA complete interrupt is pending.

2 STOPRIS R 0h

Stop Condition Raw Interrupt Status

This bit is cleared by writing a 1 to the STOPIC bit in the I2CSICR

register.

0h = No interrupt

1h = A STOP condition interrupt is pending.

1 STARTRIS R 0h

Start Condition Raw Interrupt Status

This bit is cleared by writing a 1 to the STARTIC bit in the I2CSICR

register.

0h = No interrupt.

1h = A START condition interrupt is pending.

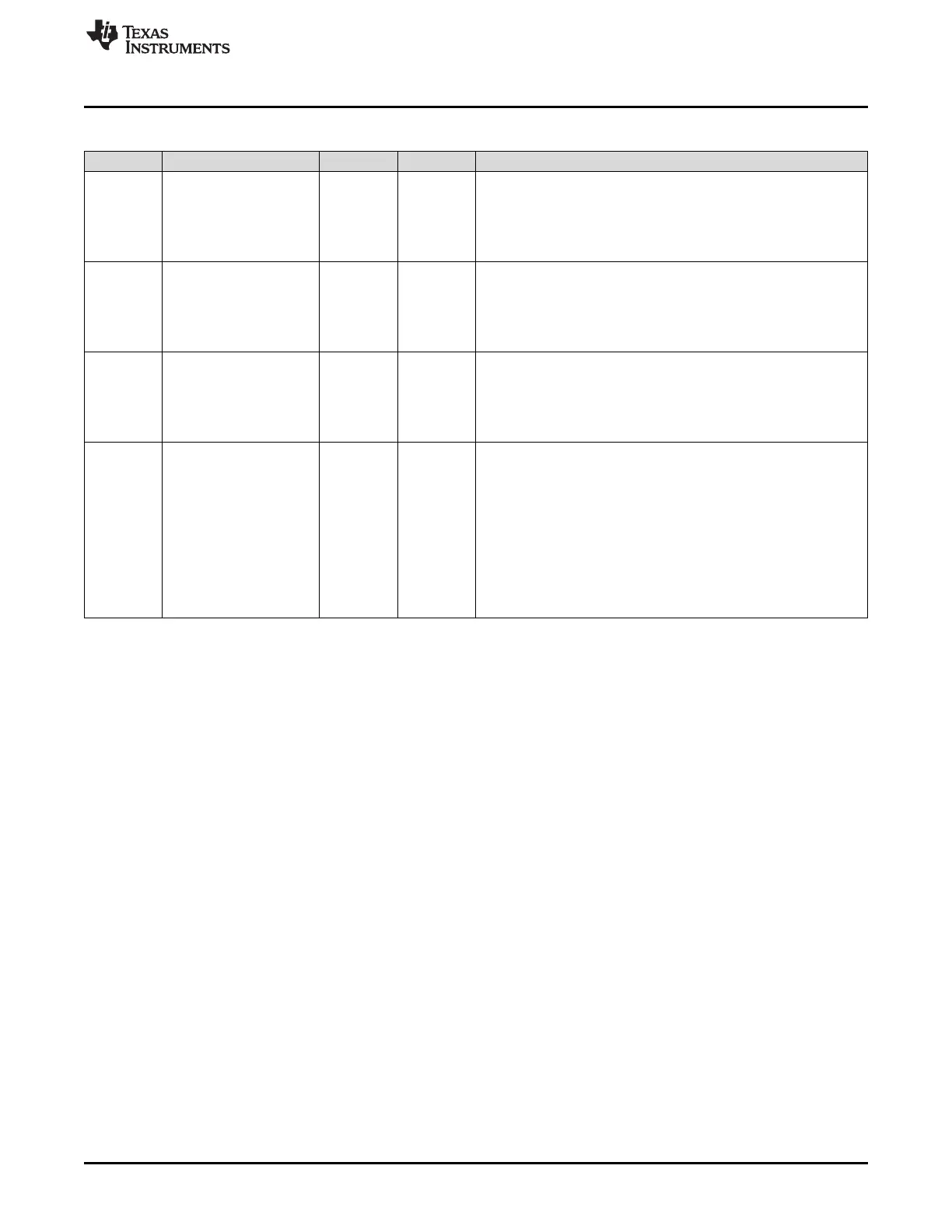

0 DATARIS R 0h

Data Raw Interrupt Status

This interrupt encompasses the following:

• slave transaction received

• slave transaction requested

• next byte transfer request

This bit is cleared by writing a 1 to the DATAIC bit in the I2CSICR

register.

0h = No interrupt.

1h = Slave Interrupt is pending.

Loading...

Loading...