www.ti.com

I2C Registers

253

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Inter-Integrated Circuit (I

2

C) Interface

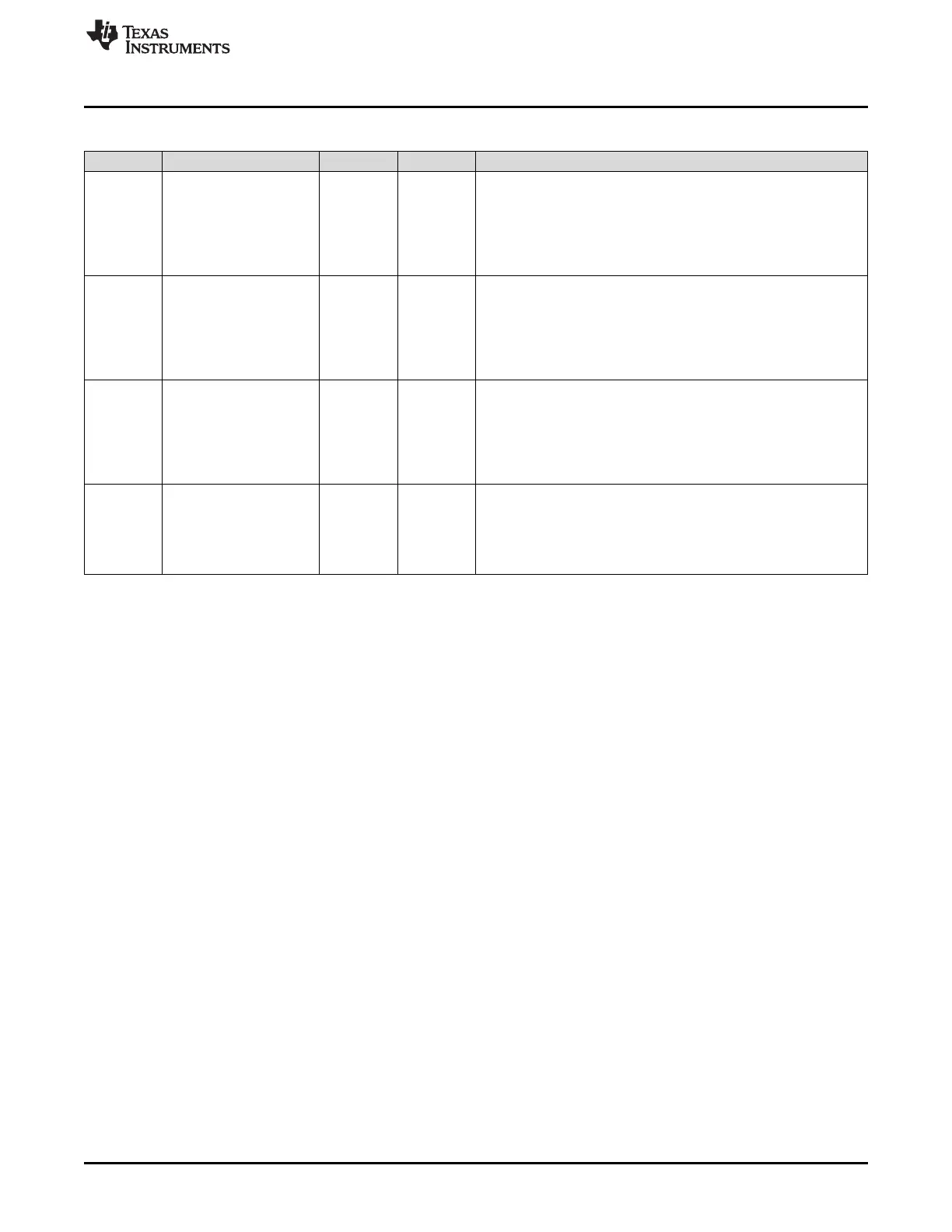

Table 7-23. I2CSMIS Register Field Descriptions (continued)

Bit Field Type Reset Description

3 DMARXMIS R 0h

Receive DMA Masked Interrupt Status

This bit is cleared by writing a 1 to the DMARXIC bit in the I2CSICR

register.

0h = An interrupt has not occurred or is masked.

1h = An unmasked receive DMA complete interrupt was signaled is

pending.

2 STOPMIS R 0h

Stop Condition Masked Interrupt Status

This bit is cleared by writing a 1 to the STOPIC bit in the I2CSICR

register.

0h = An interrupt has not occurred or is masked.

1h = An unmasked STOP condition interrupt was signaled is

pending.

1 STARTMIS R 0h

Start Condition Masked Interrupt Status

This bit is cleared by writing a 1 to the STARTIC bit in the I2CSICR

register.

0h = An interrupt has not occurred or is masked.

1h = An unmasked START condition interrupt was signaled is

pending.

0 DATAMIS R 0h

Data Masked Interrupt Status

This bit is cleared by writing a 1 to the DATAIC bit in the I2CSICR

register.

0h = An interrupt has not occurred or is masked.

1h = An unmasked slave data interrupt was signaled is pending.

Loading...

Loading...