Timer Registers

www.ti.com

322

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

General-Purpose Timers

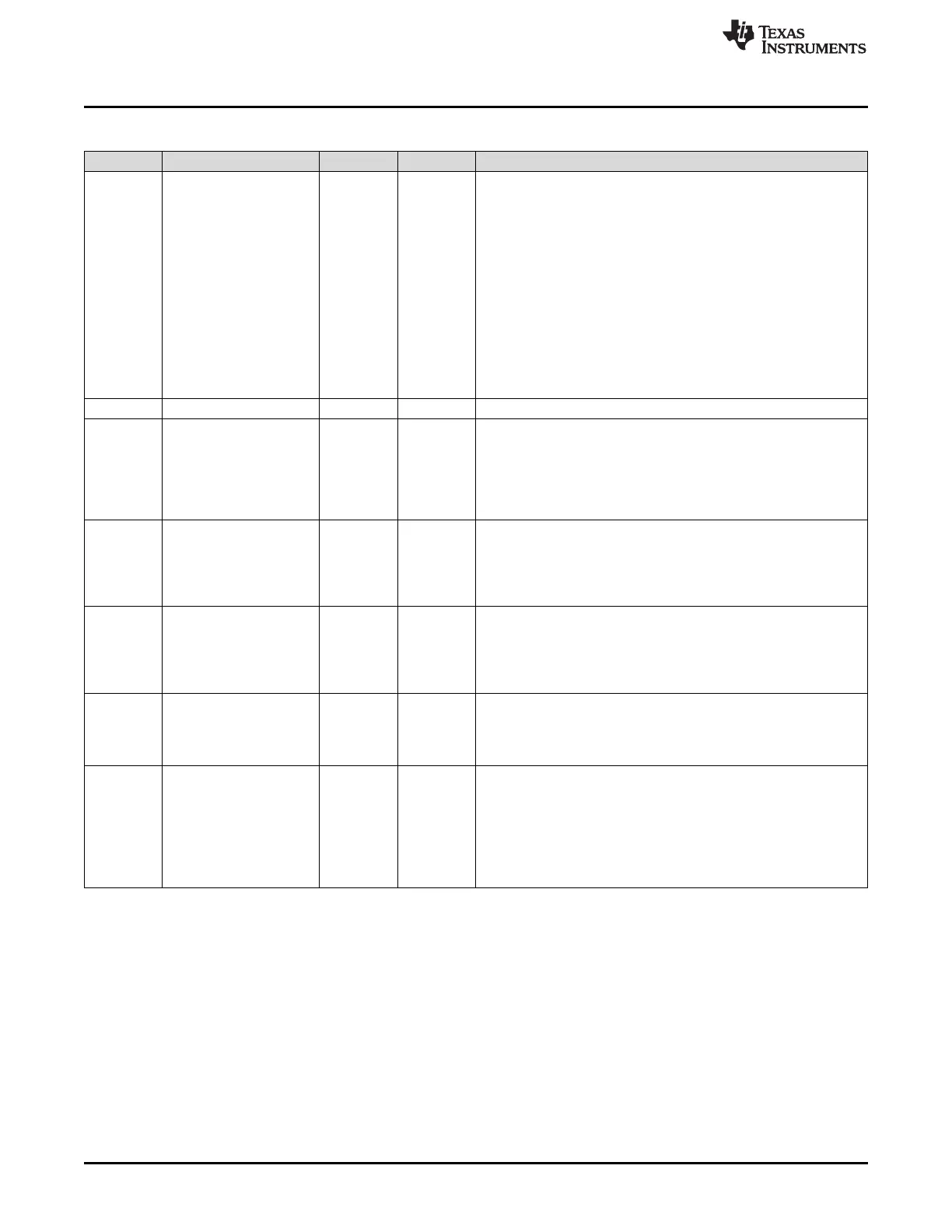

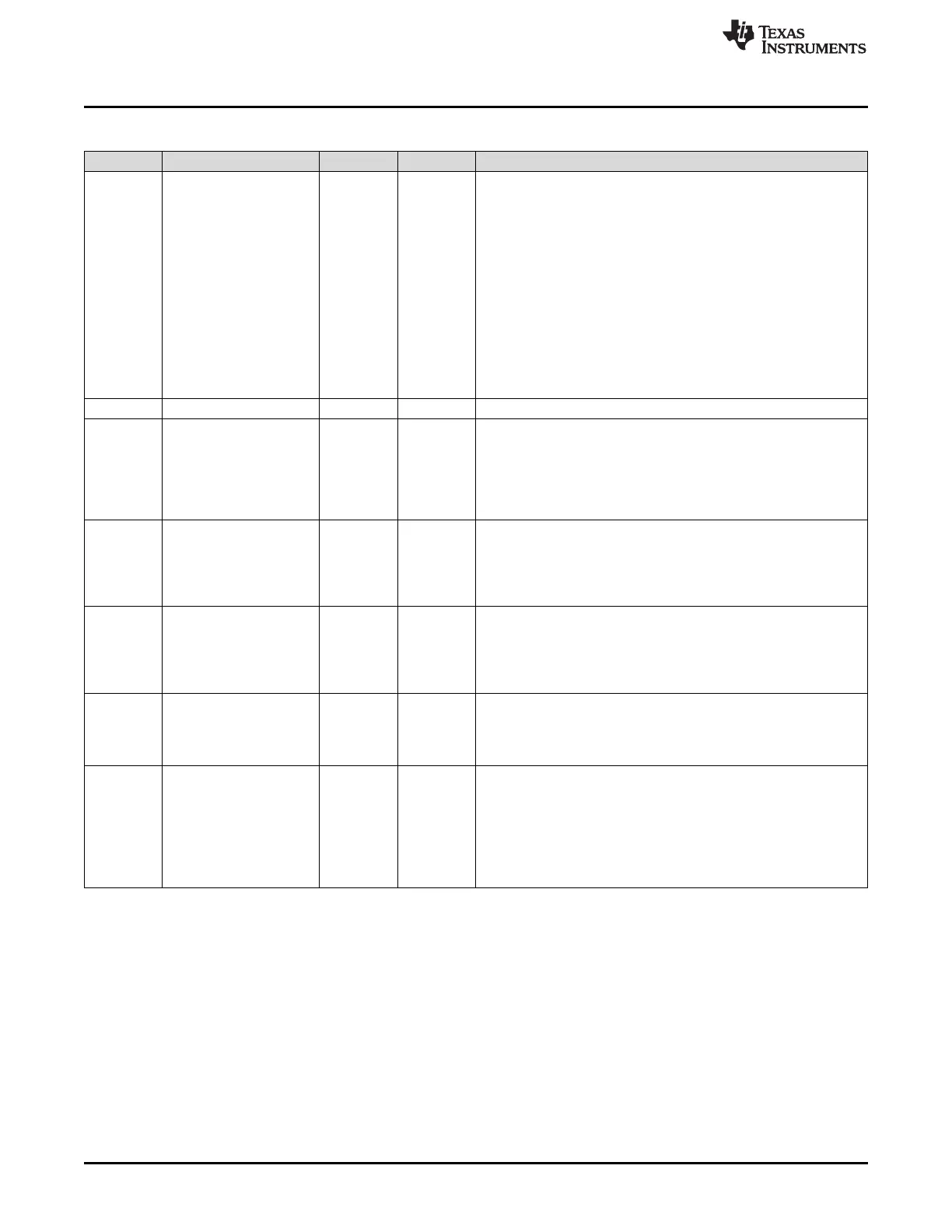

Table 9-11. GPTMTBMR Register Field Descriptions (continued)

Bit Field Type Reset Description

8 TBILD R/W 0h

GPTM Timer B Interval Load Write. The state of this bit has no effect

when counting up. The bit descriptions above apply if the timer is

enabled and running. If the timer is disabled (TBEN is clear) when

this bit is set, GPTMTBR, GPTMTBV, and GPTMTBPS are updated

when the timer is enabled. If the timer is stalled (TBSTALL is set),

GPTMTBR and GPTMTBPS are updated according to the

configuration of this bit.

0h = Update the GPTMTBR and GPTMTBV registers with the value

in the GPTMTBILR register on the next cycle. Also update the

GPTMTBPS register with the value in the GPTMTBPR register on

the next cycle.

1h = Update the GPTMTBR and GPTMTBV registers with the value

in the GPTMTBILR register on the next time-out. Also update the

GPTMTBPS register with the value in the GPTMTBPR register on

the next time-out.

7-6 RESERVED R 0h

5 TBMIE R/W 0h

GPTM Timer B Match Interrupt Enable

0h = The match interrupt is disabled for match events. Additionally,

triggers to the DMA on match events are prevented.

1h = An interrupt is generated when the match value in the

GPTMTBMATCHR register is reached in the one-shot and periodic

modes.

4 TBCDIR R/W 0h

GPTM Timer B Count Direction

0h = The timer counts down.

1h = The timer counts up. When counting up, the timer starts from a

value of 0x0. When in PWM mode, the status of this bit is ignored.

PWM mode always counts down.

3 TBAMS R/W 0h

GPTM Timer B Alternate Mode Select. The TBAMS values are

defined as follows. To enable PWM mode, clear the TBCMR bit and

configure the TBMR field to 0x1 or 0x2.

0h = Capture or compare mode is enabled.

1h = PWM mode is enabled.

2 TBCMR R/W 0h

GPTM Timer B Capture Mode. The TBCMR values are defined as

follows:

0h = Edge-count mode

1h = Edge-time mode

1-0 TBMR R/W 0h

GPTM Timer B Mode. The TBMR values are defined as follows. The

timer mode is based on the timer configuration defined by bits 2:0 in

the GPTMCFG register.

0h = Reserved

1h = One-shot timer mode

2h = Periodic timer mode

3h = Capture mode

Loading...

Loading...