SD-HOST Registers

www.ti.com

396

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

SD Host Controller Interface

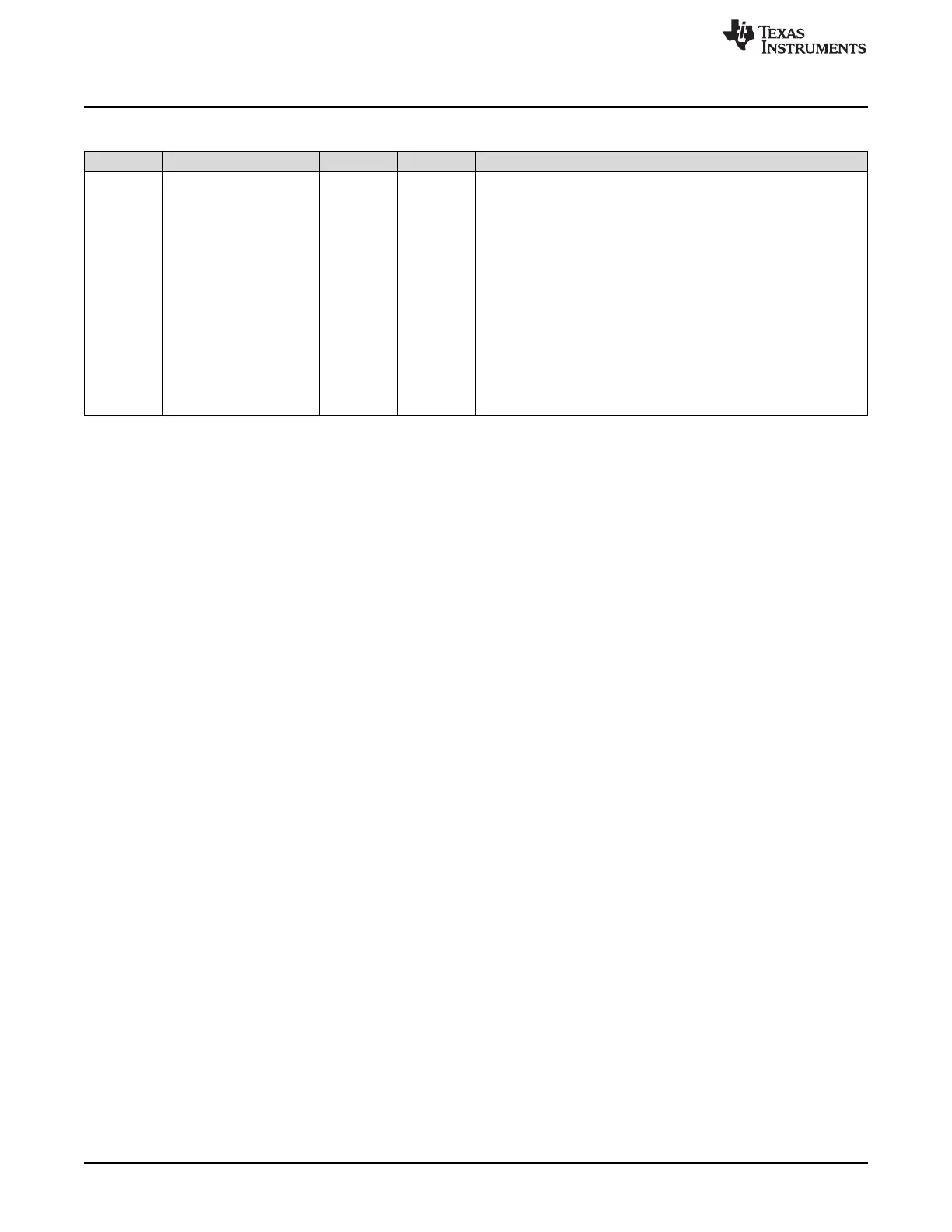

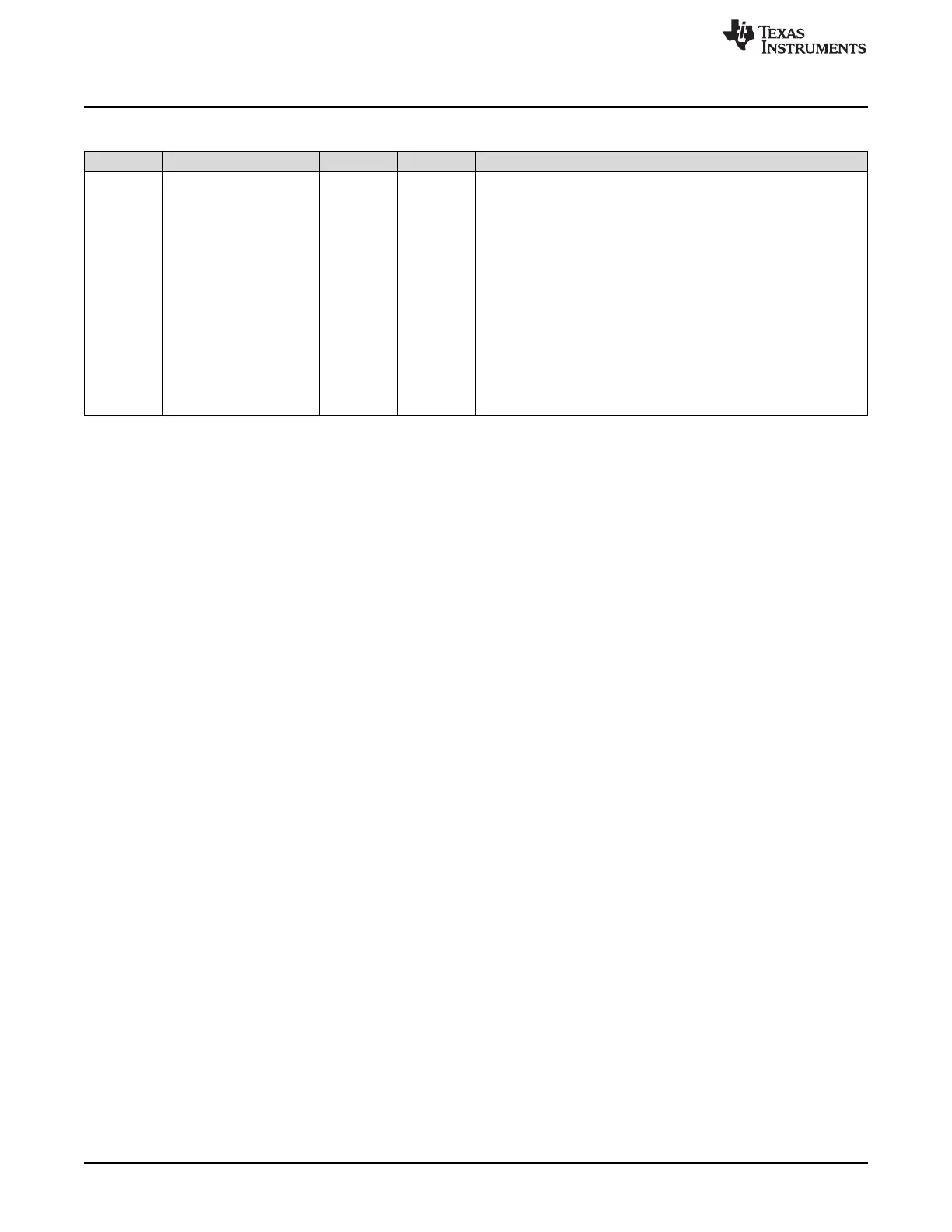

Table 11-18. MMCHS_STAT Register Field Descriptions (continued)

Bit Field Type Reset Description

0 CC R/W 0h

Command complete

This bit is set when a 1-to-0 transition occurs in the register

command inhibit (MMCi.MMCHS_PSTATE[0] CMDI bit)

If the command is a type for which no response is expected, then the

command complete interrupt is generated at the end of the

command. A command time-out error (MMCi.MMCHS_STAT[16]

CTO bit) has higher priority than command complete

(MMCi.MMCHS_STAT[0] CC bit).

If a response is expected but none is received, then a command

time-out error is detected and signaled instead of the command

complete interrupt.

Read 0h = No command complete

Write 0h = Status bit unchanged

Read 1h = Command complete

Write 1h = Status is cleared

Loading...

Loading...