SD-HOST Registers

www.ti.com

400

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

SD Host Controller Interface

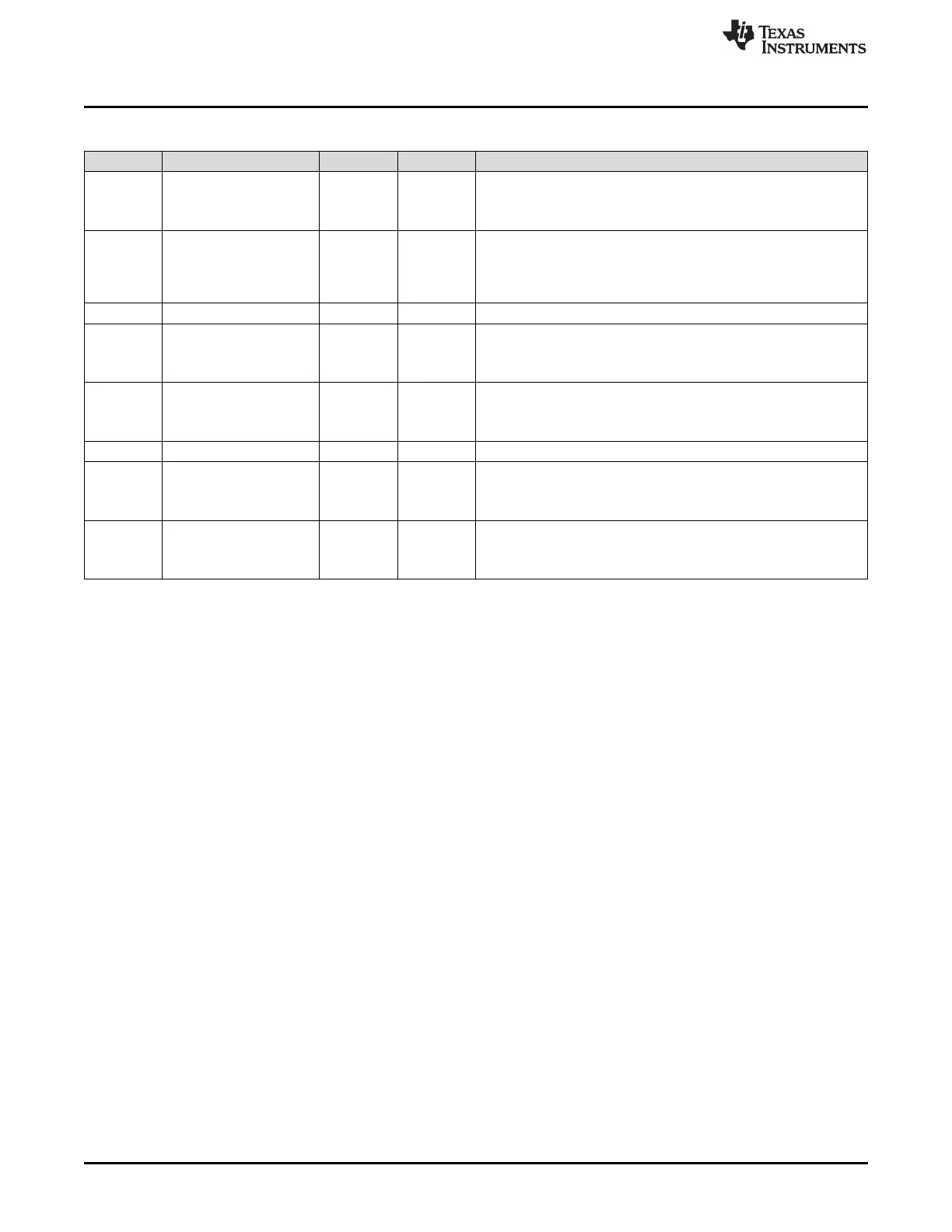

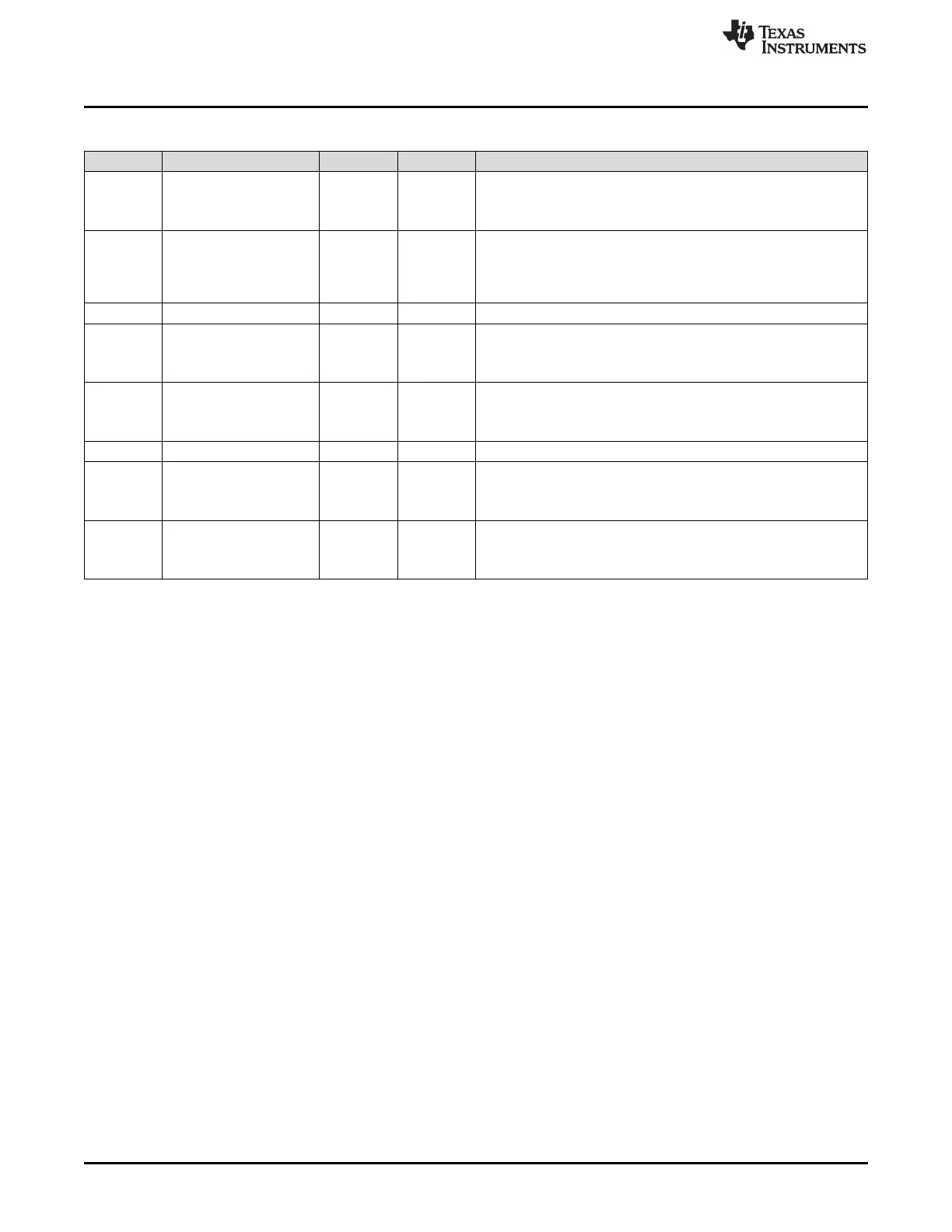

Table 11-20. MMCHS_ISE Register Field Descriptions (continued)

Bit Field Type Reset Description

16 CTO_SIGEN R/W 0h

Command time-out error signal status enable

0h = Masked

1h = Enabled

15 NULL R 0h

Fixed to 0

The host driver controls the error interrupts using the Error Interrupt

Signal Enable register.

Writes to this bit are ignored.

14-6 RESERVED R 0h

5 BRR_SIGEN R/W 0h

Buffer read ready signal status enable

0h = Masked

1h = Enabled

4 BWR_SIGEN R/W 0h

Buffer write ready signal status enable

0h = Masked

1h = Enabled

3-2 RESERVED R 0h

1 TC_SIGEN R/W 0h

Transfer completed signal status enable

0h = Masked

1h = Enabled

0 CC_SIGEN R/W 0h

Command completed signal status enable

0h = Masked

1h = Enabled

Loading...

Loading...