www.ti.com

Register Map

113

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Cortex

®

-M4 Peripherals

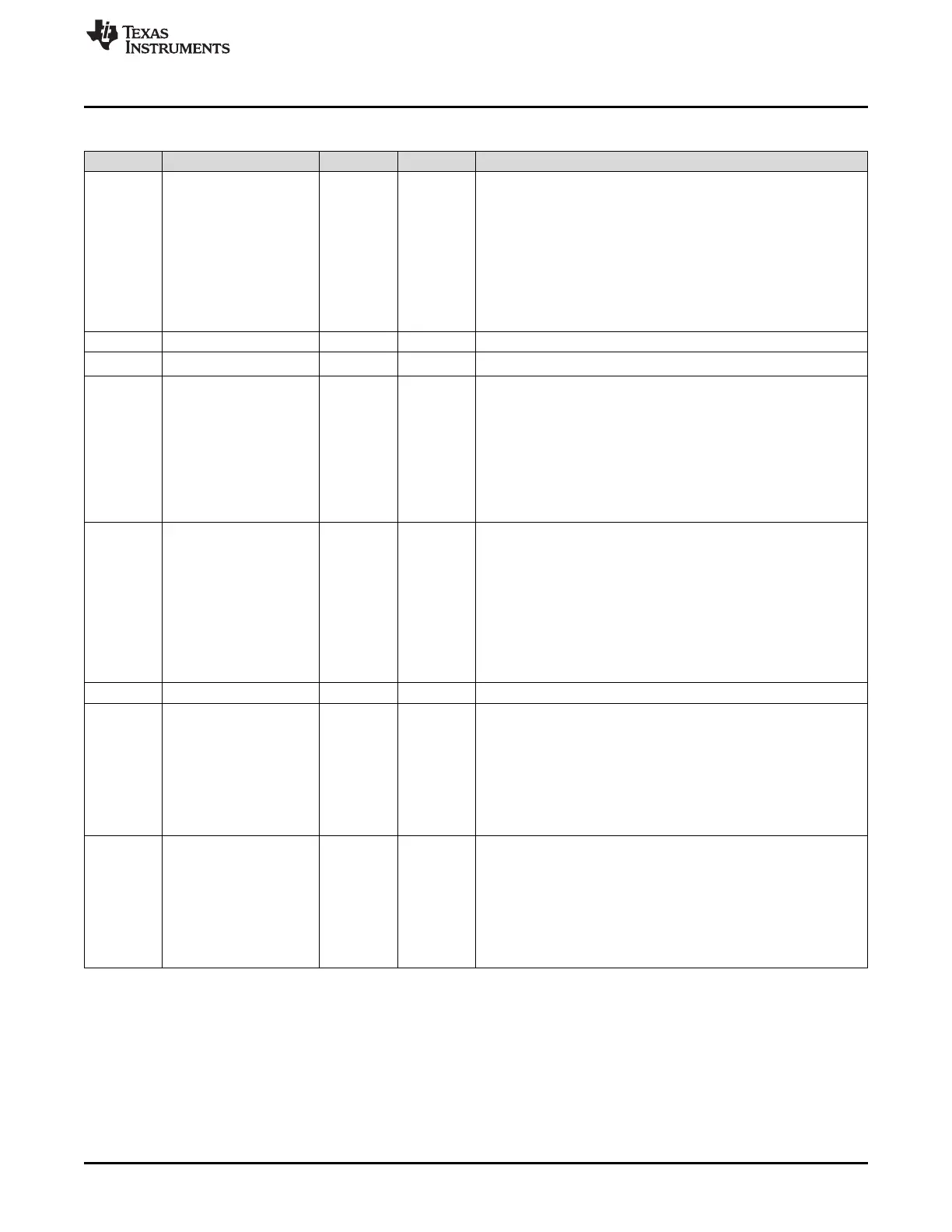

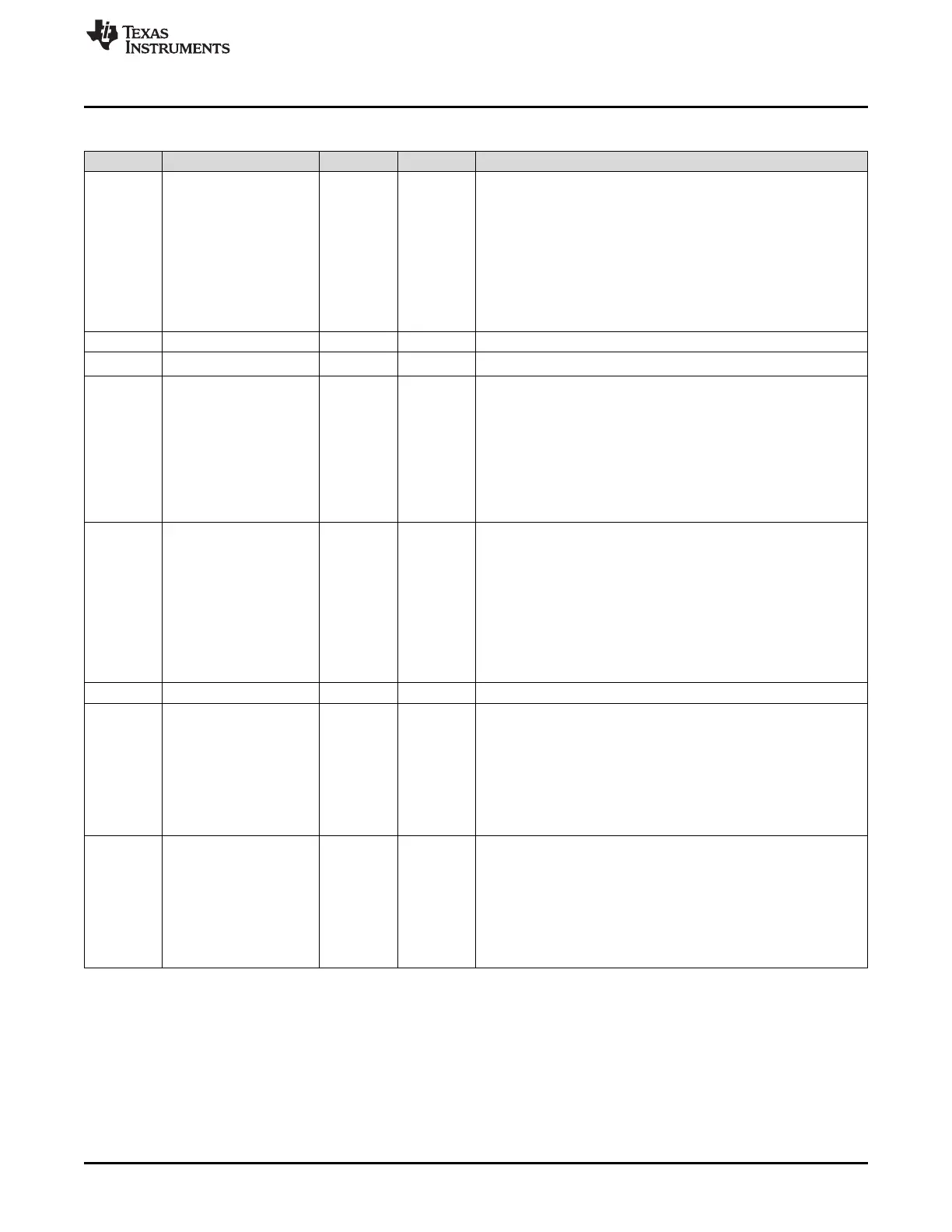

Table 3-24. FAULTSTAT Register Field Descriptions (continued)

Bit Field Type Reset Description

7 MMARV R/W1C 0h

Memory Management Fault Address Register Valid

If a memory management fault occurs and is escalated to a hard

fault because of priority, the hard fault handler must clear this bit.

This action prevents problems if returning to a stacked active

memory management fault handler whose MMADDR register value

has been overwritten.

0h = The This bit is cleared by writing a 1 to it. value in the Memory

Management Fault Address (MMADDR) register is not a valid fault

address.

1h = The MMADDR register is holding a valid fault address.

6 RESERVED R 0h

5 MLSPERR R/W1C 0h

N/A

4 MSTKE R/W1C 0h

Stack Access Violation

When this bit is set, the SP is still adjusted but the values in the

context area on the stack might be incorrect. A fault address is not

written to the MMADDR register. This bit is cleared by writing a 1 to

it.

0h = No memory management fault has occurred on stacking for

exception entry.

1h = Stacking for an exception entry has caused one or more access

violations.

3 MUSTKE R/W1C 0h

Unstack Access Violation

This fault is chained to the handler. Thus, when this bit is set, the

original return stack is still present. The SP is not adjusted from the

failing return, a new save is not performed, and a fault address is not

written to the MMADDR register. This bit is cleared by writing a 1 to

it.

0h = No memory management fault has occurred on unstacking for a

return from exception.

1h = Unstacking for a return from exception has caused one or more

access violations.

2 RESERVED R 0h

1 DERR R/W1C 0h

Data Access Violation

When this bit is set, the PC value stacked for the exception return

points to the faulting instruction and the address of the attempted

access is written to the MMADDR register. This bit is cleared by

writing a 1 to it.

0h = A data access violation has not occurred.

1h = The processor attempted a load or store at a location that does

not permit the operation.

0 IERR R/W1C 0h

Instruction Access Violation

This fault occurs on any access to an XN region. When this bit is set,

the PC value stacked for the exception return points to the faulting

instruction and the address of the attempted access is not written to

the MMADDR register. This bit is cleared by writing a 1 to it.

0h = An instruction access violation has not occurred.

1h = The processor attempted an instruction fetch from a location

that does not permit execution.

Loading...

Loading...