www.ti.com

Functional Description

75

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Cortex

®

-M4 Processor

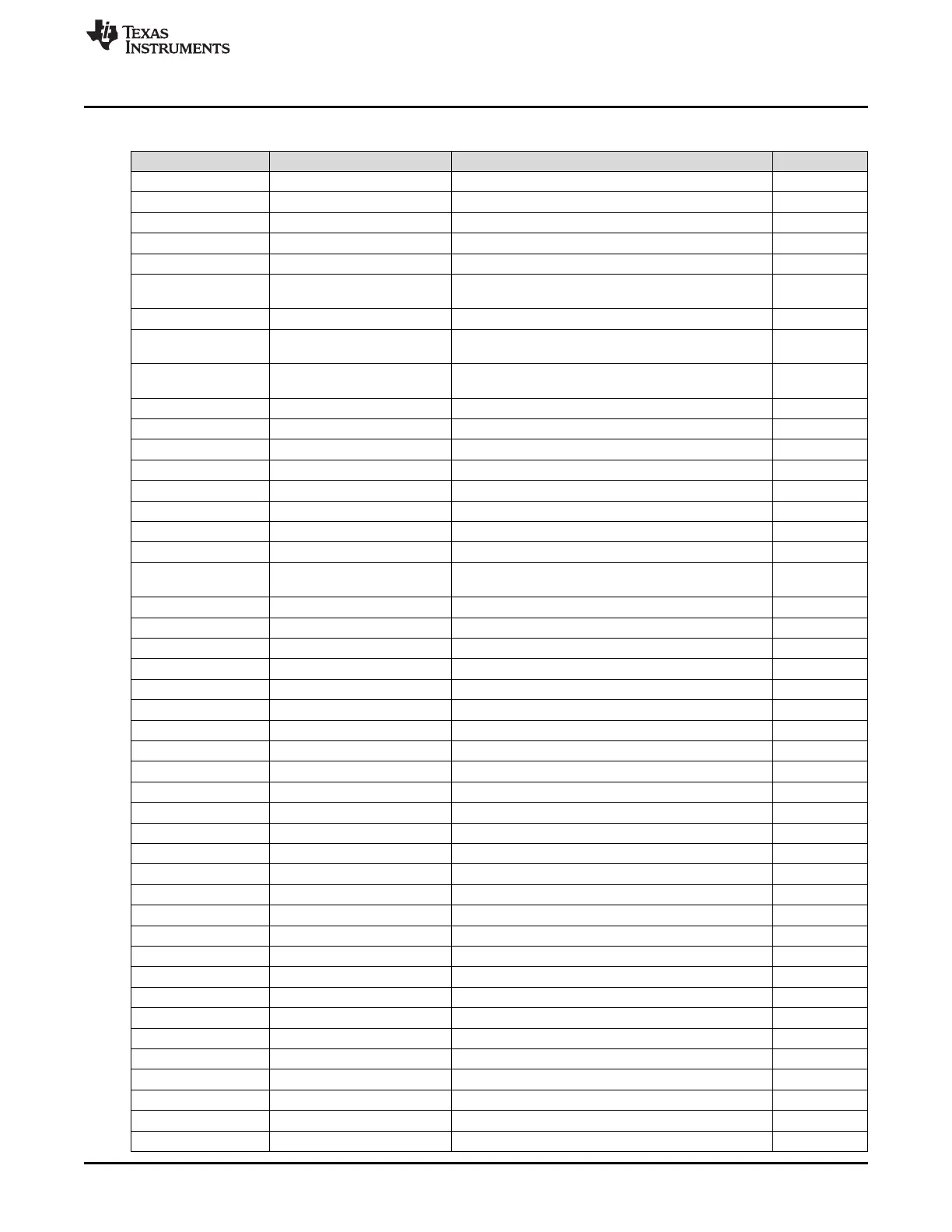

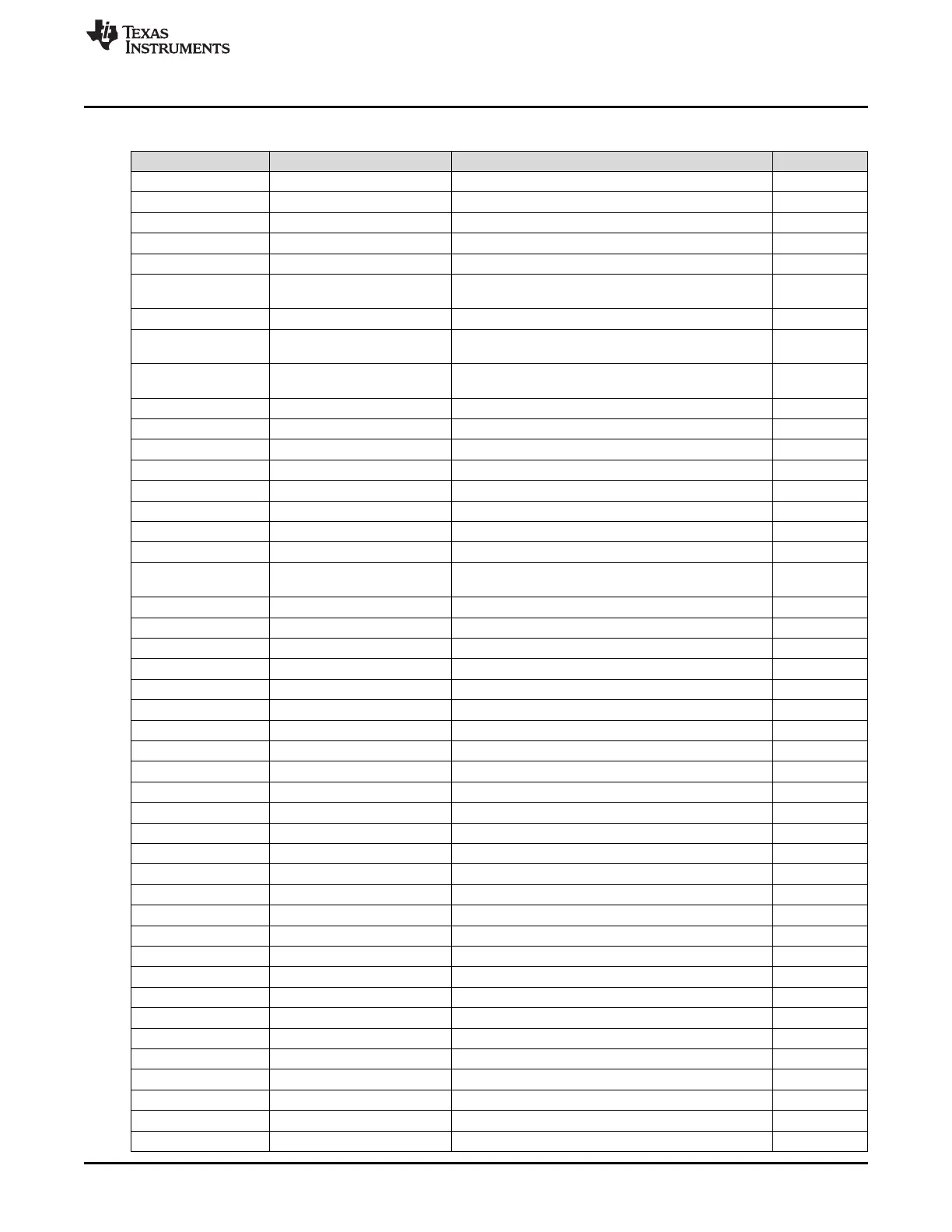

Table 2-10. Cortex

®

-M4 Instruction Summary (continued)

Mnemonic Operands Brief Description Flags

SHADD8 {Rd,} Rn, Rm Signed halving add 8 –

SHASX {Rd,} Rn, Rm Signed halving add and subtract with exchange –

SHSAX {Rd,} Rn, Rm Signed halving add and subtract with exchange –

SHSUB16 {Rd,} Rn, Rm Signed halving subtract 16 –

SHSUB8 {Rd,} Rn, Rm Signed halving subtract 8 –

SMLABB, SMLABT,

SMLATB, SMLATT

Rd, Rn, Rm, Ra Signed multiply accumulate long (halfwords) Q

SMLAD, SMLADX Rd, Rn, Rm, Ra Signed multiply accumulate dual Q

SMLAL RdLo, RdHi, Rn, Rm Signed long multiply with accumulate (32×32+64), 64-bit

result

–

SMLALBB, SMLALBT,

SMLALTB, SMLALTT

RdLo, RdHi, Rn, Rm Signed multiply accumulate long (halfwords) –

SMLALD, SMLALDX RdLo, RdHi, Rn, Rm Signed multiply accumulate long dual –

SMLAWB, SMLAWT Rd, Rn, Rm, Ra Signed multiply accumulate, word by halfword Q

SMLSD, SMLSDX Rd, Rn, Rm, Ra Signed multiply subtract dual Q

SMLSLD, SMLSLDX RdLo, RdHi, Rn, Rm Signed multiply subtract long dual Q

SMMLA Rd, Rn, Rm, Ra Signed most significant word multiply accumulate –

SMMLS, SMMLR Rd, Rn, Rm, Ra Signed most significant word multiply subtract –

SMMUL, SMMULR {Rd,} Rn, Rm Signed most significant word multiply –

SMUAD SMUADX {Rd,} Rn, Rm Signed dual multiply add Q

SMULBB, SMULBT,

SMULTB, SMULTT

{Rd,} Rn, Rm Signed multiply halfwords –

SMULL RdLo, RdHi, Rn, Rm Signed long multiply (32×32), 64-bit result –

SMULWB, SMULWT {Rd,} Rn, Rm Signed multiply by halfword –

SMUSD, SMUSDX {Rd,} Rn, Rm Signed dual multiply subtract –

SSAT Rd, #n, Rm {,shift #s} Signed saturate Q

SSAT16 Rd, #n, Rm Signed saturate 16 Q

SSAX {Rd,} Rn, Rm Saturating subtract and add with exchange GE

SSUB16 {Rd,} Rn, Rm Signed subtract 16 –

SSUB8 {Rd,} Rn, Rm Signed subtract 8 –

STM Rn{!}, reglist Store multiple registers, increment after –

STMDB, STMEA Rn{!}, reglist Store multiple registers, decrement before –

STMFD, STMIA Rn{!}, reglist Store multiple registers, increment after –

STR Rt, [Rn {, #offset}] Store register word –

STRB, STRBT Rt, [Rn {, #offset}] Store register byte –

STRD Rt, Rt2, [Rn {, #offset}] Store register two words –

STREX Rt, Rt, [Rn {, #offset}] Store register exclusive –

STREXB Rd, Rt, [Rn] Store register exclusive byte –

STREXH Rd, Rt, [Rn] Store register exclusive halfword –

STRH, STRHT Rt, [Rn {, #offset}] Store register halfword –

STRSB, STRSBT Rt, [Rn {, #offset}] Store register signed byte –

STRSH, STRSHT Rt, [Rn {, #offset}] Store register signed halfword –

STRT Rt, [Rn {, #offset}] Store register word –

SUB, SUBS {Rd,} Rn, Op2 Subtract N,Z,C,V

SUB, SUBW {Rd,} Rn, #imm12 Subtract 12-bit constant N,Z,C,V

SVC #imm Supervisor call –

SXTAB {Rd,} Rn, Rm, {,ROR #} Extend 8 bits to 32 and add –

SXTAB16 {Rd,} Rn, Rm,{,ROR #} Dual extend 8 bits to 16 and add –

SXTAH {Rd,} Rn, Rm,{,ROR #} Extend 16 bits to 32 and add –

Loading...

Loading...