Functional Description

www.ti.com

74

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Cortex

®

-M4 Processor

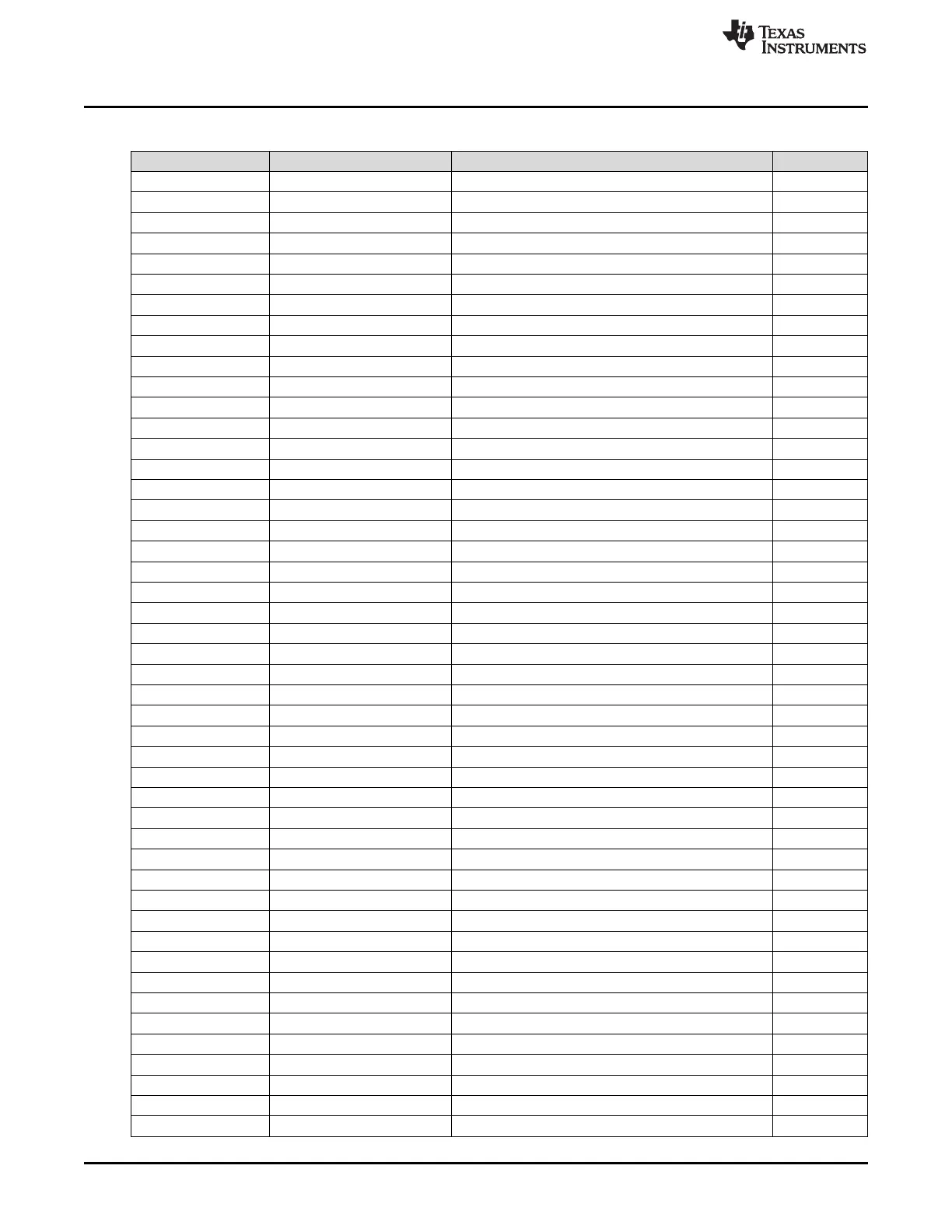

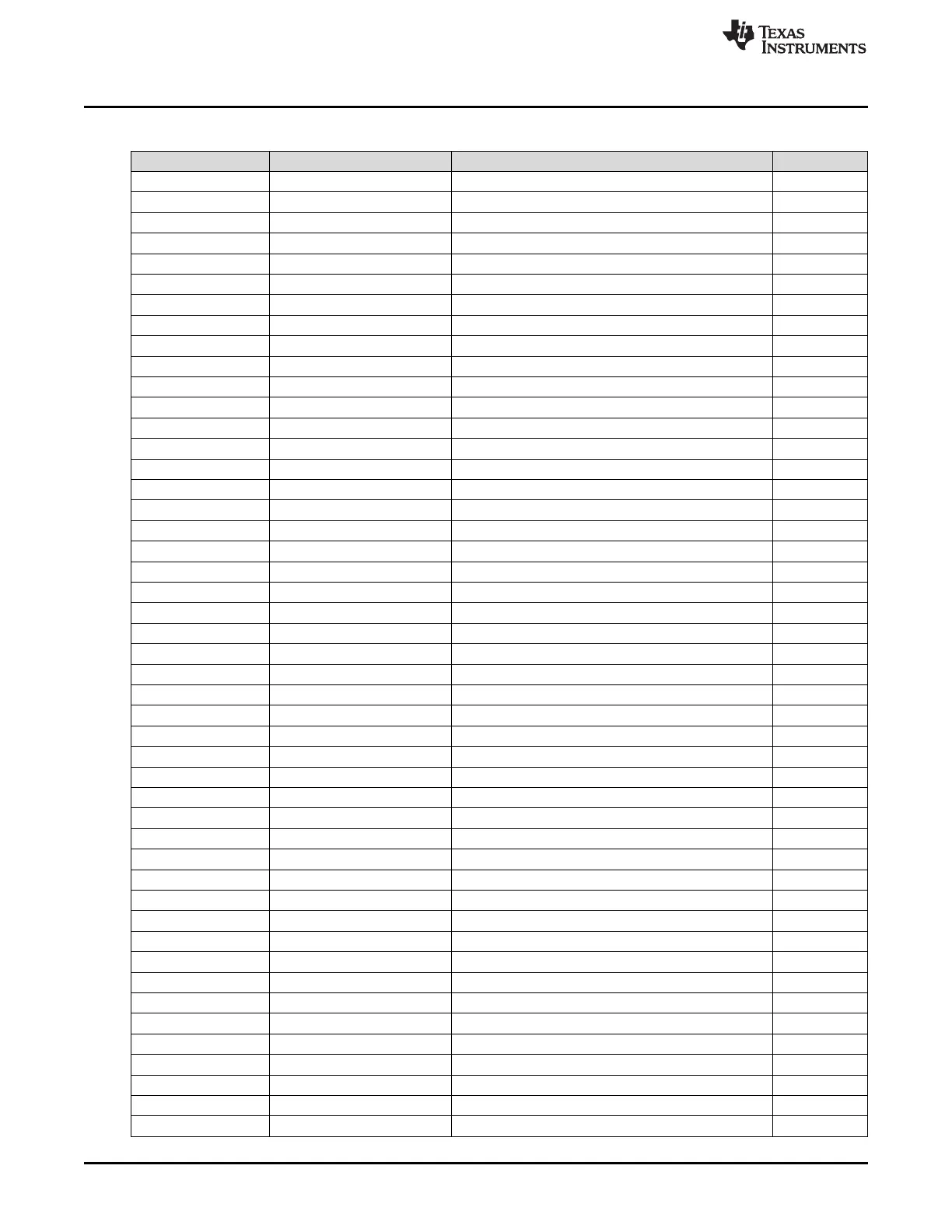

Table 2-10. Cortex

®

-M4 Instruction Summary (continued)

Mnemonic Operands Brief Description Flags

LDRH, LDRHT Rt, [Rn, #offset] Load register with halfword –

LDRSB, LDRSBT Rt, [Rn, #offset] Load register with signed byte –

LDRSH, LDRSHT Rt, [Rn, #offset] Load register with signed halfword –

LDRT Rt, [Rn, #offset] Load register with word –

LSL, LSLS Rd, Rm, <Rs|#n> Logical shift left N,Z,C

LSR, LSRS Rd, Rm, <Rs|#n> Logical shift right N,Z,C

MLA Rd, Rn, Rm, Ra Multiply with accumulate, 32-bit result –

MLS Rd, Rn, Rm, Ra Multiply and subtract, 32-bit result –

MOV, MOVS Rd, Op2 Move N,Z,C

MOV, MOVW Rd, #imm16 Move 16-bit constant N,Z,C

MOVT Rd, #imm16 Move top –

MRS Rd, spec_reg Move from special register to general register –

MSR spec_reg, Rm Move from general register to special register N,Z,C,V

MUL, MULS {Rd,} Rn, Rm Multiply, 32-bit result N,Z

MVN, MVNS Rd, Op2 Move NOT N,Z,C

NOP – No operation –

ORN, ORNS {Rd,} Rn, Op2 Logical OR NOT N,Z,C

ORR, ORRS {Rd,} Rn, Op2 Logical OR N,Z,C

PKHTB, PKHBT {Rd,} Rn, Rm, Op2 Pack halfword –

POP reglist Pop registers from stack –

PUSH reglist Push registers onto stack –

QADD {Rd,} Rn, Rm Saturating add Q

QADD16 {Rd,} Rn, Rm Saturating add 16 –

QADD8 {Rd,} Rn, Rm Saturating add 8 –

QASX {Rd,} Rn, Rm Saturating add and subtract with exchange –

QDADD {Rd,} Rn, Rm Saturating double and add Q

QDSUB {Rd,} Rn, Rm Saturating double and subtract Q

QSAX {Rd,} Rn, Rm Saturating subtract and add with exchange –

QSUB {Rd,} Rn, Rm Saturating subtract Q

QSUB16 {Rd,} Rn, Rm Saturating subtract 16 –

QSUB8 {Rd,} Rn, Rm Saturating subtract 8 –

RBIT Rd, Rn Reverse bits –

REV Rd, Rn Reverse byte order in a word –

REV16 Rd, Rn Reverse byte order in each halfword –

REVSH Rd, Rn Reverse byte order in bottom halfword and sign extend –

ROR, RORS Rd, Rm, <Rs|#n> Rotate right N,Z,C

RRX, RRXS Rd, Rm Rotate right with extend N,Z,C

RSB, RSBS {Rd,} Rn, Op2 Reverse subtract N,Z,C,V

SADD16 {Rd,} Rn, Rm Signed add 16 GE

SADD8 {Rd,} Rn, Rm Signed add 8 GE

SASX {Rd,} Rn, Rm Signed add and subtract with exchange GE

SBC, SBCS {Rd,} Rn, Op2 Subtract with carry N,Z,C,V

SBFX Rd, Rn, #lsb, #width Signed bit field extract –

SDIV {Rd,} Rn, Rm Signed divide –

SEL {Rd,} Rn, Rm Select bytes –

SEV – Send event –

SHADD16 {Rd,} Rn, Rm Signed halving add 16 –

Loading...

Loading...