www.ti.com

Functional Description

73

SWRU543–January 2019

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

Cortex

®

-M4 Processor

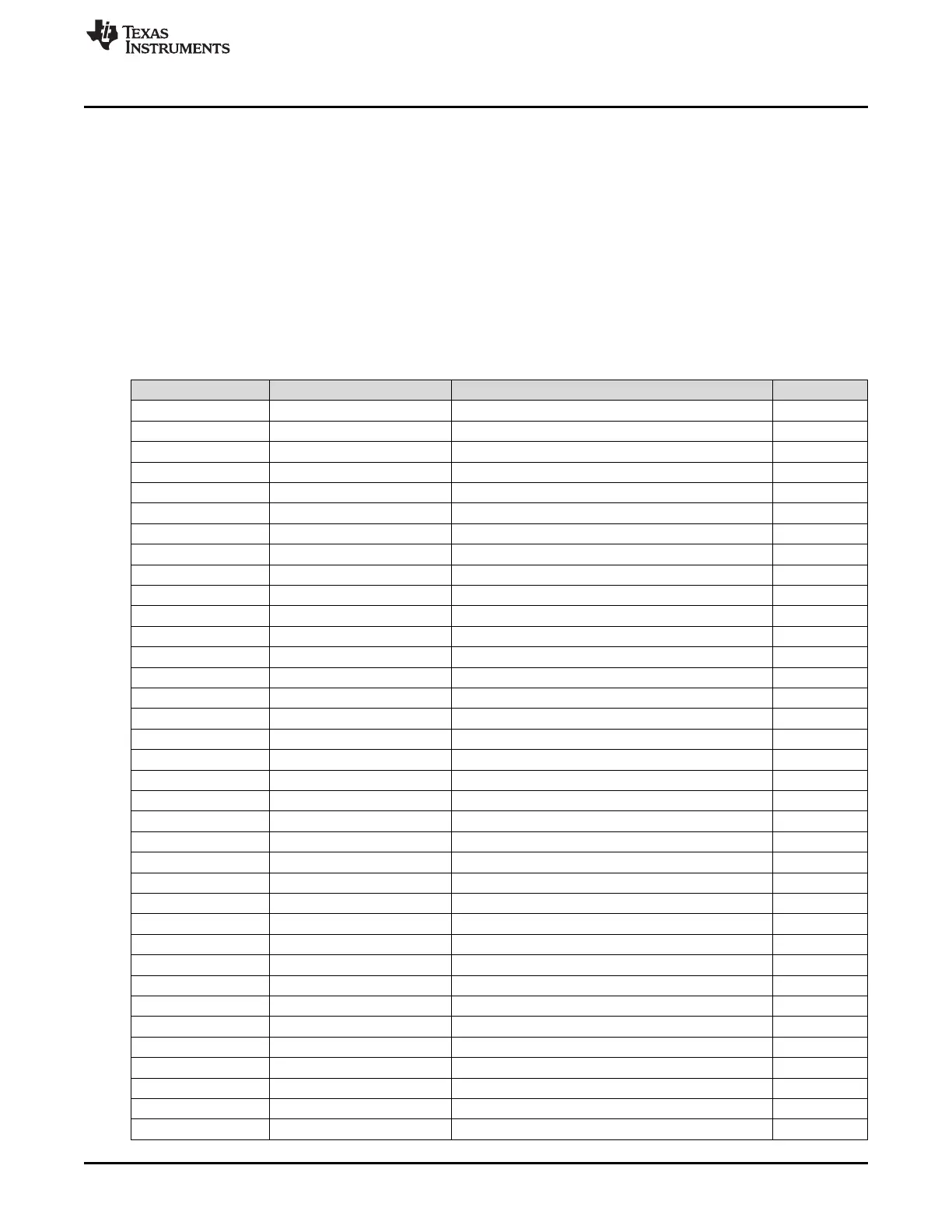

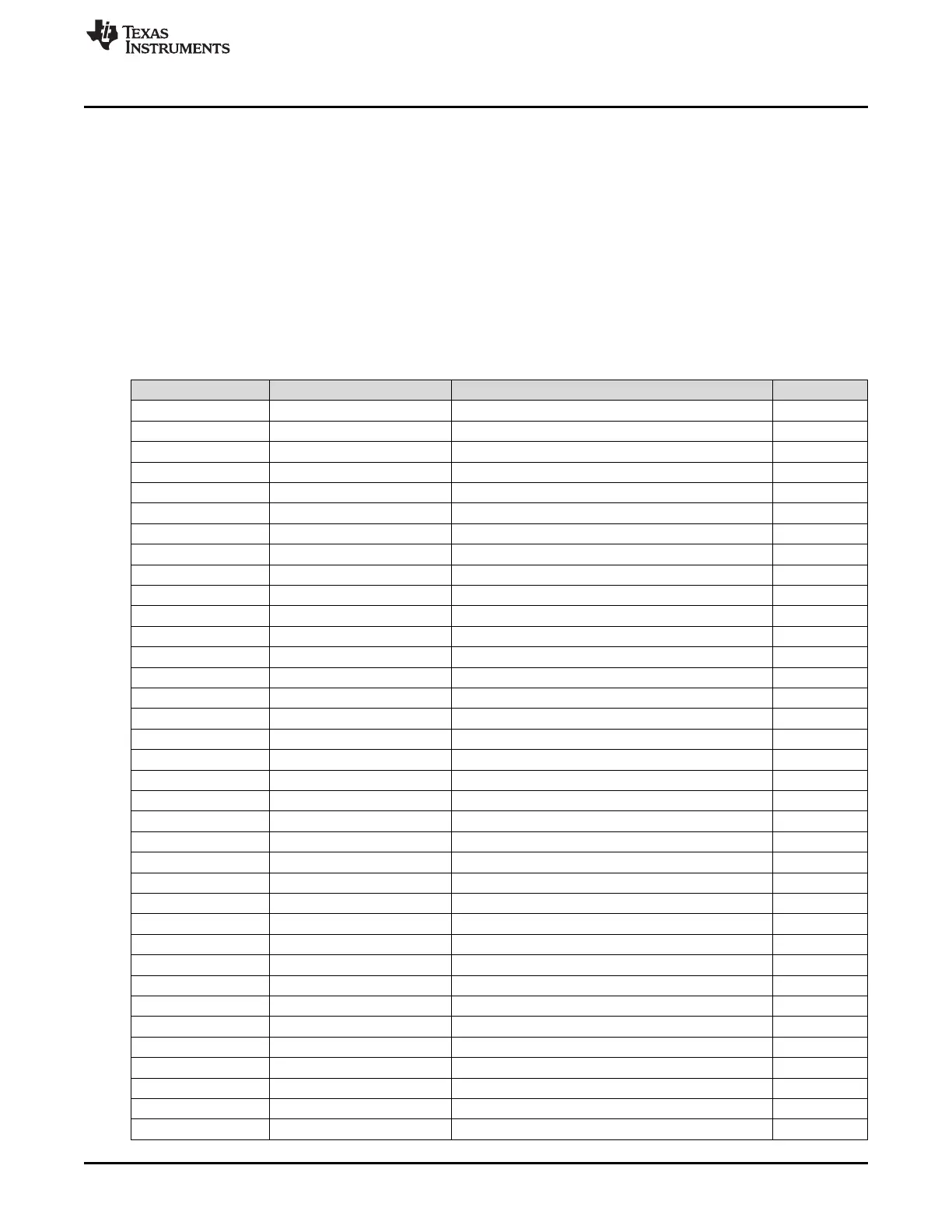

2.2.7 Instruction Set Summary

The processor implements a version of the Thumb instruction set. Table 2-10 lists the supported

instructions.

• < > Angle brackets, enclose alternative forms of the operand.

• { } Braces, enclose optional operands.

• The Operands column is not exhaustive.

• Op2 is a flexible second operand that can be either a register or a constant.

• Most instructions can use an optional condition code suffix.

For more information on the instructions and operands, see the instruction descriptions in the ARM

®

Cortex

®

-M4 Processor Technical Reference Manual.

Table 2-10. Cortex

®

-M4 Instruction Summary

Mnemonic Operands Brief Description Flags

ADC, ADCS {Rd,} Rn, Op2 Add with carry N,Z,C,V

ADD, ADDS {Rd,} Rn, Op2 Add N,Z,C,V

ADD, ADDW {Rd,} Rn , #imm12 Add –

ADR Rd, label Load PC-related address –

AND, ANDS {Rd,} Rn, Op2 Logical AND N,Z,C

ASR, ASRS Rd, Rm, <Rs|#n> Arithmetic shift right N,Z,C

B label Branch –

BFC Rd, #lsb, #width Bit field clear –

BFI Rd, Rn, #lsb, #width Bit field insert –

BIC, BICS {Rd,} Rn, Op2 Bit clear N,Z,C

BKPT #imm Breakpoint –

BL label Branch with link –

BLX Rm Branch indirect with link –

BX Rm Branch indirect –

CBNZ Rn, label Compare and branch if nonzero –

CBZ Rn, label Compare and branch if zero –

CLREX – Clear exclusive –

CLZ Rd, Rm Count leading zeros –

CMN Rn, Op2 Compare negative N,Z,C,V

CMP Rn, Op2 Compare N,Z,C,V

CPSID i Change processor state, disable interrupts –

CPSIE i Change processor state, enable interrupts –

DMB – Data memory barrier –

DSB – Data synchronization barrier –

EOR, EORS {Rd,} Rn, Op2 Exclusive OR N,Z,C

ISB – Instruction synchronization barrier –

IT – If-Then condition block –

LDM Rn{!}, reglist Load multiple registers, increment after –

LDMDB, LDMEA Rn{!}, reglist Load multiple registers, decrement before –

LDMFD, LDMIA Rn{!}, reglist Load multiple registers, increment after –

LDR Rt, [Rn, #offset] Load register with word –

LDRB, LDRBT Rt, [Rn, #offset] Load register with byte –

LDRD Rt, Rt2, [Rn, #offset] Load register with 2 bytes –

LDREX Rt, [Rn, #offset] Load register exclusive –

LDREXB Rt, [Rn] Load register exclusive with byte –

LDREXH Rt, [Rn] Load register exclusive with halfword –

Loading...

Loading...