Real-Time Clock (RTC/API)

MPC5606S Microcontroller Reference Manual, Rev. 7

Freescale Semiconductor 1099

32.6.2 RTC Control Register (RTCC)

The RTCC register contains:

• RTC counter enable

• RTC interrupt enable

• RTC clock source select

• RTC compare value

•API enable

• API interrupt enable

• API compare value

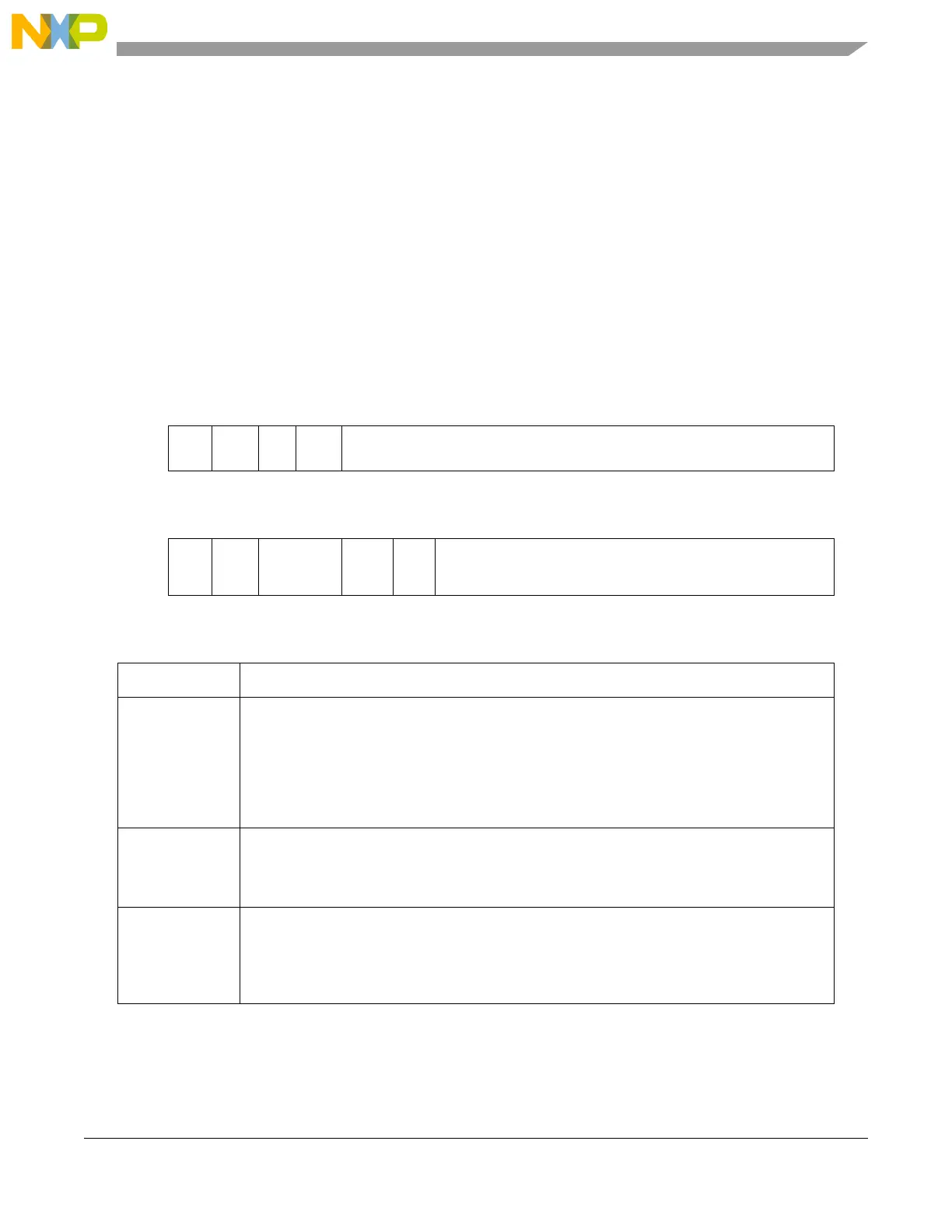

Figure 32-4. RTC Control Register (RTCC)

Offset RTC_BASE + 0x0004 Access: User read/write

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

R CNT

EN

RTCI

E

FRZ

EN

ROVR

EN

RTCVAL

W

POR 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

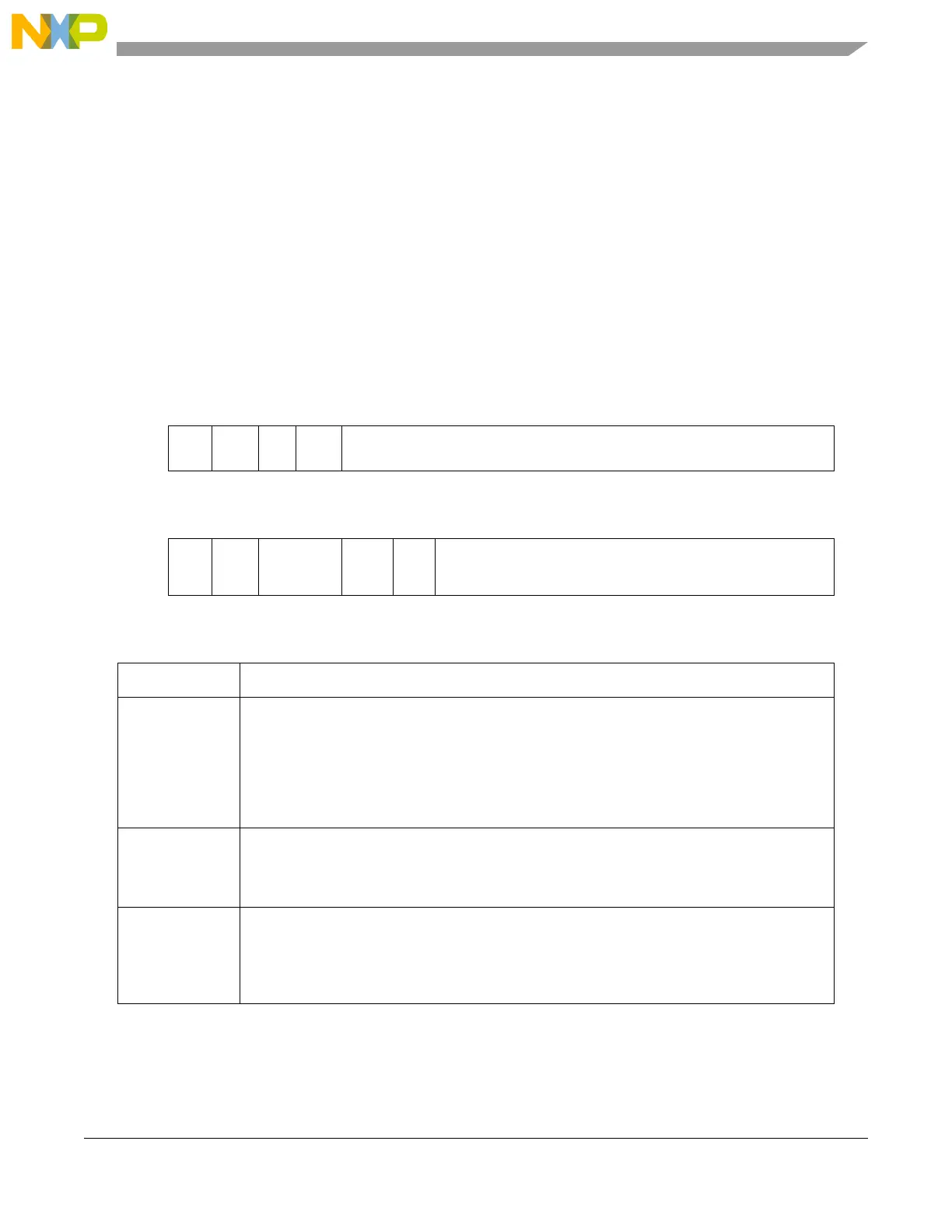

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R API

EN

APIIE CLKSEL DIV51

2

EN

DIV3

2EN

APIVAL

W

POR 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Table 32-2. RTCC field descriptions

Field Description

CNTEN Counter Enable

The CNTEN bit enables the RTC counter. Making CNTEN bit 1’b0 has the effect of

asynchronously resetting (synchronous reset negation) all the RTC logic. This allows for the

RTC configuration and clock source selection to be updated without causing synchronization

issues.

1 Counter enabled

0 Counter disabled

RTCIE RTC Interrupt Enable

The RTCIE bit enables interrupts requests to the system if RTCF is asserted.

1 RTC interrupts enabled

0 RTC interrupts disabled

FRZEN Freeze Enable Bit

The counter freezes when the MCU is stopped by a debugger on the last valid count value if the

FRZEN bit is set. After coming of the debug mode counter starts from the frozen value.

0 Counter does not freeze in debug mode.

1 Counter freezes in debug mode.

Loading...

Loading...