Flash Memory

MPC5606S Microcontroller Reference Manual, Rev. 7

648 Freescale Semiconductor

The contents of the register are loaded from location 0x203E00 of the shadow region in the code flash

(bank0) array at reset. To temporarily change the values of any of the fields in the PFAPR, a write to the

IPS-mapped register is performed. To change the values loaded into the PFAPR at reset, the word location

at address 0x203E00 of the shadow region in the flash array must be programmed using the normal

sequence of operations. The reset value shown in

Figure 17-46 reflects an erased or unprogrammed value

from the shadow region.

17.4.4 Functional description

References to the PFLASH2P_LCA block diagram shown in Figure 17-43 will assist in understanding

much of the discussion in this section.

The PFLASH2P_LCA interfaces between 2 AHB-Lite 2.v6 system bus master ports and three banks of

low-cost flash memory arrays.

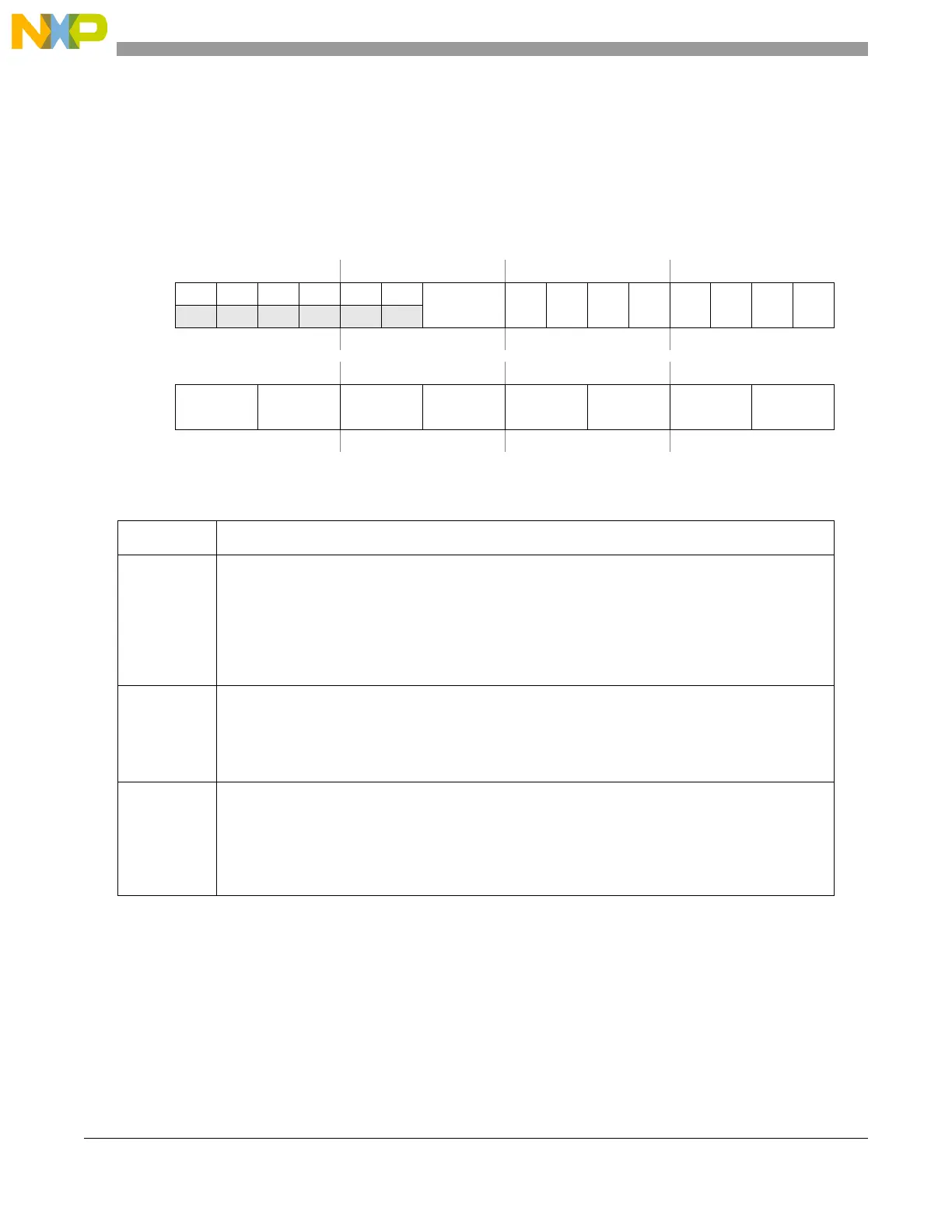

Offset 0x024 Access: Read/write

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

R 0 0 0 0 0 0

ARBM

M7P

FD

M6P

FD

M5P

FD

M4P

FD

M3P

FD

M2P

FD

M1P

FD

M0P

FD

W

Reset * * * * * * 1 1 1 1 1 1 1 1 1 1

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

M7AP M6AP M5AP M4AP M3AP M2AP M1AP M0AP

W

Reset 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

Figure 17-46. PFLASH Access Protection Register (PFAPR)

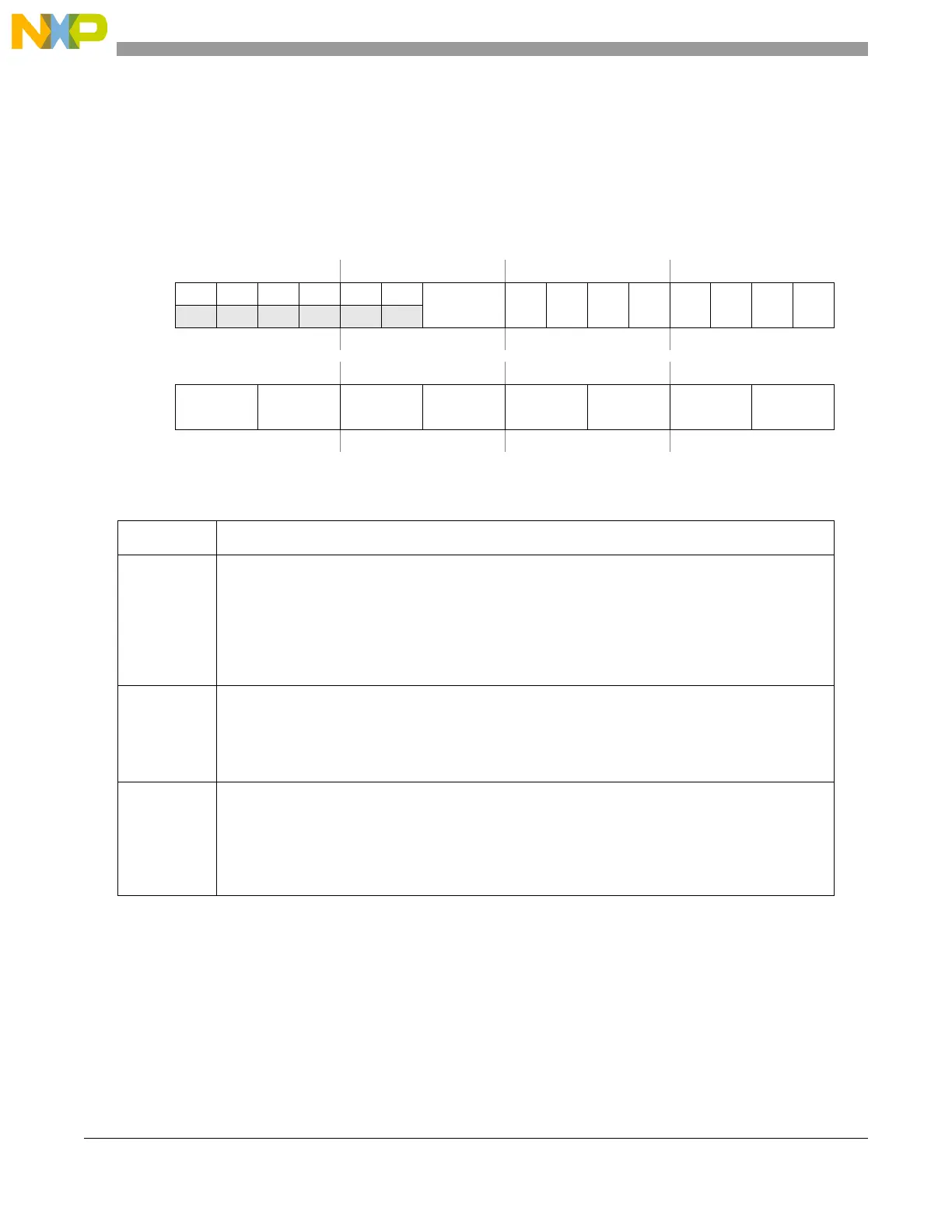

Table 17-66. PFLASH Access Protection Register field descriptions

Field Description

ARBM Arbitration mode. This 2-bit field controls the arbitration for PFLASH controllers supporting 2 AHB

ports. The port arbitration mode is used only when accesses from the 2 AHB ports attempt to

simultaneously reference the same flash bank. Simultaneous references to different memory banks

are processed concurrently.

00 Fixed priority arbitration with AHB p0 > p1

01 Fixed priority arbitration with AHB p1 > p0

1- Round-robin arbitration

MxPFD Master x Prefetch Disable (x = 0,1,2,...,7). These bits control whether prefetching may be triggered

based on the master number of the requesting AHB master. This field is further qualified by the

PFCRn[B02_Px_DPFE, B02_Px_IPFE, Bx_Py_BFE] bits.

0 Prefetching may be triggered by this master

1 No prefetching may be triggered by this master

MxAP Master x Access Protection (x = 0,1,2,...,7). These fields control whether read and write accesses

to the flash are allowed based on the master number of the initiating module.

00 No accesses may be performed by this master

01 Only read accesses may be performed by this master

10 Only write accesses may be performed by this master

11 Both read and write accesses may be performed by this master

Loading...

Loading...