Interrupt Controller (INTC)

MPC5606S Microcontroller Reference Manual, Rev. 7

780 Freescale Semiconductor

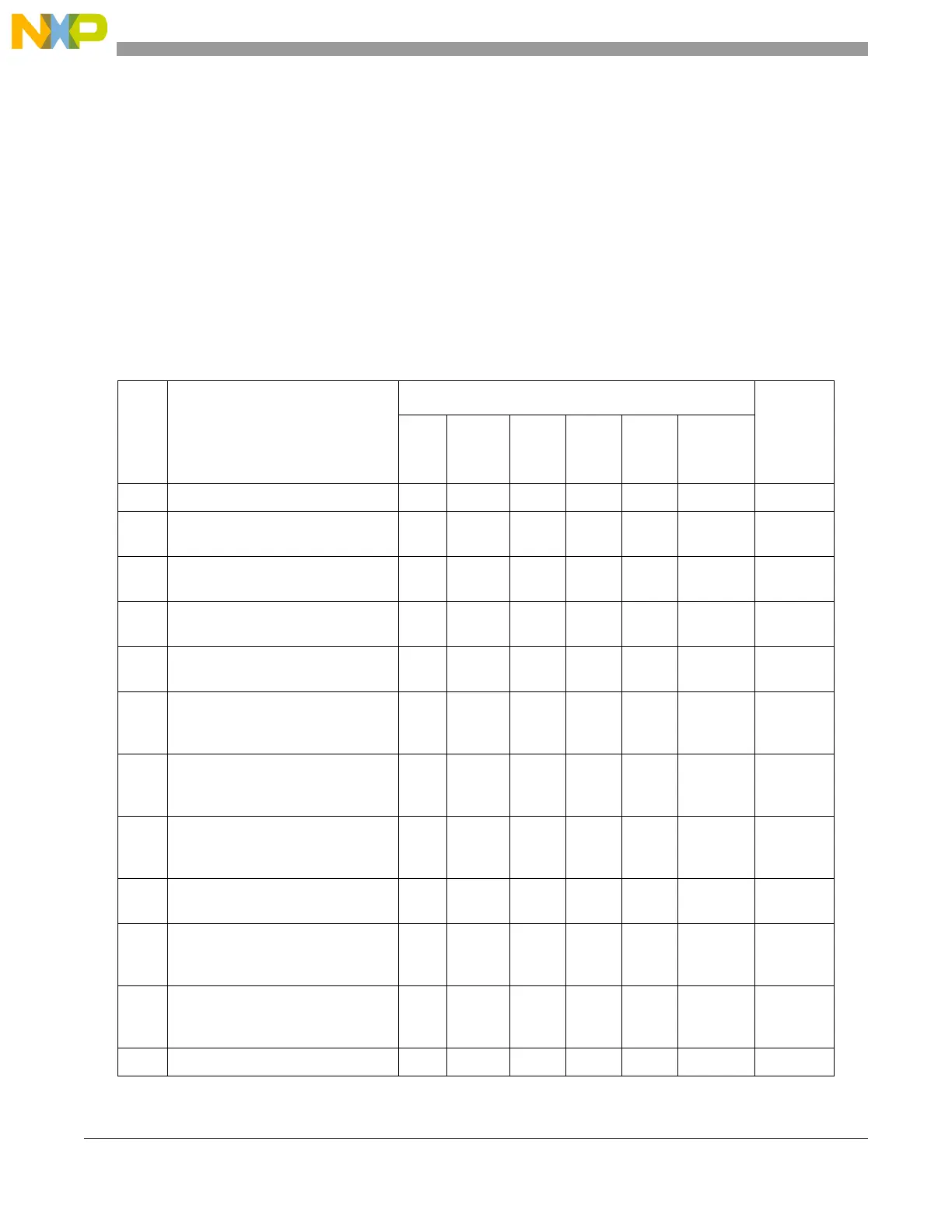

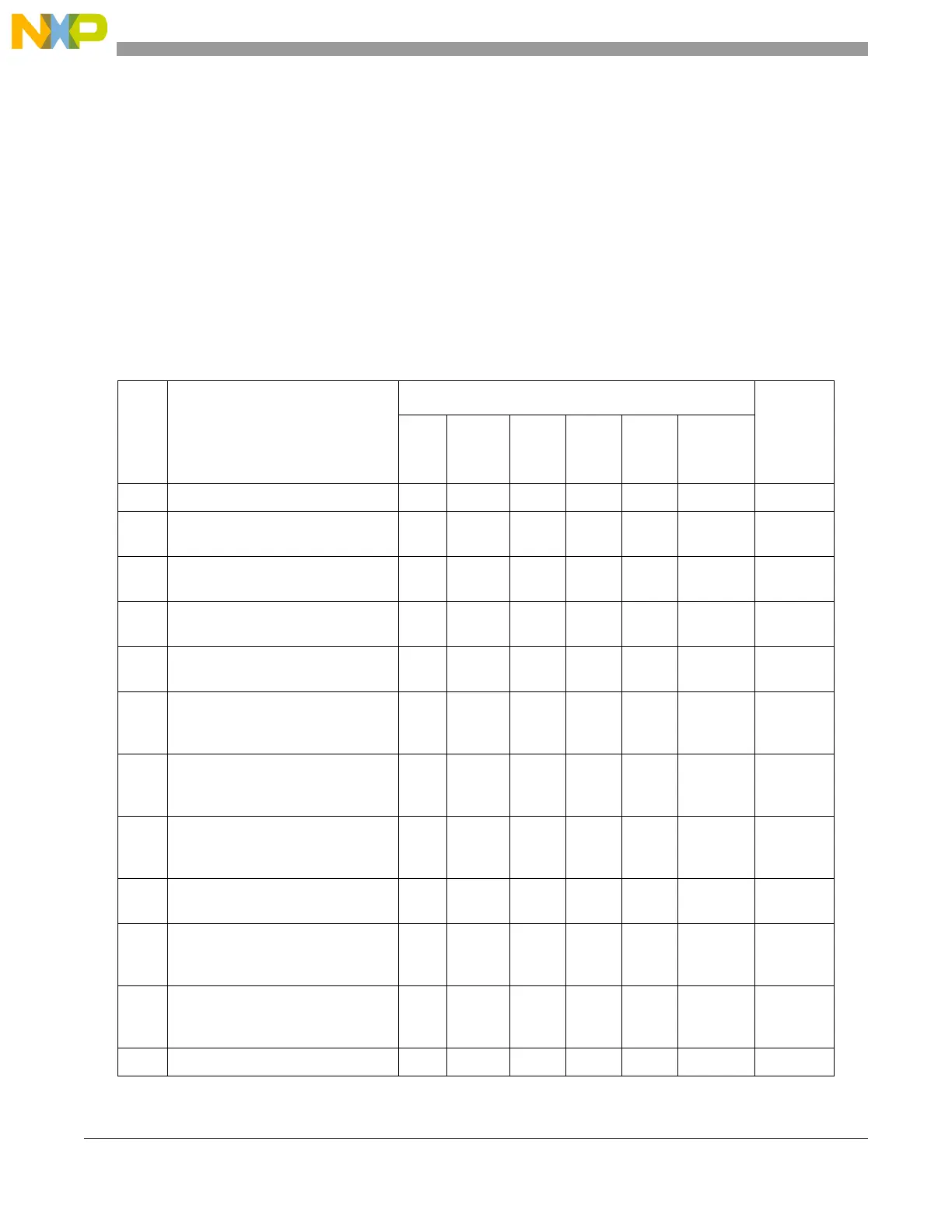

21.7.4 Order of execution

An ISR with a higher priority can preempt an ISR with a lower priority, regardless of the unique vectors

associated with each of their peripheral or software configurable interrupt requests. However, if multiple

peripheral or software configurable interrupt requests are asserted, more than one has the highest priority,

and that priority is high enough to cause preemption, the INTC selects the one with the lowest unique

vector regardless of the order in time that they asserted. However, the ability to meet deadlines with this

scheduling scheme is no less than if the ISRs execute in the time order that their peripheral or software

configurable interrupt requests asserted.

The example in Table 21-11 shows the order of execution of both ISRs with different priorities and the

same priority

Table 21-11. Order of ISR execution example

Step Step description

Code executing at end of step

PRI in

INTC_CPR

at end of

step

RTOS ISR108

1

ISR208 ISR308 ISR408

Interrupt

exception

handler

1 RTOS at priority 0 is executing. X 0

2 Peripheral interrupt request 100 at

priority 1 asserts. Interrupt taken.

X 1

3 Peripheral interrupt request 400 at

priority 4 is asserts. Interrupt taken.

X 4

4 Peripheral interrupt request 300 at

priority 3 is asserts.

X 4

5 Peripheral interrupt request 200 at

priority 3 is asserts.

X 4

6 ISR408 completes. Interrupt

exception handler writes to

INTC_EOIR.

X 1

7 Interrupt taken. ISR208 starts to

execute, even though peripheral

interrupt request 300 asserted first.

X 3

8 ISR208 completes. Interrupt

exception handler writes to

INTC_EOIR.

X 1

9 Interrupt taken. ISR308 starts to

execute.

X 3

10 ISR308 completes. Interrupt

exception handler writes to

INTC_EOIR.

X 1

11 ISR108 completes. Interrupt

exception handler writes to

INTC_EOIR.

X 0

12 RTOS continues execution. X 0

Loading...

Loading...